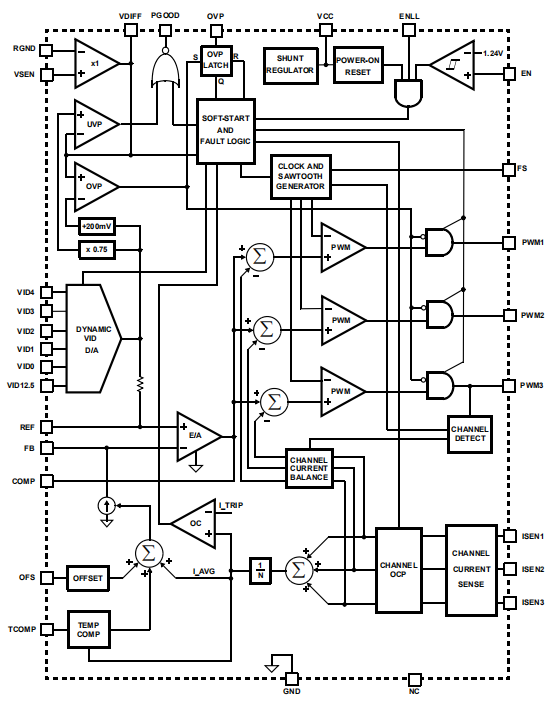

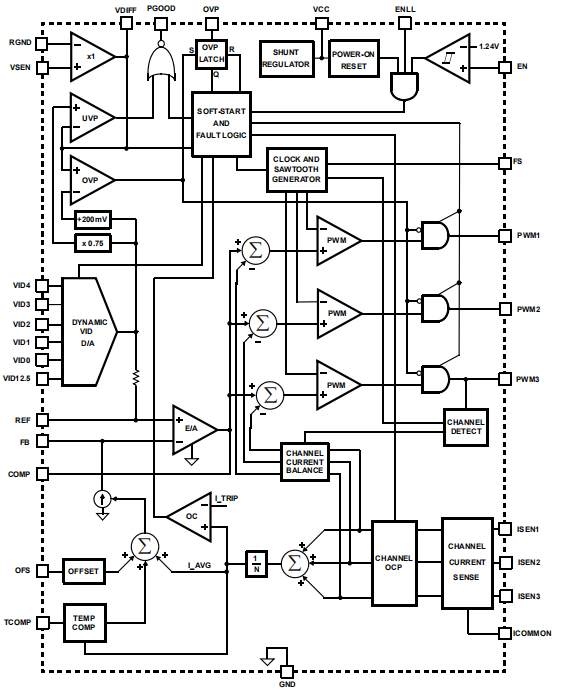

ISL6565A、ISL6565B控制微处理器核心驱动高达3个同步整流的电压调节并联降压通道。多相buck变换器体系结构使用交织定时来倍增信道纹波频率和减少输入和输出纹波电流。ISL6565A和ISL6565B之间的区别是ISL6565A利用无线电数据系统(开启)电流感应,而ISL6565B对每个相位使用DCR电流感应。电流传感的这些节省成本和空间的方法用于自适应电压定位(下垂)、通道电流平衡和过电流保护。以确保速降精度,可编程内部温度补偿功能用于补偿rDS(ON)和DCR温度灵敏度的影响。提供一个单位增益差分放大器,用于遥控电压感应。遥控器之间的任何电位差用遥控器消除了当地的干扰放大器。精度阈值敏感启用输入为可用于精确协调ISL6565A、ISL6565B,带Intersil MOSFET驱动芯片。动态视频8482; 技术允许无缝实时视频变化。偏移管脚允许精确的电压偏移独立于视频设置的设置

特征

多相功率转换-2或3相操作

精确的核心电压调节-差分遥感电压-0.5%系统精度超过温度和寿命-可调参考电压偏移

精确的rDS(开)或DCR电流感应-集成可编程温度补偿-精确的负荷线编程-精确的通道电流平衡-低成本、无损电流传感

输入电压:12V或5V偏置

微处理器电压识别输入-动态VID®技术-6位视频输入-0.8375V至1.600V,步进12.5mV

用于精确排序的阈值启用功能

过电流保护

过电压保护

数字软启动

每相工作频率高达1.5MHz

QFN包-符合JEDEC PUB95 MO-220QFN-四平面无引线-封装外形-接近芯片规模的封装,提高了印刷电路板效率,外形更薄

无铅可用

绝对最大额定值

电源电压,VCC。+7伏

输入、输出或I/O电压(OVP除外)。接地-0.3V至VCC+0.3V

过电压。+15伏

人体模型。>4千伏

ESD(机器型号)。>300伏

ESD(充电装置型号)。>2千伏

操作条件

电源电压,VCC(5V偏置模式)。+5V±5%

结温。0°C至125°C

热信息

热阻θJA(℃/W)θJC(℃/W)

SOIC封装(注1)。62不适用

QFN包(注2、3)。33 3.5条

TSSOP包(注1)。85牛刀

最高结温。150摄氏度

最高储存温度范围。-65°C至150°C

最高引线温度(焊接10s)。300摄氏度(SOIC-仅限铅头)

注意:超过“绝对最大额定值”中列出的应力可能会对设备造成永久性损坏。这是一个压力等级和操作

在本规范操作章节中所述的上述条件或任何其他条件下的装置并不隐含。

笔记:

1.θJA是用安装在自由空气中的高效热导率测试板上的元件测量的。详见技术简报TB379。

2.θJA是在自由空气中测量的,该部件安装在具有“直接连接”特性的高效热导率测试板上。见技术简报TB379。

3.对于θJC,“外壳温度”位置是包装底部外露金属垫的中心。

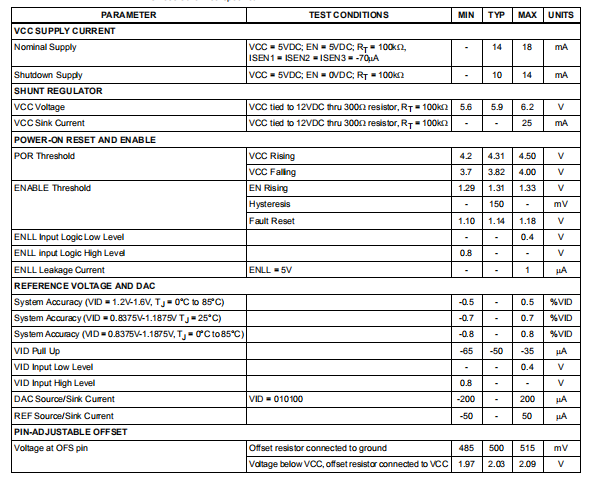

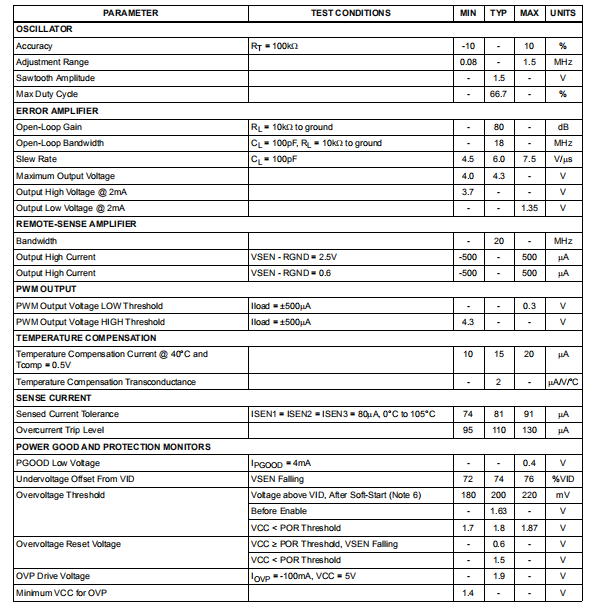

电气规范工作条件:VCC=5V或ICC<25mA(注3),TJ=0°C至105°C。除非另有规定。

电气规范工作条件:VCC=5V或ICC<25mA(注3),TJ=0°C至105°C。除非另有规定。(续)

笔记:

4.当使用内部分路调节器时,VCC被夹紧至6.02V(最大值)。电流必须限制在25毫安或以下。

5.这些部分的设计和调整精度与所有误差的电压环包括在内。

6.软启动时,VDAC从0上升到VID。过电压跳闸等级为1.7V和VDAC+0.2V。

功能管脚说明

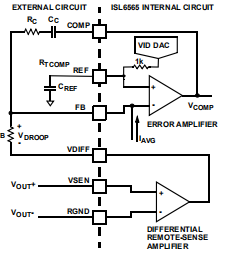

VCC-提供操作芯片所需的所有电源。当这个引脚上的电压超过上升的POR阈值,并在该引脚上的电压降到下降的POR阈值以下。将此引脚直接连接到+5V电源或通过一系列300Ω电阻至+12V电源。GND—集成电路的偏置和参考接地。EN-此引脚是控制器。通过适当的电阻分压器提供同步的方法控制器和MOSFET驱动芯片的通电。当EN电压高于1.31V时,ISL6565A、ISL6565B根据ENLL、内部POR和挂起的故障状态。在低于1.14V的电压下行驶,将清除所有故障故障状态并启动ISL6565A、ISL6565B至软启动重新启用时。ENLL—该引脚是控制器。当断言为逻辑高时,ISL6565是根据EN、内部POR、VID的状态激活输入和未决故障状态。解除资产负债所有故障状态,并在重新启用时将ISL6565A、ISL6565B启动为软启动。FS-一个电阻,从FS到地,将设置开关频率。有关正确的电阻器,请参考公式45计算。视频4、视频3、视频2、视频1、视频0和视频12.5-这些是提供参考的内部DAC的输入输出调节电压。将这些插脚连接到带或不带外部上拉电阻器的开漏输出或激活上拉输出。VID4-VID12.5有20微安当电压高于逻辑高电平。VDIFF、VSEN和RGND-VSEN和RGND是精密差分遥感放大器。这个放大器转换遥控器的差动电压输出到参考本地接地的单端电压。VDIFF是放大器的输出和调节器的输入以及保护电路。将VSEN和RGND连接到检测远程负载的管脚。FB和COMP-误差的输入和输出反转分别放大。FB通过电阻器。负电流,与输出电流成比例出现在FB引脚上。适当大小的电阻器VDIFF和FB设置负载线(下垂)。下垂刻度因子由ISEN电阻和较低电阻的比率设置MOSFET rDS(ON)或电感DCR。COMP被绑定到FB通过外部R-C网络补偿

REF-REF输入引脚是错误的正输入安培。它通过1kΩ电阻器。在参考引脚和在动态过程中接地以平滑电压过渡视频™ 操作。TCOMP-温度补偿缩放输入。一个从该引脚到接地的电阻设置内部感温电路。由控制器用于将下垂电流输出修改为FB引脚,用于调节MOSFET rDS(ON)和电感DCR随温度变化。PWM1,PWM2,PWM3—脉冲宽度调制输出。将这些引脚连接到Intersil的PWM输入引脚驾驶员集成电路。活动通道的数量由PWM3的状态。将PWM3连接到VCC,以配置两相运行。ISEN1、ISEN2、ISEN3、ICOMON(仅限ISL6565B)-这些引脚用于感应单个相位输出海流。感应电流用于通道平衡,保护和负载线调节。ISEN3应该留下打开进行2相操作。对于使用ISL6565A的无线电数据系统(开启)电流感应,连接ISEN1、ISEN2和ISEN3引脚之间的电阻器它们各自的相位节点。这个电阻设置一个电流与下部MOSFET中的电流成比例传导间隔。对于使用ISL6565B的DCR感应,连接一个电阻器从VCORE到icomon pin。然后连接ISEN1,ISEN2和ISEN3指向RC sense之间的节点各相电感周围的元件。PGOOD-PGOOD用作结束软启动。它是一个漏极逻辑输出,很低阻抗直到软启动完成。它会被拉一旦达到欠压点,再次降低。OFS-OFS引脚提供了一种对dc编程的方法通过下垂产生偏移电压的电流FB和VDIFF之间的电阻器。偏移电流为由外部电阻和内部精密电阻产生电压基准。偏移的极性由将电阻器连接到GND或VCC。如果没有偏移OFS引脚应保持未连接状态。过电压保护引脚。这是一条明渠设备,可以在外部配置一个电阻器控制可控硅关闭调节器

操作

多相功率转换

微处理器负载电流配置文件已更改为指出多相功率变换的优点是不可能忽视的。技术挑战与生产单相转换器有关成本效益和热可行性都迫使转变为多阶段的成本节约方法。这个ISL6565A、ISL6565B控制器有助于简化通过集成重要功能和要求来实现最小输出组件。第2页的框图和3提供多相电源的顶层视图使用ISL6565A和ISL6565B控制器进行转换。

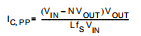

多相转换器中每个通道的切换是彼此对称失相频道。在三相转换器中,每个通道开关1/3在前一个通道后循环,在跟踪频道。因此,三相转换器组合纹波频率比任何一相的纹波频率。此外,组合电感电流的峰-峰振幅减小与相数成比例(方程式1和2)。纹波频率增加,纹波幅度降低设计人员可以使用更少的每通道电感和降低任何性能的总输出电容规范。图1说明了输出纹波的乘法效应频率。三通道电流(IL1、IL2和IL3)合并形成交流纹波电流和直流负载当前。波纹分量的波纹是每个通道电流的频率。每个脉冲宽度调制脉冲在上一阶段。每相的峰间电流为大约7A,电感电流的直流分量联合收割机输送货物。为了了解波纹电流振幅在多相电路,检查表示单个通道的峰-峰电感电流。

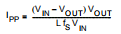

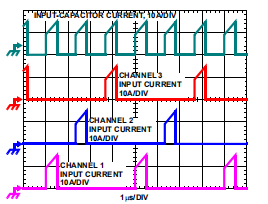

在等式1中,VIN和VOUT是输入和输出电压,L为单通道电感值,fS是开关频率。输出电容器传导电感电流。在多相转换器的情况下电容电流是每个个别频道的。将方程式1与求和后峰间电流的表达式N对称相移电感电流方程2。峰间纹波电流减小与通道数成比例的量。输出电压纹波是电容、电容的函数等效串联电阻(ESR)和电感纹波当前。降低电感纹波电流允许设计师使用较少或较便宜的输出电容器。

交错的另一个好处是减少输入纹波当前。输入电容部分由最大输入纹波电流。多相拓扑可以通过降低输入纹波提高整体系统成本和规模使设计师能够降低投入成本电容。图2中的示例演示了输入三相变流器的电流总输入纹波电流。图2所示的转换器向36A负载提供1.5V电压从12V输入。有效值输入电容电流为5.9A。将其与同样降压的单相转换器进行比较=36A时为12V至1.5V。单相转换器有11.9A有效值输入电容电流。单相变流器必须使用有效值电流两倍的输入电容器组、容量相当于三相变流器。

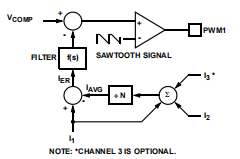

标题为“输入电容器”一节中的图19和20选择可用于确定输入电容器RMS基于负载电流、占空比和频道。在确定最佳输入电容解决方案。脉宽调制操作每个变流器支路的定时由活动频道。的默认频道设置ISL6565A,ISL6565B是3。定义了一个开关周期作为PWM1脉冲终止信号之间的时间。这个脉冲终止信号是内部产生的时钟触发PWM1下降沿的信号。周期时间脉冲终止信号是开关的倒数由FS引脚和之间的电阻器设置的频率地面。当时钟信号指令时,每个周期开始PWM1变低。PWM1转换向信道1发送信号关闭通道1上部MOSFET的MOSFET驱动器打开通道1同步MOSFET。在默认信道配置,PWM2脉冲终止PWM1脉冲后一个周期的1/3。PWM3脉冲在PWM2之后终止一个周期的1/3。如果PWM3连接到VCC,双通道操作选择后,PWM2脉冲终止1/2个周期PWM1脉冲终止。一旦一个脉宽调制脉冲转换低,它将保持低最少1/3个周期。强制关闭时间要求确保电流样本准确。电流感应是在下一节中描述。在强制关闭时间之后到期时,将启用脉宽调制输出。脉宽调制输出状态由误差放大器输出信号的位置驱动,VCOMP,减去相对于锯齿形坡道如图6所示。当修改VCOMP电压穿过锯齿形斜坡,PWM输出高度转换。MOSFET驱动器检测到脉宽调制信号的状态并关闭同步打开上面的MOSFET。脉宽调制信号在脉冲终止信号标记通过触发低脉冲宽度调制信号开始下一个周期。

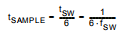

电流采样

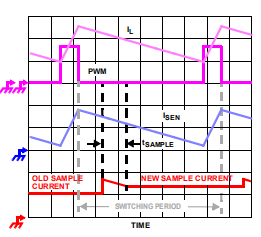

在强制关闭时间内,经过低电压脉冲宽度调制转换,电流检测放大器使用ISEN输入再现与电感电流成比例的信号。无论采用哪种当前的感知方法感应电流(ISEN)只是电感电流。示例窗口正好打开开关周期,tSW,在PWM转换低之后。这个然后,示例窗口将在固定时间内保持打开状态,t取样,等于开关周期的1/6,tSW为如图3所示。

采样电流在采样结束时为与电感电流成比例,并保持到下一个切换周期样本。采样电流用于电流平衡、负载线调节和过电流保护。

电流传感

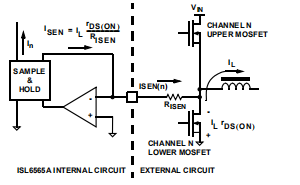

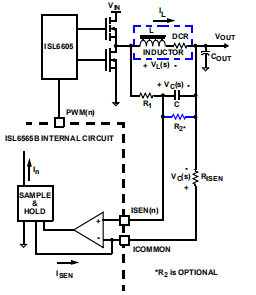

ISL6565A支持MOSFET rDS(ON)电流感应,而ISL6565B支持电感DCR电流感应。图4和5所示的内部电路表示n通道转换器的n通道。这个电路是对转换器中的每个通道重复,但不能根据PWM3引脚的状态激活,如在“脉宽调制操作”一节中介绍。MOSFET rDS(ON)感应(仅限ISL6565A)ISL6565A通过采样检测信道负载电流下MOSFET rDS(ON)上的电压,如图4。一个接地参考运算放大器,内部到ISL6565A,通过电阻,上升。上升的电压相当于下MOSFET的rDS(ON)上的电压降当它在指挥的时候。产生的电流进入ISEN引脚与通道电流成正比。伊森海流是按照当前采样中的描述进行采样和保持章节。从图4中可以看出,In的以下公式是其中IL是通道电流。

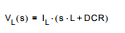

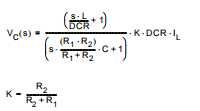

感应器DCR感应(仅限ISL6565B)电感绕组具有分布的特性电阻或DCR(直流电阻)。为了简单地说,电感DCR被认为是一个独立的集中数量,如图5所示。通道电流IL流过感应器,通过DCR。方程5显示了s域等效电压,VL,穿过感应器。

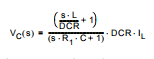

一个简单的R-C网络,跨越感应器(R1和C)提取DCR电压,如图5所示。电压通过传感电容器,VC,可以显示为与通道电流IL成比例,如等式6所示

在某些情况下,可能需要使用电阻分压器R-C网络通过感应器感应电流。这个可以通过放置第二个电阻R2,穿过传感电容器。在这些情况下,电压通过传感电容,VC,与通道电流IL和电阻分压比K。

如果选择了R-C网络组件,则RC时间常数与电感L/DCR时间匹配常数,则VC等于DCR乘以电阻分压器的比率,K。如果电阻分压器未使用,K的值为1。

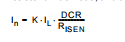

电容电压VC,然后在感应电阻上升。监管者应该只有一个从VOUT平面连接到IComon别针。通过上升的电流与电感电流。公式9表明通道电流和感应电流(ISEN)之间由选择的感测电阻器的值驱动电阻分压比,电感的DCR。

通道电流平衡来自每个有源信道的采样电流,In总和除以活动的数量频道。产生的循环平均电流,IAVG,提供对每个开关周期的转换器。通道电流通过比较每个通道的循环平均电流,并使根据错误。Intersil的专利电流平衡法在图6中,表示通道1的误差校正。在图中,循环平均电流与通道1采样,I1,创建错误信号IER滤波后的误差信号改变脉冲宽度由VCOMP命令纠正任何不平衡和力更接近于零。误差信号的同一方法校正应用于每个活动通道。

通道电流平衡是实现热平衡的关键多相操作的优点。产生的热量转换在多个设备和一个大的区域。设计人员避免了驱动多个平行mosfet,以及使用散热器和非标准磁性材料。电压调节集成补偿网络如图7所示确保输出电压的稳态误差为仅限于参考电压的误差(输出和OFS电流源的偏移误差,遥测和误差放大器。Intersil指定ISL6565A、ISL6565B的保证公差包括这些元素的组合公差。误差放大器VCOMP的输出与产生脉冲宽度调制信号的锯齿波。脉冲宽度调制信号控制内部MOSFET驱动器和将转换器输出调节到指定的参考值电压。控制的内部和外部电路电压调节如图7所示。ISL6565在反馈路径中集成了一个内部差分远程感测放大器。放大器移除测量输出时遇到的电压误差相对于控制器接地参考点的电压从而获得更精确的感应输出方法电压。将微处理器检测引脚连接到遥控放大器。远程感应输出,VDIFF,是通过外部电阻。

数模转换器(DAC)产生参考信号基于引脚VID4上逻辑信号状态的电压通过第12.5节。DAC解码6位逻辑信号(VID)进入表1所示的一个离散电压。每个VID输入提供20微安的上拉至内部2.5V用于开漏输出的电源。上拉电流在逻辑阈值以上递减为零以保护电压敏感输出装置。外部上拉电阻器能在漏电时增大上拉电流源进入驱动装置的电流大于20微安。