ADS1231点击型号即可查看芯片规格书

特征

•桥梁传感器的完整前端

•内部放大器,增益128

•内部振荡器

•电桥传感器低压侧电源开关

•低噪声:35nVrms

•可选数据速率:10SPS或80SPS

•同时抑制50赫兹和60赫兹10SPS

•输入电磁干扰滤波器

•用于比率测量的外部电压参考高达5V

•简单的销驱动控制

•二线串行数字接口

•供电范围:3V至5.3V

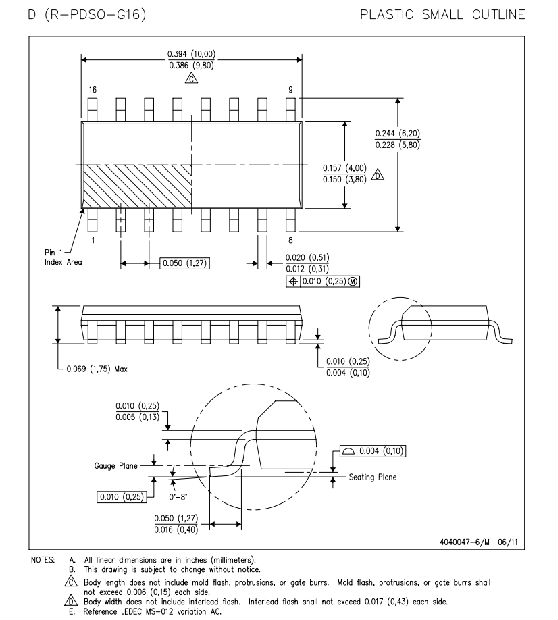

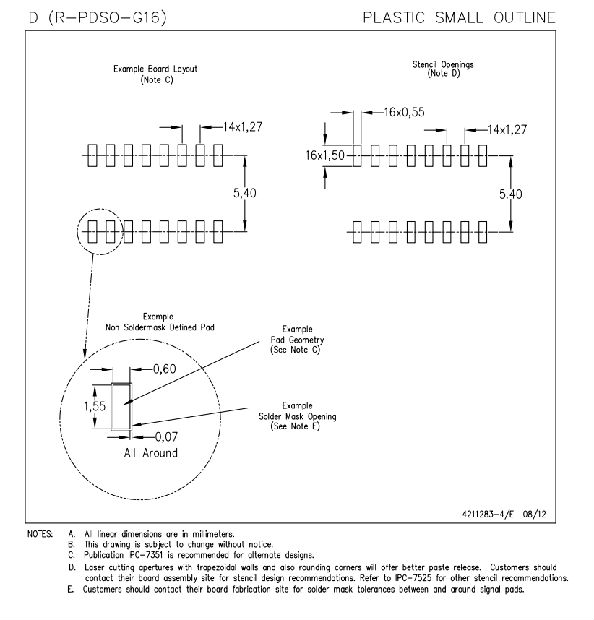

•包装:SOIC-16

•温度范围:–40°C至+85°C

应用

•磅秤

•应变计

•称重传感器

•工业过程控制

说明

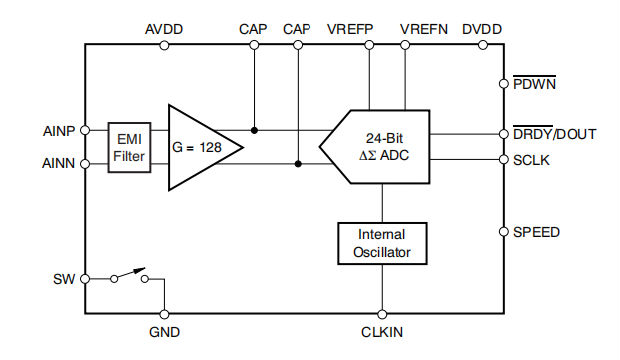

ADS1231是一种精密的24位模数转换器(ADC)。ADS1231具有板载低噪声放大器、板载振荡器、精密三阶24位δ∑(Δ∑)调制器和电桥电源开关,为电桥传感器应用(包括称重仪、应变计和称重传感器)提供了完整的前端解决方案。

低噪声放大器的增益为128,支持±19.5mV的全刻度差分输入。Δ∑ADC具有24位分辨率,由三阶调制器和四阶数字滤波器组成。支持两种数据速率:10SPS(同时抑制50赫兹和60赫兹)和80SPS。ADS1231可以处于低功耗待机模式,也可以在关机模式下完全关闭。

ADS1231由专用管脚控制;没有可编程的数字寄存器。数据通过一个容易隔离的串行接口输出,该接口直接连接到MSP430和其他微控制器。

ADS1231采用SO-16封装,温度范围为-40°C至+85°C。

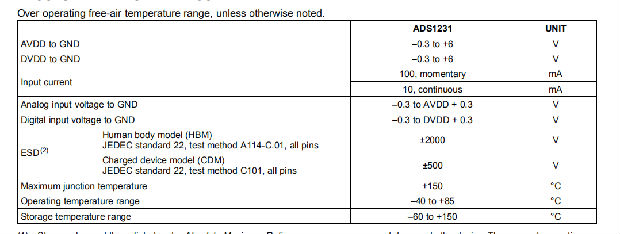

绝对最大额定值

超出工作自由空气温度范围,除非另有说明。

(1)、超过绝对最大额定值的应力可能会对设备造成永久性损坏。这些仅为应力额定值,不暗示设备在这些或任何其他条件下的功能运行。长期暴露在绝对最大额定条件下可能会影响设备的可靠性。

(2)、注意:ESD敏感装置。搬运设备时应采取预防措施,以防止永久损坏。

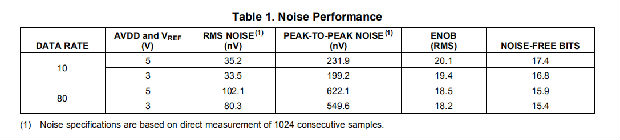

噪声性能

ADS1231具有出色的噪声性能。表1总结了输入端对不同数据速率和电压参考值外部短路时的典型噪声性能。

均方根和峰-峰噪声指的是输入。有效位数(ENOB)定义为:ENOB=ln(FSR/RMS噪声)/ln(2)

无噪声位定义为:无噪声位=ln(FSR/峰间噪声)/ln(2)

式中:FSR(满标度范围)=VREF/增益。

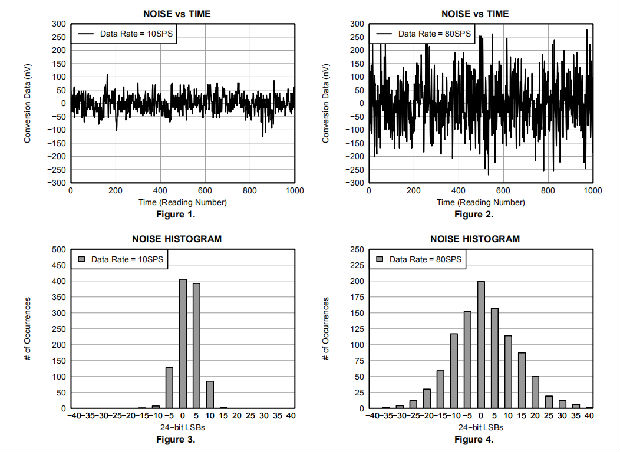

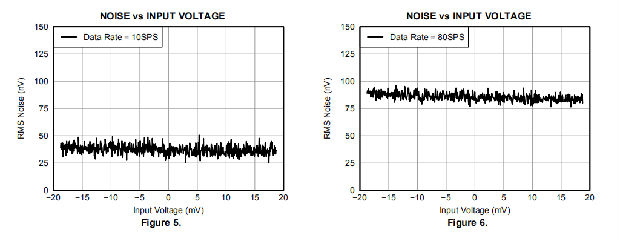

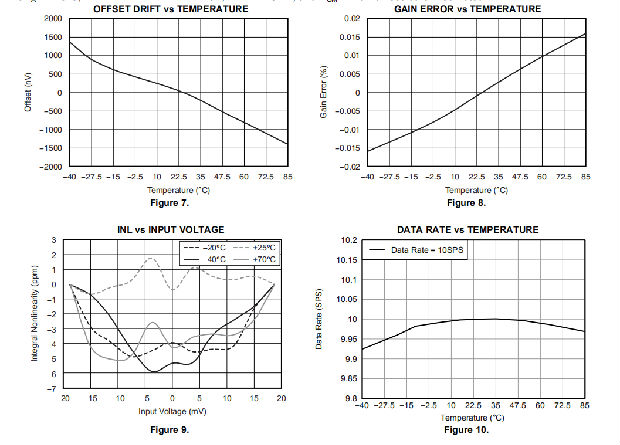

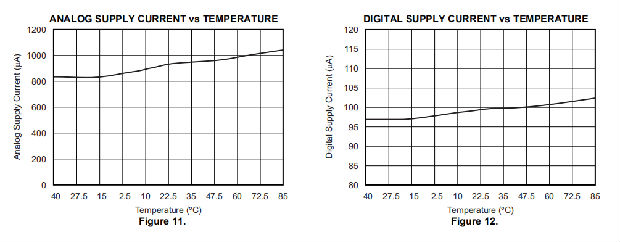

典型特征

在TA=+25°C时,AVDD=DVDD=REFP=5V,REFN=GND,VCM=2.5V,除非另有说明。

概述

ADS1231是一种精密的24位ADC,包括低噪声PGA、内部振荡器、三阶deltasigma(Δ∑)调制器和四阶数字滤波器。ADS1231为桥梁传感器应用提供了一个完整的前端解决方案,如称重仪、应变仪和压力传感器。

数据可以在10SPS下输出,以获得卓越的50赫兹和60赫兹抑制,或者在需要更高速度时以80SPS输出。ADS1231易于配置,所有数字控制都是通过专用管脚完成的;没有寄存器可编程。一个简单的二线串行接口检索数据。

模拟输入(AINP,AINN)

将要测量的输入信号应用于输入引脚AINP和AINN。ADS1231接受差分输入信号,但也可以测量单极信号。

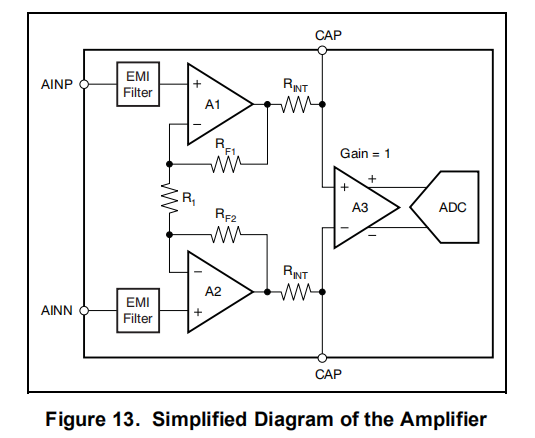

低噪声放大器

ADS1231采用低漂移、低噪声放大器,为桥接传感器提供完整的前端解决方案。放大器的简化图如图13所示。它由两个斩波稳定放大器(A1和A2)和三个精确匹配的电阻器(R1、RF1和RF2)组成,它们构成一个增益为128的差分前端级,然后是增益级A3(增益=1)。输入端配有EMI滤波器,如图13所示。EMI滤波器的截止频率为20MHz。以AVDD为参考输入,双极性输入范围为-19.5mV至+19.5mV。ADS1231的输入由连接到供电轨的内部二极管保护。这些二极管钳制所施加的信号,以防止其损坏输入电路。

外部电容器

两个ADS1231帽针上的外部电容器(CEXT)与内部电阻RINT(onchip)结合,形成低通滤波器。CEXT的推荐值为0.1μF,角频率为720Hz。这种低通滤波器有两个用途。首先,对输入信号进行频带限制,以防止ADC产生混叠,并滤除高频噪声。其次,它衰减放大器的斩波残余,以改善温度漂移性能。建议使用NPO或C0G电容器。为了获得最佳性能,将外部电容器放置在非常靠近盖脚的位置。

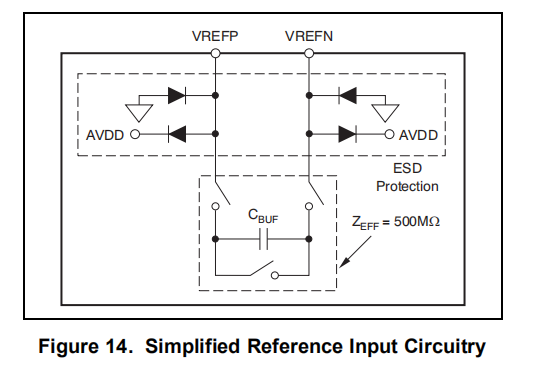

电压参考输入(VREFP、VREFN)

调制器使用的电压基准由VREFP和VREFN之间的电压差产生:VREF=VREFP–VREFN。这个参考输入采用类似于模拟输入的结构。为了提高参考输入阻抗,采用开关缓冲电路降低输入等效电容。基准漂移和噪声影响ADC的性能。为了达到最佳效果,请密切注意参考噪声和漂移规格。参考输入上电路的简化图如图14所示。开关和电容器可以用有效阻抗ZEFF=500MW近似建模。

ESD二极管保护参考输入。为防止这些二极管通电,请确保参考管脚上的电压低于GND的幅度不超过100毫伏,同样,也不要超过100毫伏的AVDD:

GND – 100mV < (VREFP or VREFN) < AVDD +100mV

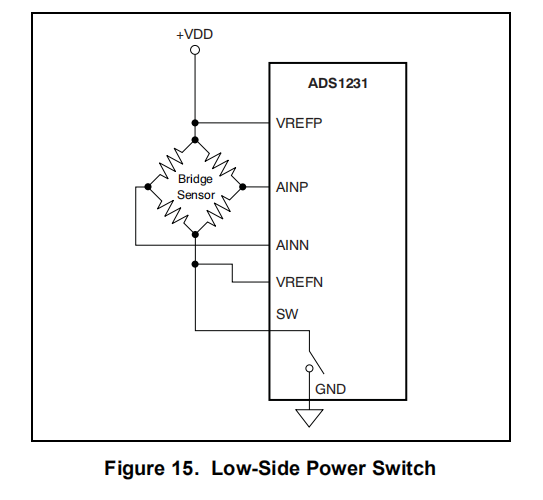

低压电源开关(SW)

ADS1231包含一个内部开关,用于外部桥接传感器,如图15所示。该开关可用于桥式电源的回流通道。通过打开开关,消除了电桥中的功耗。开关由ADS1231转换状态控制。在正常转换过程中,开关闭合(开关管脚接地)。在待机或断电模式下,开关断开(开关管脚为高阻抗)。使用开关时,建议将负参考输入(VREFN)直接连接到电桥接地端子,如图15所示,以获得最佳性能。

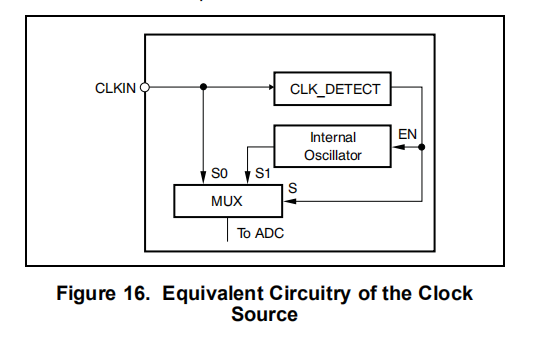

时钟源

ADS1231可以使用内部振荡器或外部时钟源来适应各种应用。图16显示了时钟模块的等效电路。CLK_检测块确定是否将外部时钟信号应用于CLKIN管脚,以便绕过或激活内部振荡器。当CLKIN管脚频率高于~200kHz时,CLK_检测电路关闭内部振荡器并将外部时钟信号传递给ADC。当CLKIN pin频率低于~200kHz时,CLK_检测块激活内部振荡器。选择内部振荡器时,确保将CLKIN引脚连接到GND。

外部时钟信号fCLKIN的允许频率范围在电气特性表中规定。

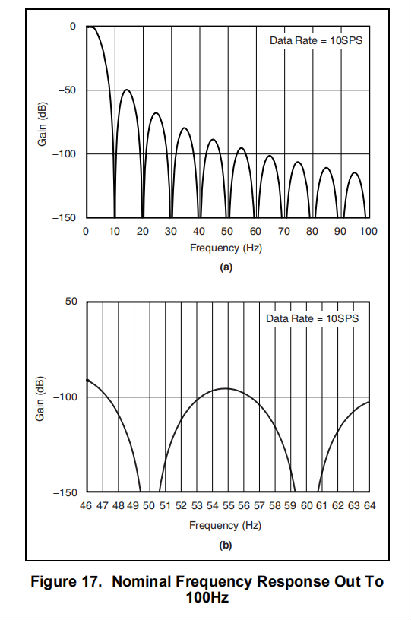

频率响应

ADS1231使用sinc4数字滤波器,频率响应如图17所示,fCLKIN=4.9152MHz。频率响应以76.8kHz调制器采样频率的倍数重复。总体响应是低通滤波器,其-3dB截止频率为3.32Hz,速度引脚绑定低(10SPS数据速率),11.64Hz,速度引脚绑定高(80SPS数据速率)。

为了帮助观察低频率下的响应,图17(a)说明了当数据速率为10SPS时,100Hz的标称响应。注意,10Hz倍率下的信号被拒绝,因此实现了50Hz和60Hz的同时拒绝。

使用sinc4滤波器的好处是,每个频率陷波器在同一位置上都有四个零点,从而对线周期干扰提供了极好的正常模式抑制。

图17(b)放大50赫兹和60赫兹的槽口,速度引脚绑定低(10SPS数据速率)。

ADS1231的数据速率和频率响应标度直接与时钟频率有关。例如,如果在速度管脚高的情况下,fCLKIN从4.9152MHz增加到5.5296MHz,则数据速率从80SPS增加到90SPS,而陷波也从80Hz增加到90Hz。请注意,这些更改仅在应用外部时钟源时才可能发生。

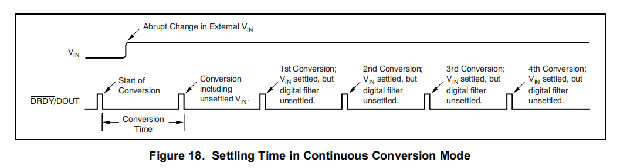

沉降时间

输入信号的快速变化需要时间来解决。例如,ADS1231前面的外部多路复用器可以通过简单地切换多路复用器输入信道来产生输入电压的突变。输入中的这些变化需要四个数据转换周期才能解决。连续转换时,可能需要五个读数来确定数据。如果输入的变化发生在第一次转换的中间,则需要对完全结算的输入进行四次完全转换才能获得完全结算的数据。丢弃前四个读数,因为它们只包含部分固定的数据。图18显示了ADS1231的稳定时间。

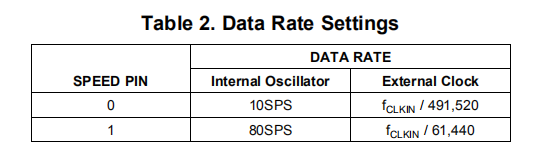

数据速率

ADS1231数据速率由速度引脚设置,如表2所示。当速度较低时,数据速率名义上为10SPS。该数据速率提供最低的噪声,并且对50赫兹和60赫兹的线周期干扰都有极好的抑制。对于需要快速数据速率的应用,设置高速选择名义上为80SPS的数据速率。

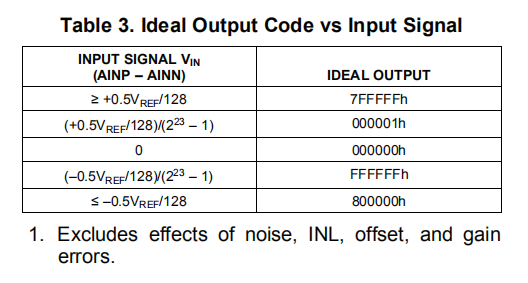

数据格式

ADS1231以二进制二进位补码格式输出24位数据。最低有效位(LSB)的权重为(0.5VREF/128)(223–1)。正满标度输入产生7FFFFFh的输出码,负满标度输入产生800000 h的输出码,对于超过满标度的信号,输出卡在这些码处。表3总结了不同输入信号的理想输出代码。

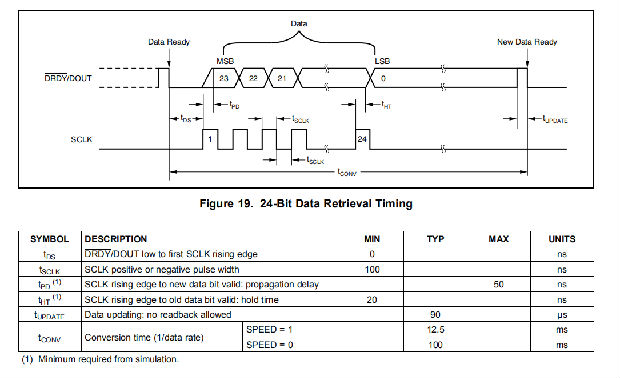

数据就绪/数据输出(DRDY/DOUT)

这个数字输出管脚有两个用途。首先,它指示新数据何时准备就绪。之后在SCLK的第一个上升沿DRDY/DOUT pin改变功能并开始输出转换数据,最高有效位(MSB)第一个。数据在每个后续的SCLK上升沿。毕竟24位已经检索后,可以使用附加SCLK。然后它会一直保持高位,直到新的数据准备好了。此配置在轮询确定何时开始的DRDY/DOUT状态。

串行时钟输入(SCLK)

这个数字输入随着每个上升沿将串行数据移出。此输入具有内置滞后,但仍应注意确保信号干净。故障或缓慢上升的信号可能导致不必要的额外移位。因此,最好确保SCLK的上升和下降时间均小于50ns。

数据检索

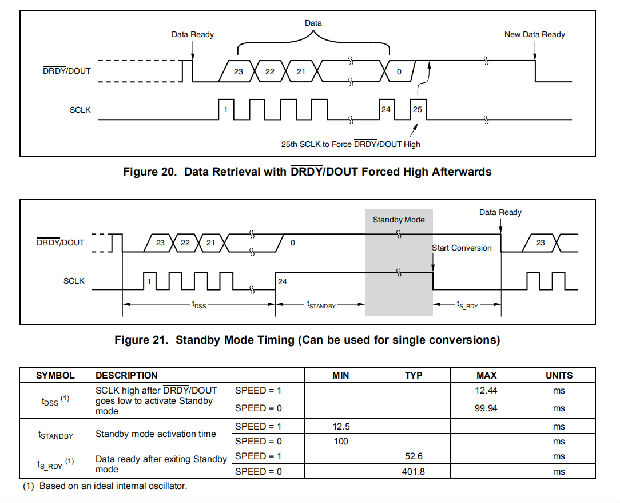

ADS1231连续转换模拟输入信号。要检索数据,请等到DRDY/DOUT低,如图19所示。医生走后低,开始通过应用SCLK移出数据。数据首先移出MSB。不需要将24位数据全部移出,但数据必须是在更新新数据之前检索(在tCONV内)否则数据将被覆盖。避免数据更新期间的检索(tUPDATE)。如果只有24已应用SCLKs,DRDY/DOUT仍在最后一位的状态移到高位(请参见tUPDATE),指示正在更新新数据。为了避免DRDY/DOUT留在最后一位的状态,第25个SCLK可应用于强制DRDY/DOUT高,如图20所示。当控制设备的主机正在轮询DRDY/DOUT以确定数据何时准备就绪时,此技术非常有用。

待机模式

待机模式通过关闭大部分电路显著降低功耗。要进入待机模式,只需在DRDY/DOUT变低后保持SCLK高;见图21。备份过程中随时可以启动待机模式;不必预先检索所有24位数据。

当tSTANDBY在SCLK保持高电平的情况下通过时,待机模式激活。当待机模式开始时,DRDY/DOUT保持在高位。SCLK必须保持高电平才能保持待机模式。要退出待机模式(唤醒),请将SCLK设置为低。退出待机模式后的第一个数据有效。

断电模式

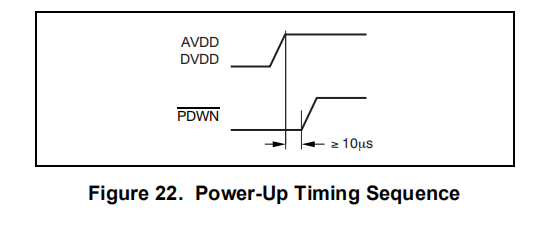

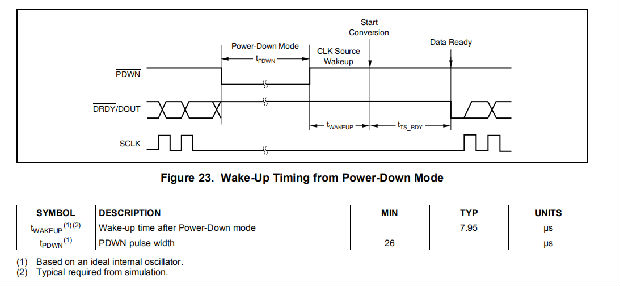

断电模式关闭整个ADC电路,并将总功耗降低到接近零。要进入断电模式,只需将PDWN引脚保持在低位。断电模式也会重置整个电路。在回读过程中,可以随时启动关机模式;它不是必须预先检索所有24位数据。图22。通电计时序列图23显示了断电模式下的唤醒计时。

应用实例

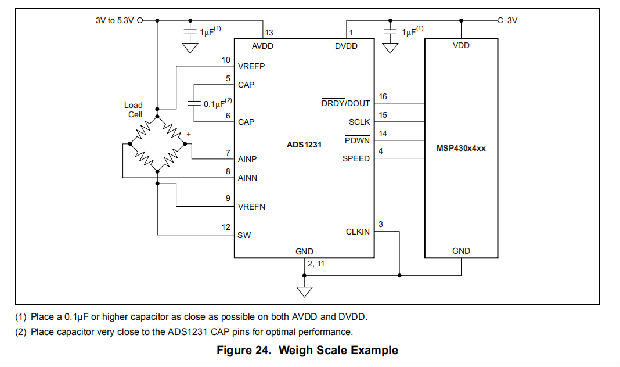

称重系统

图24显示了作为称重系统一部分的典型ADS1231应用程序。

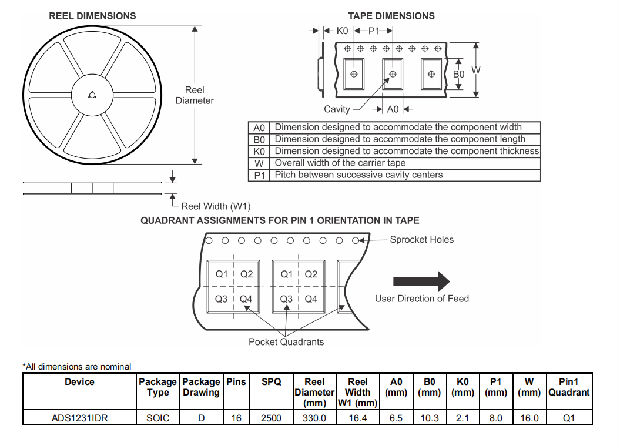

磁带和卷盘信息