130点击型号即可查看芯片规格书

ADL5801点击型号即可查看芯片规格书

特征

宽带上变频器/下变频器;功率转换增益1.8db;宽带射频、低频和中频端口;SSB噪声系数(NF)为9.75 dB;输入IP3:28.5 dBm;输入P1dB:13.3dbm;典型低驱动:0 dBm;单电源操作:130毫安时5伏;低功率运行的可调偏压;明桨,4 mm×4 mm,24导LFCSP封装。

应用

蜂窝基站接收机;无线链路下变频器;宽带块转换;仪表。

一般说明

ADL5801采用高线性、双平衡、有源混频器核心和集成LO缓冲放大器,提供从10mhz到6ghz的高动态范围频率转换。混频器得益于专有的线性化架构,当受到高输入电平的影响时,可提供增强的输入IP3性能。偏压调整特性允许使用单个控制管脚优化输入线性度、SSB噪声系数和直流电流。为自适应偏置控制提供了可选的输入功率检测器。高输入线性允许设备用于要求苛刻的蜂窝应用,其中带内阻塞信号可能会导致动态性能下降。自适应偏置特性允许部件在出现大阻塞信号时提供高输入IP3性能。当阻滞剂被移除时,ADL5801可以自动向下偏压以提供低噪声系数和低功耗。

平衡有源混频器配置提供极好的LO-toRF和LO-to-IF泄漏,通常优于-40 dBm。中频输出设计为在加载到200Ω负载时提供7.8 dB的典型电压转换增益。开路集电极中频输出的宽频范围允许ADL5801用作各种发射应用的上变频器。

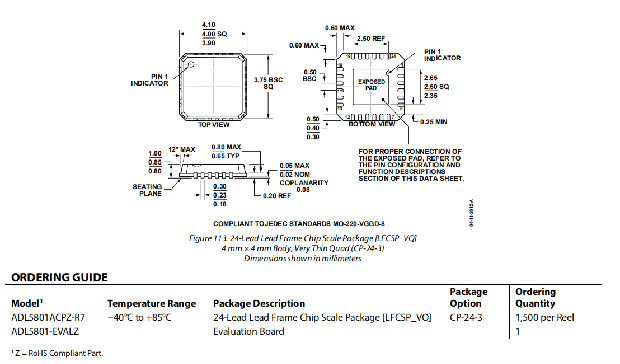

ADL5801采用SiGe高性能集成电路工艺制作。该装置采用紧凑型4 mm×4 mm 24引线LFCSP封装,工作温度范围为-40°C至+85°C。也有一个评估委员会。

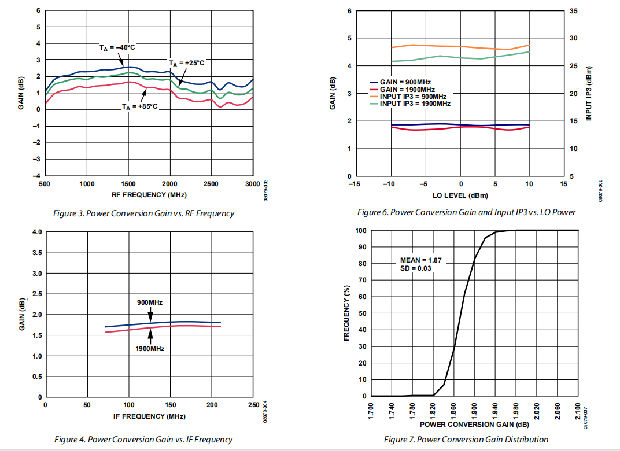

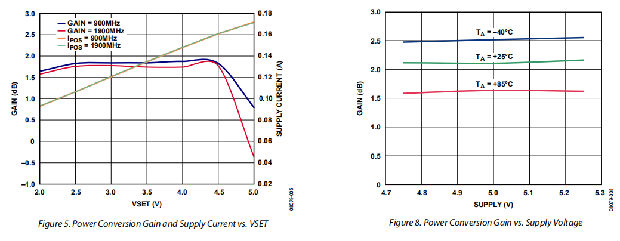

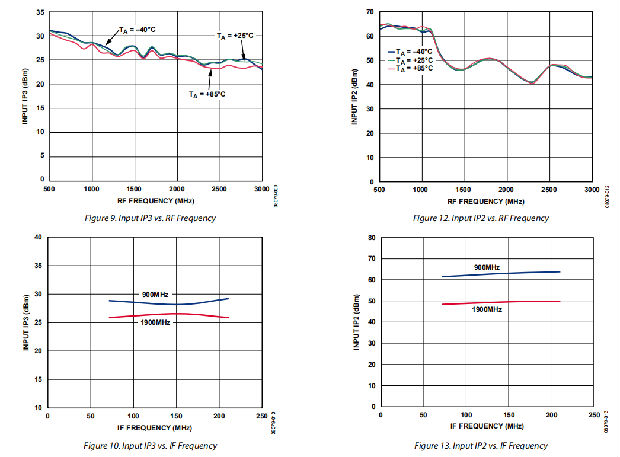

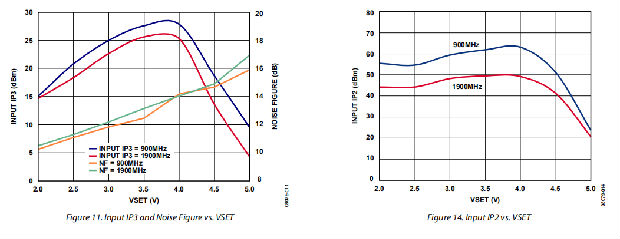

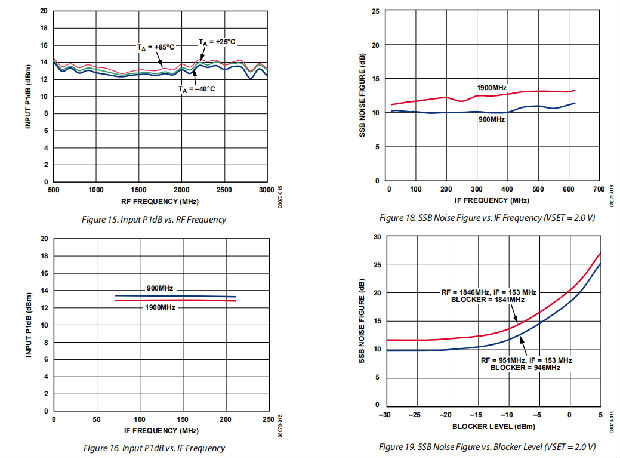

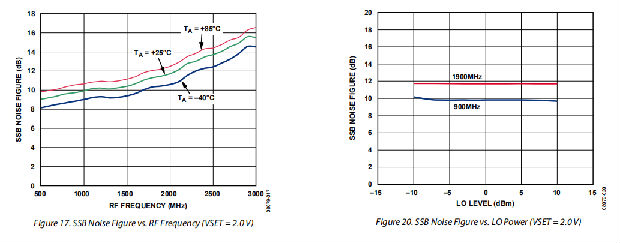

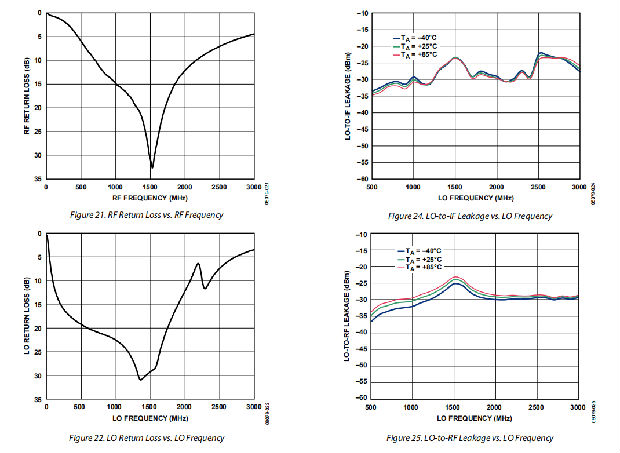

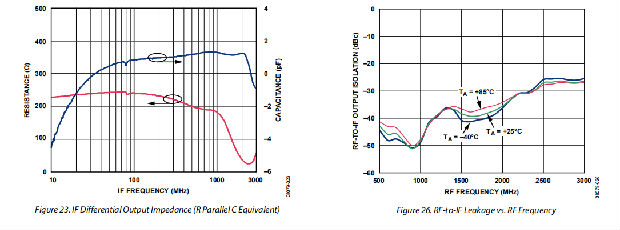

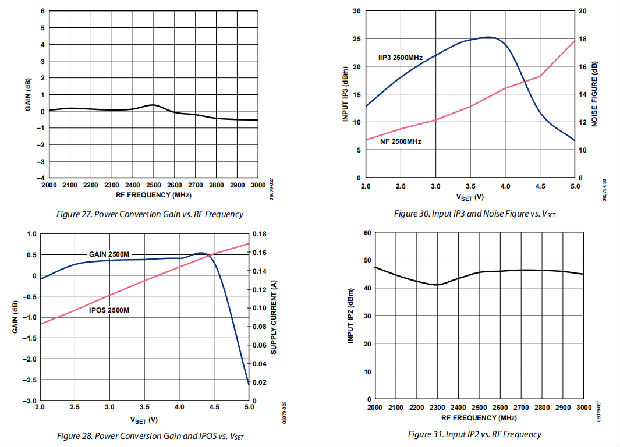

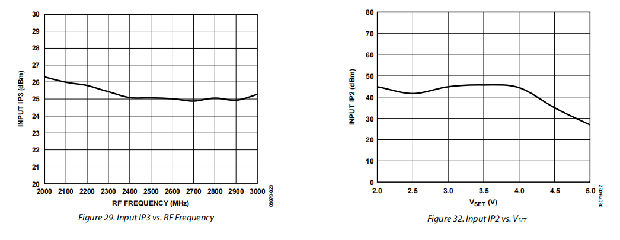

典型性能特征

宽带巴伦下变频模式

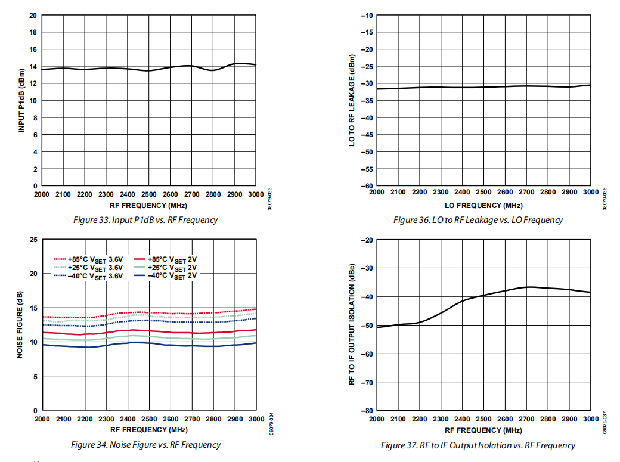

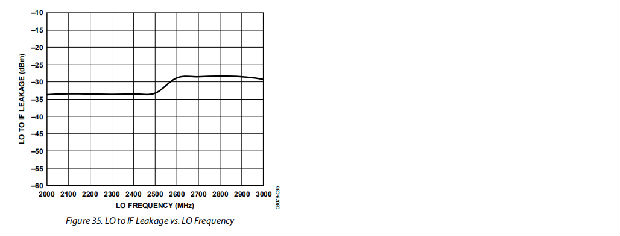

VS=5 V,TA=25°C,VSET=3.8 V,IF=153 MHz,除非另有说明,否则使用带有低端本地振荡器(LO)的典型电路原理图测量。从增益测量中提取输入和输出baluns(TC1-1-13M+,TC4-1W+)的插入损耗。

带MINI-CIRCUITS®TC1-1-43M+输入巴伦的下变频器模式

VS=5 V,TA=25°C,VSET=3.8 V,IF=211 MHz,使用带有低端本地振荡器(LO)的典型电路图测量,除非另有说明。增益测量包括输入和输出baluns(TC1-1-43M+,TC4-1W+)的插入损耗。

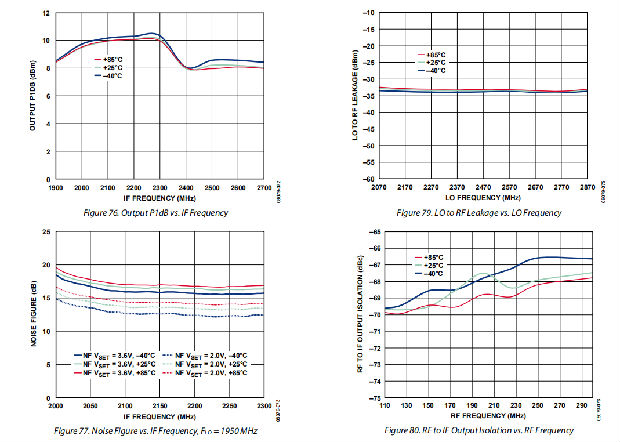

具有JOHANSON 3.5ghz输入巴伦的下变频器模式

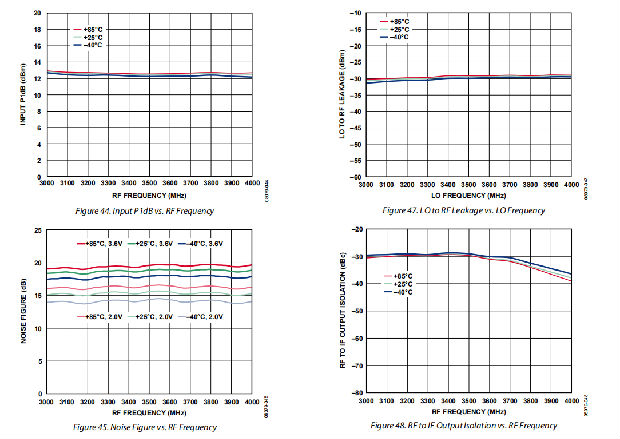

VS=5 V,TA=25°C,VSET=3.6 V,IF=153 MHz,使用带有低端本地振荡器(LO)的典型电路图测量,除非另有说明。增益测量包括输入和输出baluns(3600BL14M050,TC4-1W+)的插入损耗。

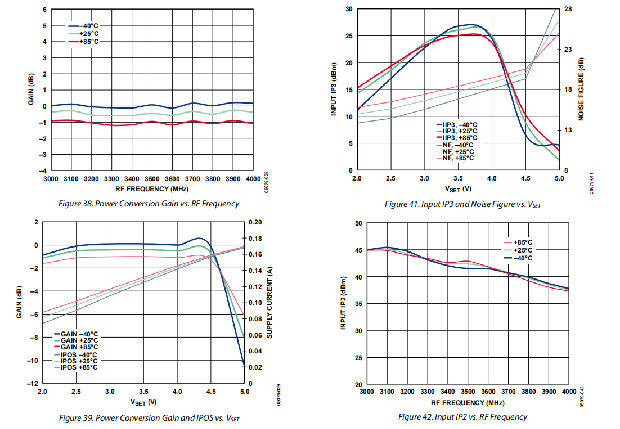

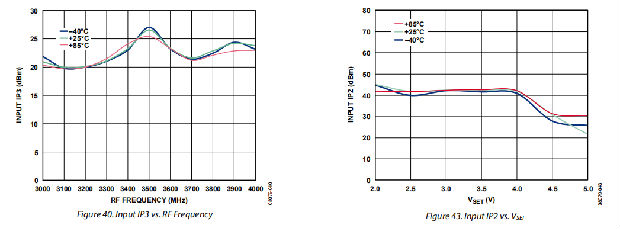

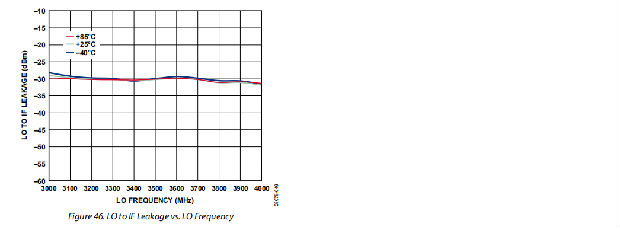

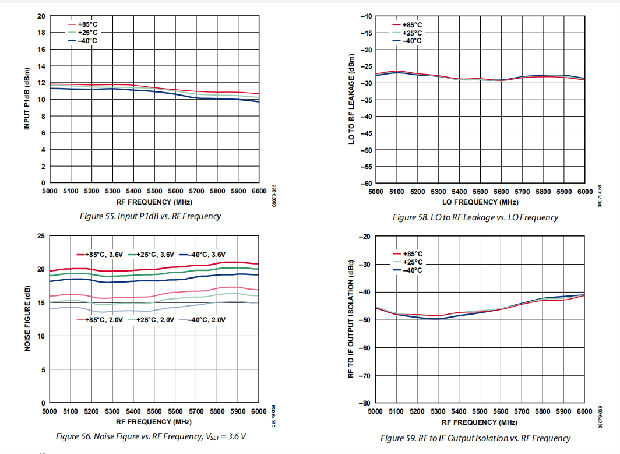

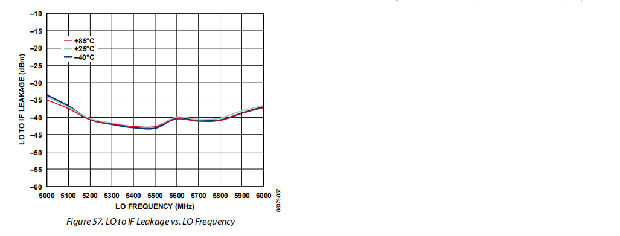

JOHANSON 5.7ghz下变频模式

VS=5 V,TA=25°C,VSET=3.6 V,IF=153 MHz,使用带有低端本地振荡器(LO)的典型电路图测量,除非另有说明。增益测量包括输入和输出baluns的插入损耗(5400BL14B050,TC4-1W+)。

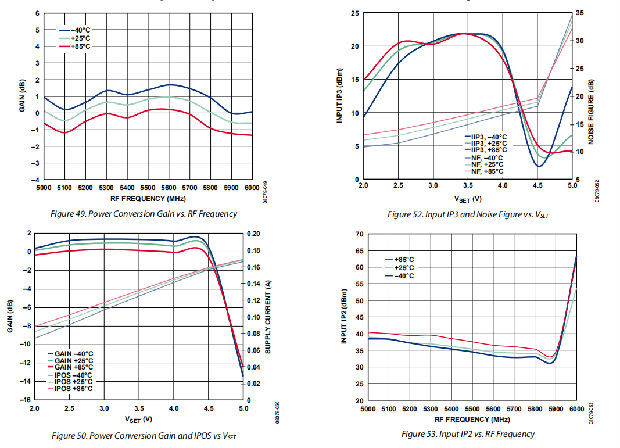

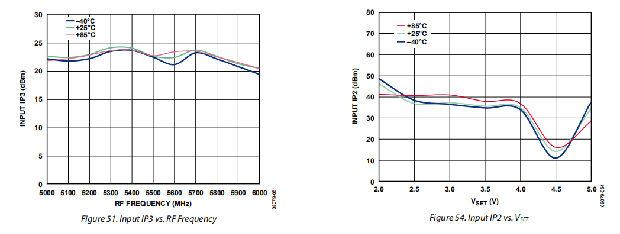

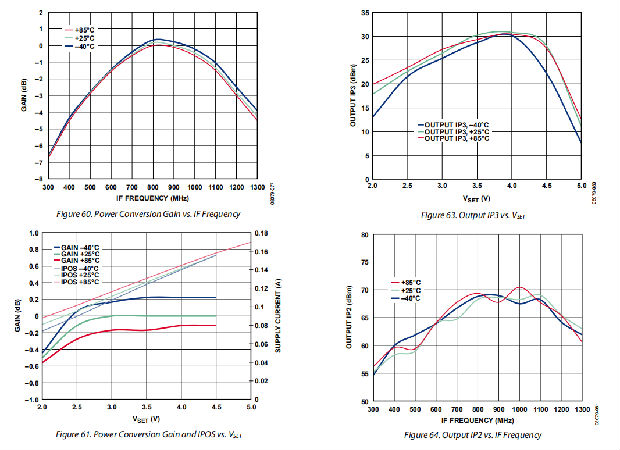

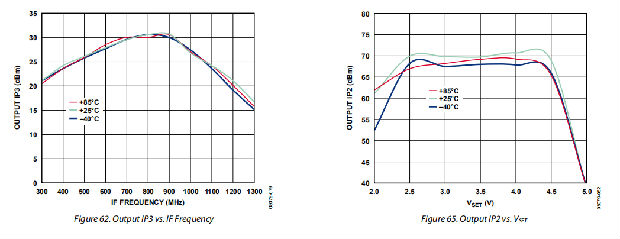

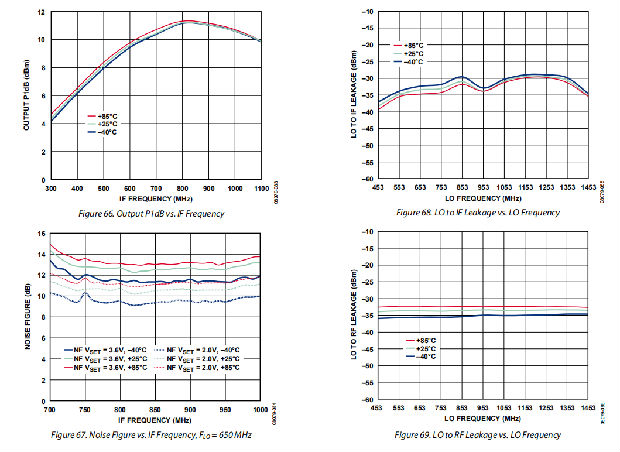

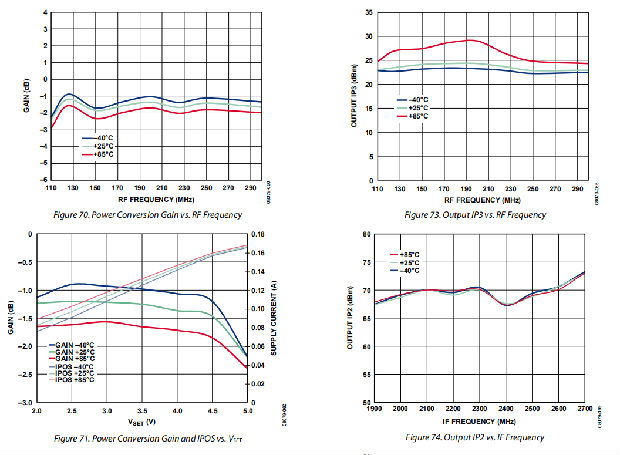

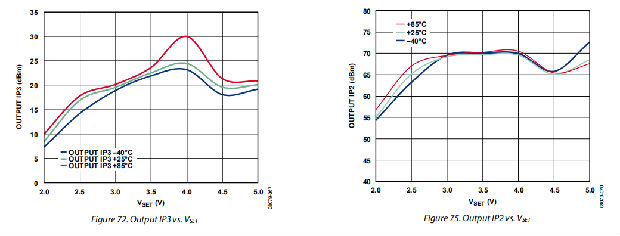

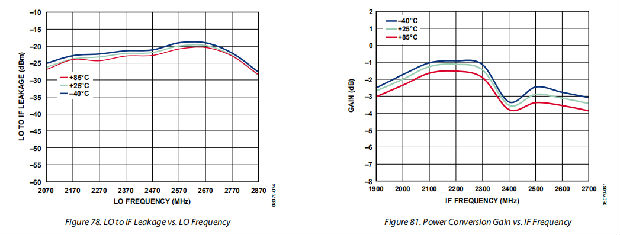

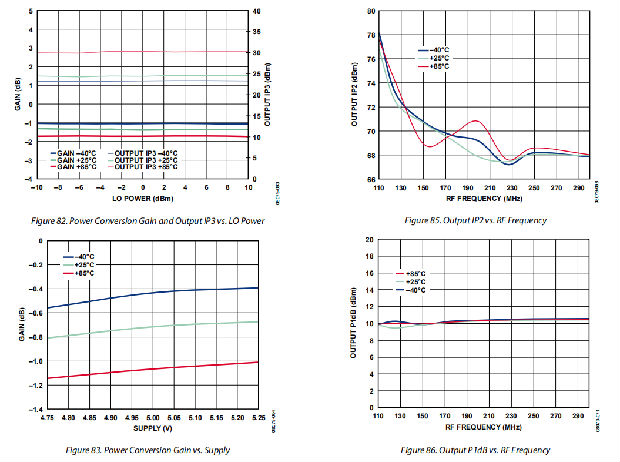

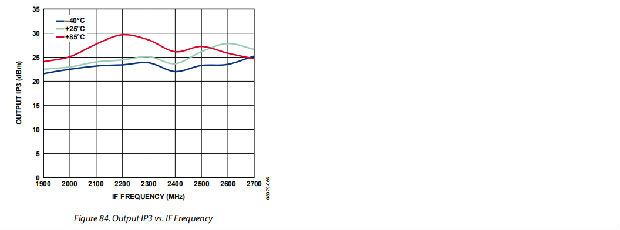

900兆赫输出匹配的上变频器模式

VS=5 V,TA=25°C,VSET=3.6 V,RF=153 MHz,使用带有低端本地振荡器(LO)的典型电路图测量,除非另有说明。输入和输出balun(TC1-1-13M+,TC4-14)的插入损耗包含在增益测量中。

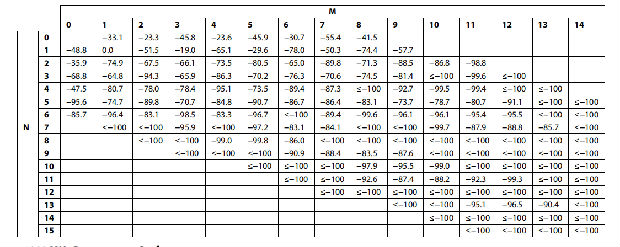

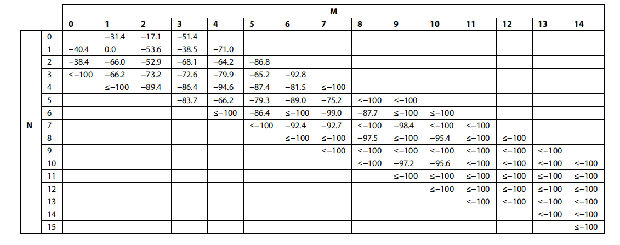

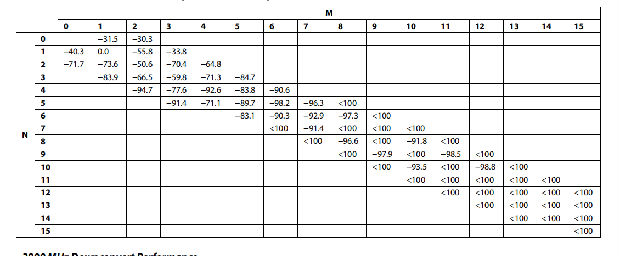

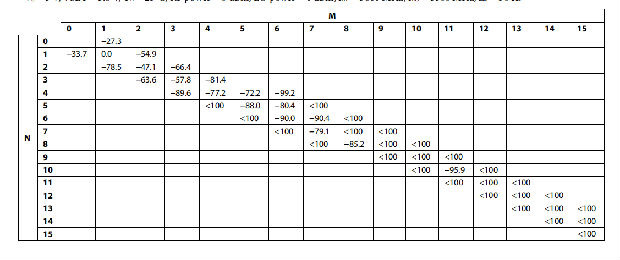

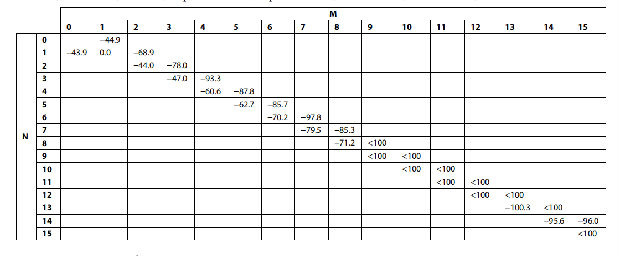

激励性能

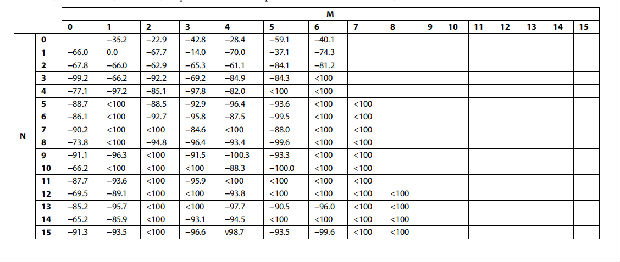

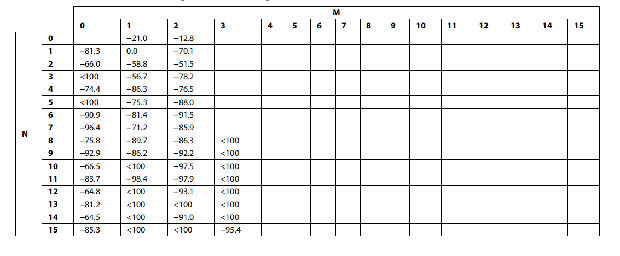

所有丁坝表均为(N×fRF)-(M×fLO),并使用标准评估委员会进行测量(见评估委员会一节)。混频器杂散产物的测量单位为分贝,与中频输出功率电平的载波(dBc)有关。数据只针对小于6ghz的频率进行测量。测量系统的典型噪声下限为-100 dBm。

900兆赫下变频性能

VS=5 V,VSET=3.8 V,TA=25°C,射频功率=0 dBm,低功率=0 dBm,fRF=900 MHz,fLO=703 MHz,Z0=50Ω。

1900兆赫下变频性能

VS=5 V,VSET=3.8 V,TA=25°C,射频功率=0 dBm,低功率=0 dBm,频率=1900 MHz,频率=1703 MHz,Z0=50Ω。

2600兆赫下变频性能

VS=5 V,VSET=3.8 V,TA=25°C,射频功率=0 dBm,低功率=0 dBm,fRF=2600 MHz,fLO=2350 MHz,Z0=50Ω。

3800兆赫下变频性能

VS=5 V,VSET=3.8 V,TA=25°C,射频功率=0 dBm,低功率=0 dBm,fRF=3800 MHz,fLO=3500 MHz,Z0=50Ω。

5800兆赫下变频性能

VS=5 V,VSET=3.8 V,TA=25°C,射频功率=0 dBm,低功率=0 dBm,fRF=5800 MHz,fLO=5600 MHz,Z0=50Ω。

806MHz上变频性能

VS=5 V,VSET=3.8 V,TA=25°C,射频功率=0 dBm,低功率=0 dBm,fRF=140 MHz,fLO=946 MHz,Z0=50Ω。

2210兆赫上转换性能

VS=5 V,VSET=4.0 V,TA=25°C,射频功率=0 dBm,低功率=0 dBm,频率=140 MHz,频率=2350 MHz,Z0=50Ω。

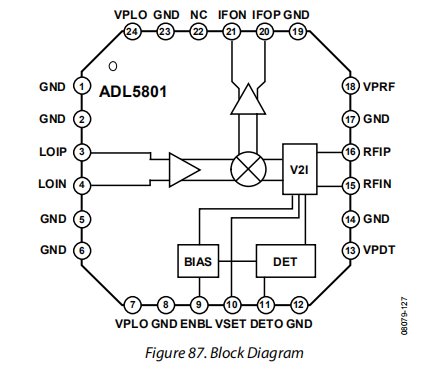

电路说明

ADL5801包括一个具有50Ω输入阻抗和250Ω输出阻抗的双平衡有源混频器。此外,ADL5801集成了一个本地振荡器(LO)放大器和一个射频功率检测器,可用于优化混频器的动态范围。RF和LO是差分的,在输入和输出端口提供最大可用带宽。本振也可在50Ω输入阻抗下工作,并可选择差动或单端操作。输入、输出和LO端口可以在非常宽的频率范围内工作。ADL5801可以配置为下变频混频器或上变频混频器。

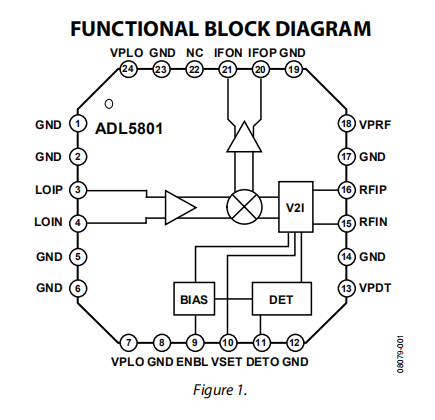

ADL5801可分为以下部分:LO放大器和分配器、RF电压电流(V-to-I)转换器、混频器核心、输出负载、RF检测器和偏置电路。设备的简化框图如图87所示。LO块产生一对差分LO信号来驱动两个混频器核心。射频输入功率通过V-to-I转换器转换成射频电流,然后馈入两个混频器核心。混频器的内部差动负载提供来自混频器的宽带250Ω输出阻抗。每个部分的参考电流由偏置电路产生,可以使用ENBL引脚启用或禁用。下面将详细描述ADL5801的每个部分。

LO放大器和分路器

LO输入由一系列放大器调节,以向混频器核心提供良好控制和有限的LO摆动,从而产生优秀的输入IP3。使用宽带低噪声放大器(LNA)放大LO输入,然后跟随LO限制放大器。LNA输入阻抗名义上为50Ω。本振电路具有较低的加性噪声,在射频阻断下具有良好的混频器噪声系数和输出噪声。为获得最佳性能,LO输入应以差分方式驱动,但频率较低;可接受单端驱动。

射频电压电流(V-TO-I)转换器

差分RF输入信号被应用于V-to-I转换器,该转换器将差分输入电压转换为输出电流。V-to-I转换器提供50Ω输入阻抗。V-to-I段偏置电流可以使用VSET管脚上下调节。调高电流可以改善IP3和P1dB的输入,但会降低SSB的噪声系数。降低电流可以提高SSB的噪声系数,但会降低IP3和P1dB的输入。转换增益在VSET管脚设置的广泛范围内几乎保持恒定,允许在不影响转换增益的情况下动态调整部件。

混合器芯

ADL5801有一个使用高性能SiGe NPN晶体管的双平衡混频器。该混频器基于四个交叉连接晶体管的吉尔伯特单元设计。

混频器输出负载

混频器负载使用一对125Ω电阻器连接到正极电源。这提供了250Ω的差分输出电阻。混频器输出应通过一对射频扼流圈或使用中心抽头连接到正极电源的输出变压器从外部拉到正极电源。当混频器铁心电流较低时,可以排除这些元件,但随后P1dB输入和IP3输入都减小。

混频器负载输出可以从直流电(dc)到大约600兆赫,再到200Ω负载。对于上转换应用,混频器负载可以使用片外匹配组件进行匹配。传输操作可达3ghz。有关匹配电路的详细信息,请参阅应用程序信息部分。

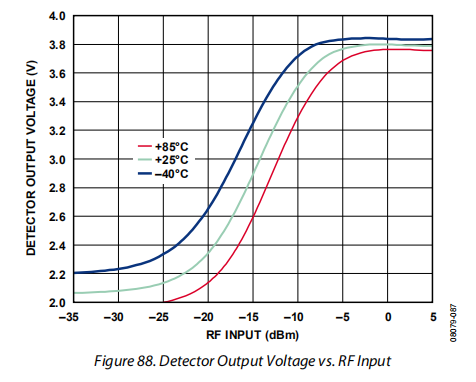

射频探测器

射频功率检测器从V-to-I转换器部分缓冲。该探测器的功率响应范围约为-25 dBm至0 dBm,并提供电流输出。当混频器输入端存在大的射频信号时,输出电流被设计为连接到VSET管脚以提高混频器芯电流。外部电容器可用于调整此功能的响应时间。如果不使用,DETO引脚可以保持打开或接地。

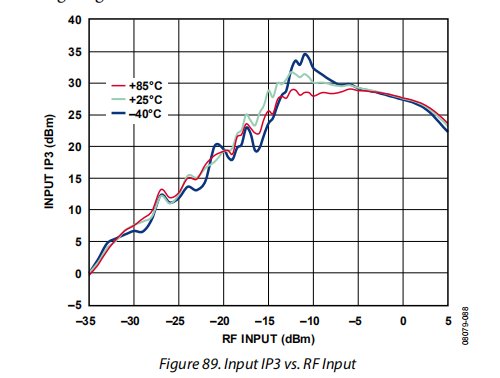

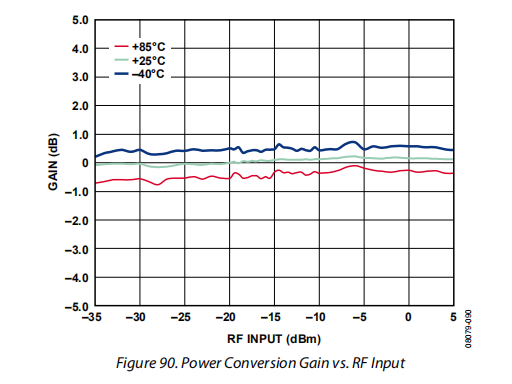

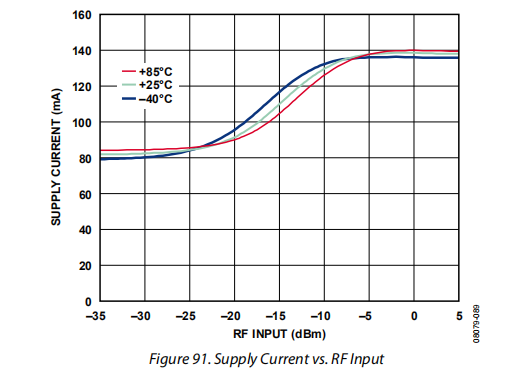

探测器在下变频器模式下的宽带巴伦段条件下进行了表征。引脚11(DETO)与引脚10(VSET)相连,并绘制了这些引脚上的电压与射频输入功率水平、温度和许多设备的关系图。

在这些条件下,还记录了输入IP3、增益和电源电流。结果如图89至图91所示。

偏置电路

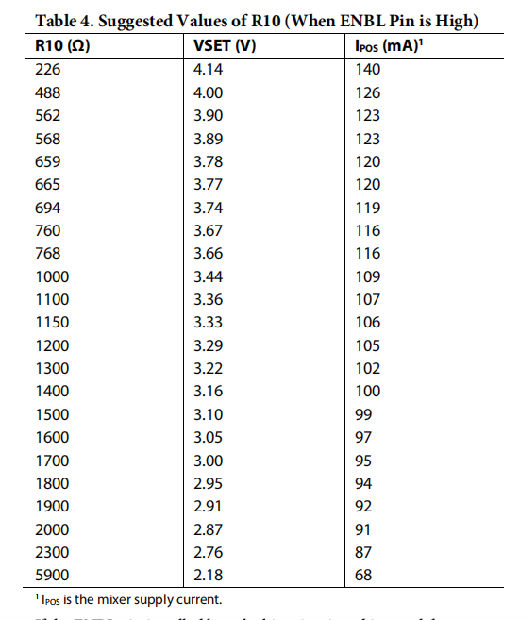

带隙基准电路产生混频器使用的基准电流。使用ENBL管脚可以启用和禁用偏置电路和内部探测器。将ENBL引脚拉高可关闭偏置电路和内部探测器。然而,ENBL引脚不会改变LO段中的电流,因此,不提供真正的掉电特性。当ENBL引脚被拉高时,可以通过向VSET引脚施加外部电压或通过将电阻器从VSET引脚连接到正极电源来操作设备。在内部,VSET管脚具有串联电阻和二极管对地;因此,仅用一个简单的分压器驱动管脚是不够的。表4列出了该电阻器的一些典型值以及当ENBL引脚设置为高时产生的VSET值和电源电流。使用表4选择适当的R10值(见图110),以达到所需的混频器偏置水平。在这种操作模式下,VSET管脚不能保持浮动,占位符R7和R9必须保持打开状态。

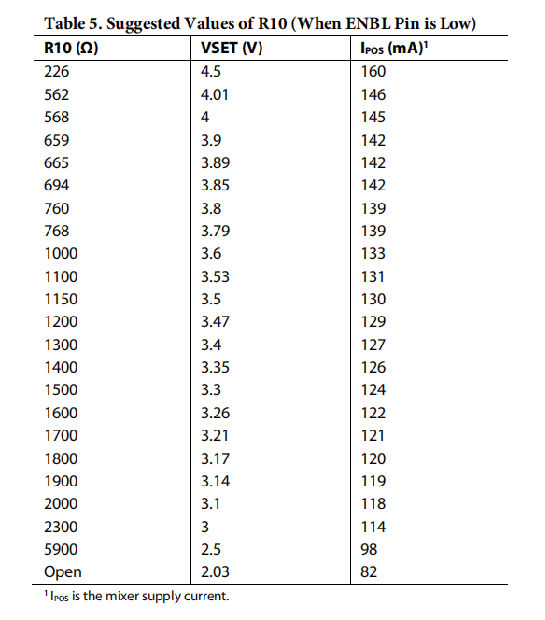

如果将ENBL引脚拉低,则设备的偏置电路和内部探测器将启用。在这种模式下,可以通过向VSET引脚施加外部电压或将电阻器从VSET引脚连接到正极电源来操作设备。表5列出了该电阻器的一些典型值以及当ENBL引脚设置为低时产生的VSET值和电源电流。使用表5选择适当的R10值(见图110),以达到所需的混频器偏置水平。在此操作模式下,R7和R9必须保持打开状态。

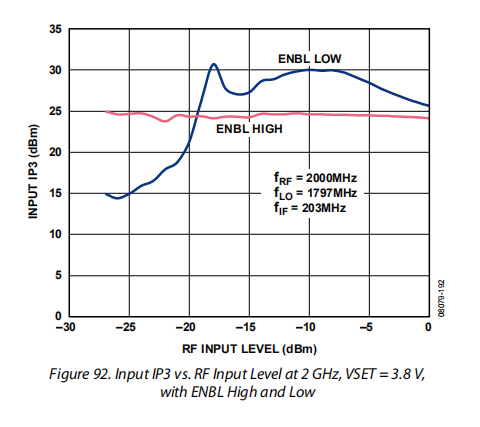

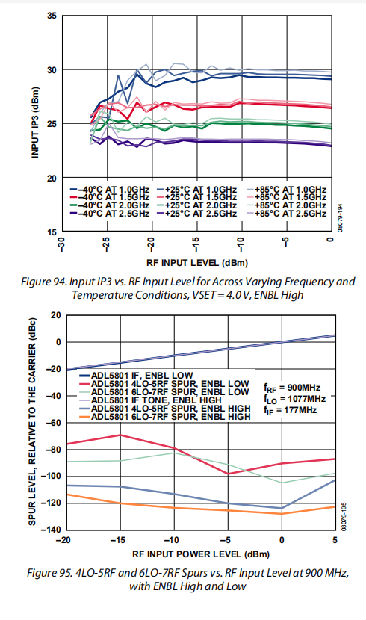

可选地,VSET管脚可以连接到DETO管脚,以使用内部检测器提供动态混频器偏置控制。图92是当ENBL引脚被拉高和拉低时,在2ghz时输入IP3性能与RF输入功率电平的比较。将ENBL拉高可改善输入功率电平之间的线性度,而将ENBL拉低可提高较高功率电平下的IP3性能。当ENBL引脚被拉得很高时,该器件还表现出更好的激励性能。图95是在900兆赫的ENBL高电平和低电平下,4LO-5RF和6LO-7RF杂散与射频输入功率电平的比较。

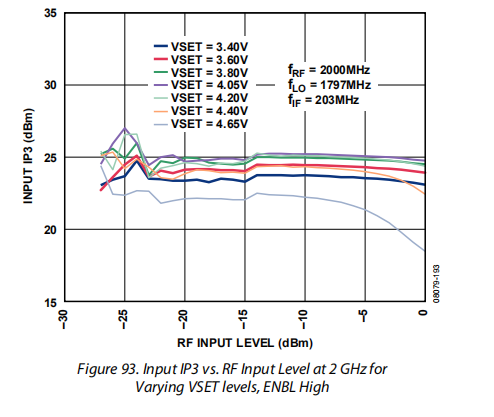

图93是当ENBL管脚被拉高时,在2ghz的不同VSET电平的输入IP3与RF输入功率电平的图。在这种工作模式下,该器件在4.0v的VSET电平下表现出最佳的线性度。如前所述,可以使用外部电压或通过将电阻器从VSET引脚放置到正极电源来设置VSET电平。图94是当ENBL在不同的温度和频率条件下被拉高时,4.0v的VSET电平的输入IP3与RF输入功率电平的图。该装置在不同的频率范围内表现良好,并表现出优异的温度灵敏度。

应用程序信息

基本连接

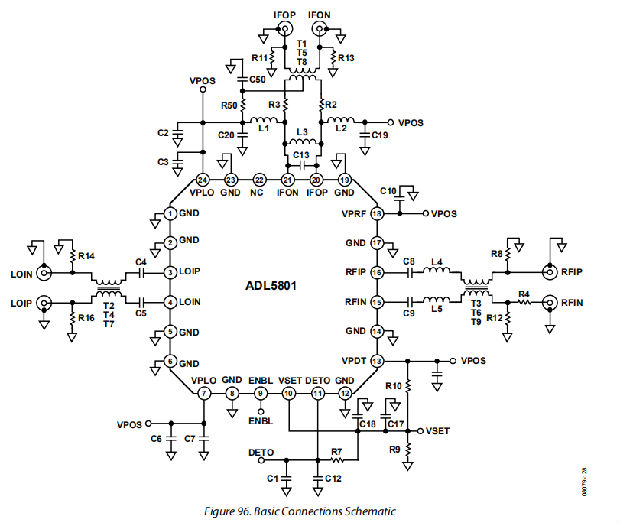

ADL5801设计用于在射频(RF)和中频(IF)之间转换。对于上转换和下转换应用程序,必须将RFIP(Pin 16)和RFIN(Pin 15)配置为输入接口。必须将IFOP(引脚20)和IFON(引脚21)配置为输出接口。每个电源引脚(引脚7、引脚13、引脚18和引脚24)、VSET控制引脚(引脚10)和DETO探测器输出引脚(引脚11)附近需要单独的旁路电容器。当选择片上探测器形成闭环,自动控制VSET引脚时,R7可以填充0Ω电阻。或者,只需在VSET和DETO测试点之间使用跳线进行评估。图96说明了ADL5801操作的基本连接。

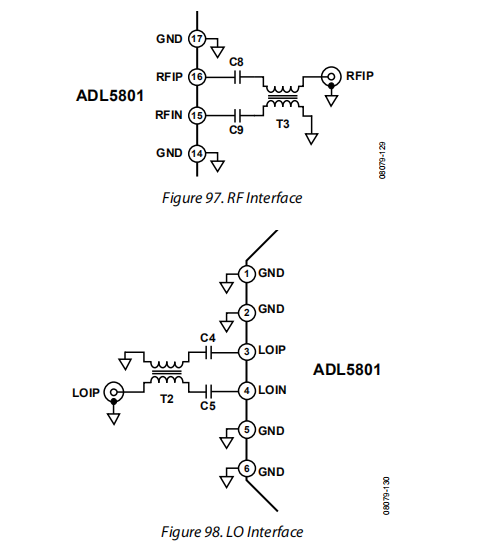

射频和低端口

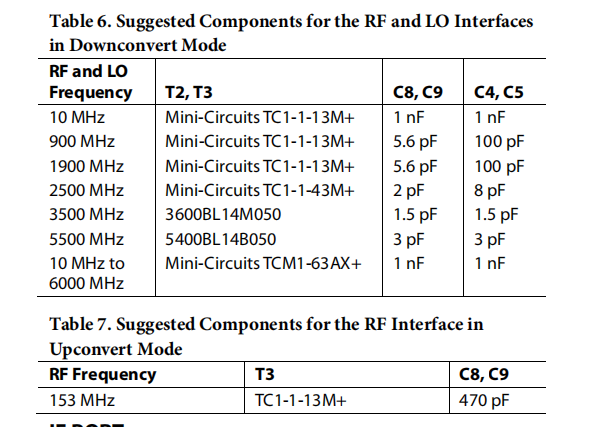

射频和低输入端口设计用于大约50Ω的差分输入阻抗。图97和图98分别说明了射频和LO接口。建议通过巴伦驱动每个射频和低差分端口,以获得最佳性能。还需要对射频和低端口进行交流耦合。使用适当值的电容器有助于改善期望频率上的输入返回损耗。表6和表9列出了上转换和下转换模式下各种射频和低频波段的推荐组件。特性数据可在典型性能特性部分获得。

中频端口

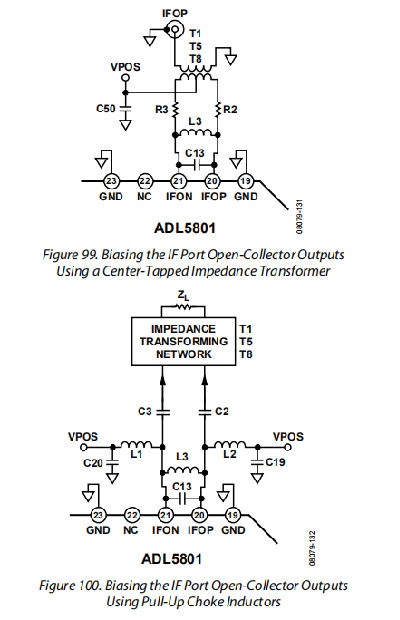

IF端口具有开放的收集器、差分输出接口。必须使用图99和图100中所示的方案之一来偏置开路集电极输出。

图99显示了中心抽头阻抗变压器的使用。应选择变压器的匝数比,以提供所需的阻抗变换。在50Ω负载阻抗的情况下,应使用4:1阻抗比变压器将50Ω负载转换为中频输出引脚处的200Ω差动负载。

图100显示了使用上拉扼流圈电感偏置开路集电极输出的差分中频接口。用于将直流电流耦合到混频器磁芯的扼流圈电感的分流阻抗应足够大,以使其在达到预期负载之前不会降低输出电流。此外,所选扼流圈电感的直流电流处理能力必须至少为45毫安。

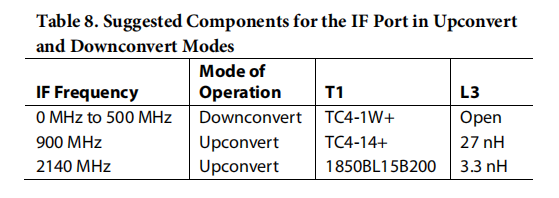

所选扼流圈电感的自谐振频率必须高于预期的中频频率。从Coilcraft®和Murata等制造商处可以买到各种合适的扼流圈感应器。在中频输出端,可能需要阻抗转换网络将最终负载阻抗转换为200Ω。表8列出了上转换和下转换模式下IF端口的建议组件。

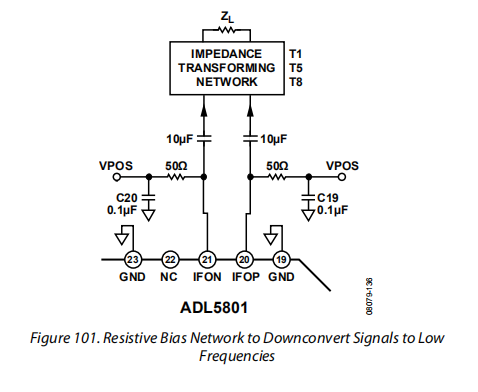

下变频至低频ZL

为了下变频到更低的频率,器件应该在输出端用一个电阻偏置。该装置中频输出共模电压应为3.75v,以确保最佳性能。图101提供了将900 MHz输入信号下变频至100 kHz的示例设置。在图101所示的设置中,设备的输出被50Ω电阻偏置。在这种工作模式下,当500兆赫的信号下变频到100千赫、10千赫或1千赫时,器件显示出2.0分贝的转换增益。

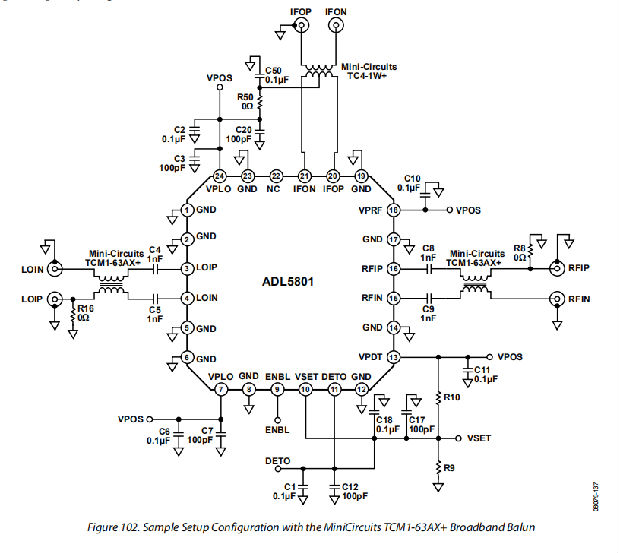

宽带业务

ADL5801可以支持从10兆赫到6兆赫的输入频率。对于需要宽带频率覆盖的应用,该设备可以使用宽带balun操作,例如小型电路TCM1-63AX+。图102示出了在RF和LO端口上填充微型电路TCM1-63AX+balun的示例设置配置。此单一设置解决方案提供了利用设备完整输入频率范围的选项。

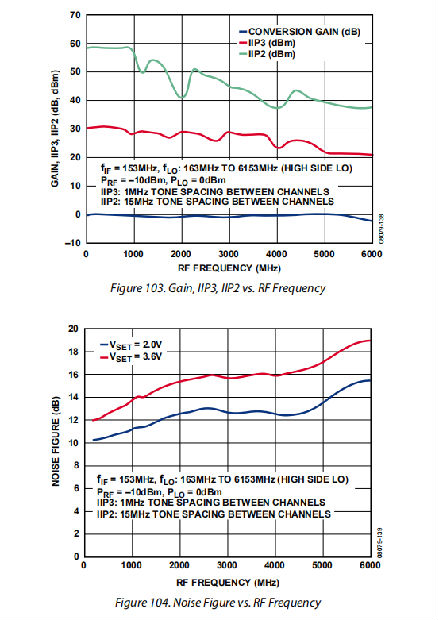

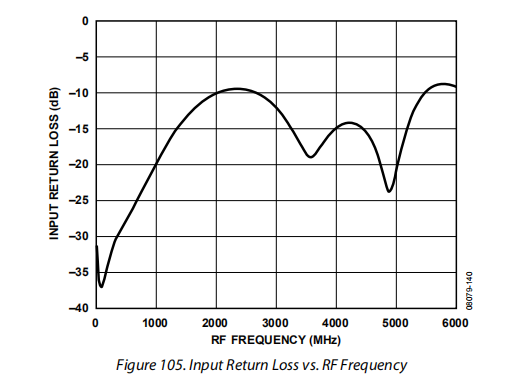

图103至图105展示了在射频和LO端口上填充了小型电路TCM1-63AX+的混频器的性能。

该设备在10 MHz至6 GHz频带内保持20 dBm或更高的输入IP3和-2 dB或更高的转换增益。

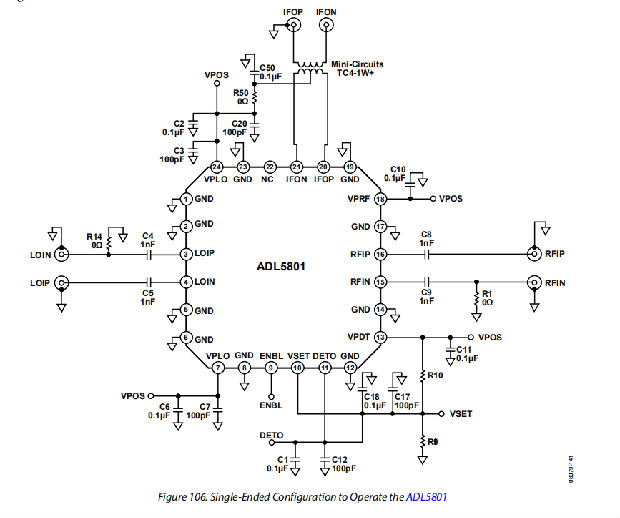

射频和低输入的单端驱动

有源混频器的RF和LO端口可以单端驱动,而无需单端操作的balun。在这种配置中,未使用的RF和LO端口应使用1nf电容器进行交流接地。图106描绘了建议在单端模式下操作设备的设置配置。

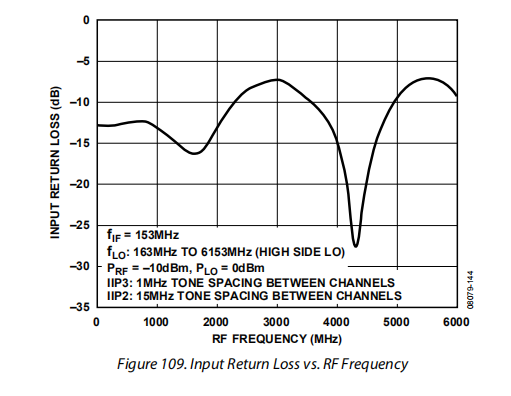

图107至图109展示了单端模式下混频器的性能。

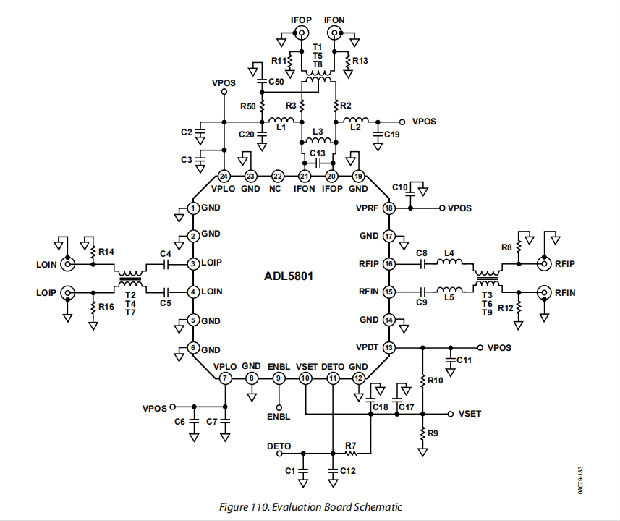

评估委员会

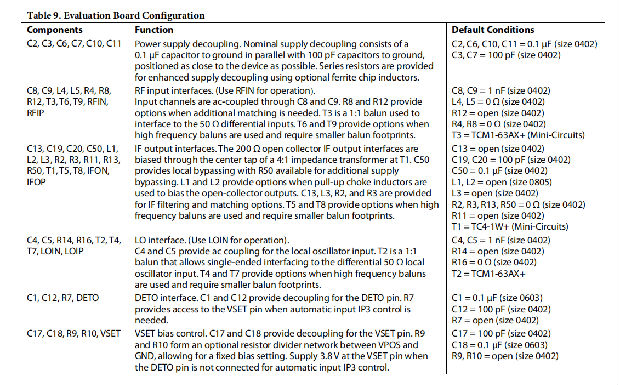

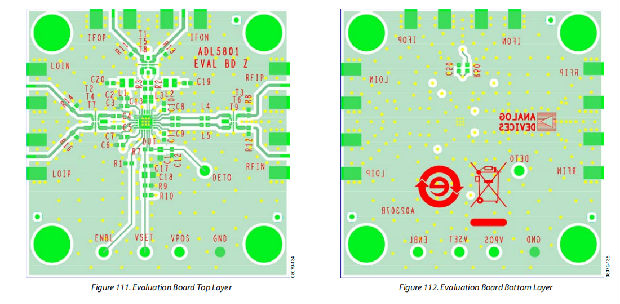

ADL5801有一个评估板。标准评估板采用Rogers®RO3003材料制造。每个RF、LO和IF端口都配置为通过balun变压器进行单端信令。评估板的示意图如图110所示。表9描述了评估板的各种配置选项。电路板的布局如图111和图112所示。

外形尺寸