VECANA01点击型号即可查看芯片规格书

功能应用程序

10全差分输入交流电机速度控制5路同步采样三相功率控制加2同步采样

频道

振动分析

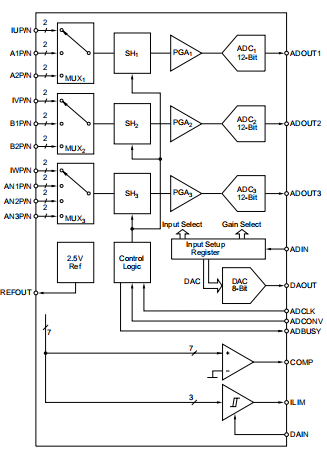

3个同步12位ADCμ12.8s吞吐率数字可选输入范围±5V电源IUP/编号串行数字输入/输出A1P/NADOUT1号3个数字签名A2P/N号

可编程窗口比较器IVP/N号说明B1P/NADOUT2号B2P/编号

VECANA01由三个12位模拟数字转换器组成,前面同时有五个IWP/编号用于10个差分输入的操作采样保持放大器和多路复用器。ADC具有模拟串行输出,用于高速数据传输和数据处理。AN1P/编号ADOUT3号AN2P/编号AN3P/编号VECANA01还提供可编程增益放大器,可编程增益为1.0V/V、1.25V/V,2.5V/V和5.0V/V。通道选择和增益选择可通过串行输入控制字选择重新输出。

该部分还包含一个8位数字到模拟转换器-其数字输入作为输入控制字的一部分提供的转换器。

功能描述

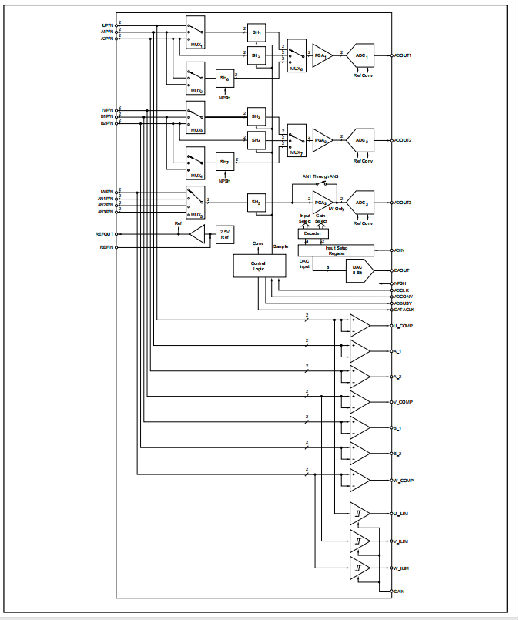

图1。功能图。

VECAN01是一个三重12位SAR a/D转换器,由双±5V电源供电。该部分包括三个12位逐次逼近adc、10个全差分输入的多路复用器、5个差分输入同步采样保持放大器以及两个异步采样保持放大器。它通过三个同步SPI/SSI串行输出和一个输入端口进行通信。VECANA01在外部时钟上运行,外部时钟还决定输出数据速率(参见图2)。

多路复用器

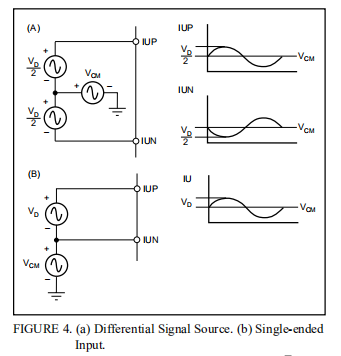

VECANA01具有多个输入多路复用器,用于选择所需的模拟输入,并将适当的采样和保持输出连接到PGAs和A/D转换器。解码器从输入设置寄存器接收其输入并驱动mux(有关选择输入信道的信息,请参见表VII和表VIII)。输入多路复用器可以接收全差分或单端信号(见图4和表III)。模拟信号通过采样保持差分,PGA一直到A/D转换器的输入端。这提供了最好的噪声抑制。

样品保存VECANA01包含七个采样保持放大器。其中五个(SH1到SH5)同时采样,并在内部同步采样和保持定时(定时如图2所示)。三个采样和保持(SH1、SH3和SH5)连接到输入多路复用器,以便它们可以为所有信道输入提供同步采样。此外,SH2和SH4同时采样其信道的第三个输入(分别为A2和B2)。这在电机控制应用中很有用,其中A1和B1是一个位置传感器的正交输入,A2和B2是第二个位置传感器的正交输入(见图9)。在该应用中,希望同时采样给定位置传感器的正交输入(即使它们在连续的转换周期中被转换)(见表VII),以便在相同的轴位置捕获它们的值。VECANA01还具有有限异步采样的能力。SH6和SH7的采样由控制信号NPSH异步控制(见表七)。这允许两个输入,分别在通道1和通道2(见表VIII)上,从另一个采样保持的定时异步采样。这在电机控制应用中非常有用,因为每个通道的两个输入需要异步采样到一个参考点。

ADC和PGA

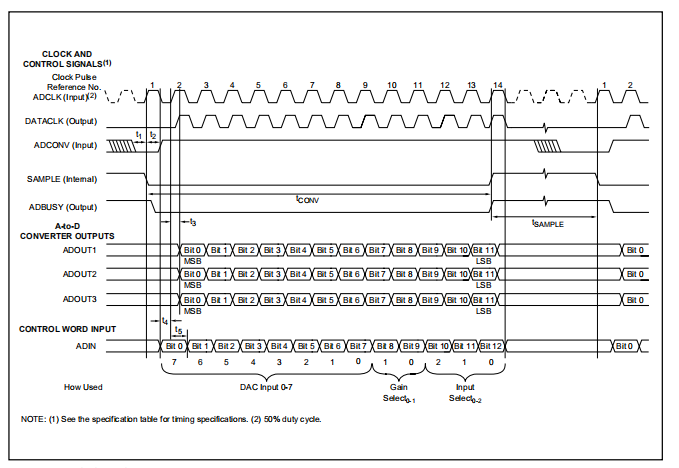

图2。时序图。VECANA01包含三个信号通道,每个通道都有12位a/D转换器输出。A/D转换器同步工作,其串行输出同时发生(表九给出了模拟输入/数字输出关系)。可编程增益放大器位于A/D转换器之前(表九给出了增益选择信息)。对于通道1和通道2,PGA对所有三个模拟输入都有效。对于第三信道,PGA只改变IW输入的增益。无论增益选择值如何,输入AN1、AN2和AN3以1.0V/V的固定增益连接到A/D转换器3。

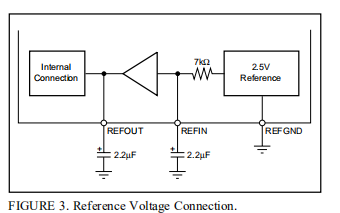

电压基准

VECANA01包含一个内部2.5V电压参考。它可以通过输出缓冲放大器从外部获得。如果需要使用外部参考,可以在REFIN引脚处连接一个。该引脚对于外部参考电压的输出电阻通常为7kΩ。然后,这会覆盖内部2.5V参考电压,并连接到A/D转换器。它也可用作重新输出端的缓冲输出。

基准电压应通过外部电容器(约2.2μF)缓冲在REFIN引脚和REFOUT引脚(见图3)上,尽可能靠近引脚。

图3。参考电压连接。数模转换器

8位DAC提供从0V到2.499V的256个输出电压电平(输入/输出关系见表I)。DAC由输入设置字的DAC输入部分控制。字的DAC输入部分在转换周期结束时被选入DAC(图2中的第14个CLK脉冲)。

数字输入

DAC输入0-7

模拟输出

+0.0098伏

法国法郎

表1.DAC输入/输出关系。

DAC输出电压

DAC输出电压的值由ADI字的DAC输入部分确定(位0到7,见图2)。8位DAC有256个可能的输出阶跃,从0V到+2.499V。1LSB的值为0.0098V。

其他数字输入和输出

采样和转换由ADCONV和ADCLK输入控制(见图2)。VECANA01设计用于从ADCLK输入端提供的外部时钟进行操作。这样可以使转换与系统定时同步,从而将瞬态噪声影响降至最低。ADCLK信号可以连续运行,也可以仅在转换序列期间提供。ADBUSY和DATACLK信号是内部生成的,提供这些信号是为了使与微处理器的接口更容易(参见图2和图9)。

开机初始化

当对VECANA01通电时,在第三个周期上传输有效数字数据之前,初始化需要两个转换周期。通电后的第一次转换是用输入设置寄存器的双缓冲输出中的不确定配置值执行的。第二个转换周期将所需值加载到寄存器中。第三个转换使用这些值执行正确的转换,并从每个A/D转换器输出有效的数字数据。

时钟

位置(1)

说明

功能

DAC输入0-7设置DAC输出电压增益选择0-1设置PGA增益输入选择0-2条件确定多路复用器注:(1)见图2,“时钟脉冲参考号”表二。配置参数的说明。

可配置参数包括:PGA增益输入多路复用器和采样保持选择DAC输出电压这些参数的配置信息包含在ADINword中(参见图2)。在进行一次转换时,下一次转换的配置将通过ADIN字加载到缓冲输入设置寄存中。表一、七、八和十显示了有关这些参数的信息。

模数转换器A/D转换器是用开关电容电路实现的12位逐次逼近型。

时钟速率

A/D转换器转换的时钟由ADCLK引脚外部提供。规定精度的典型时钟频率为1.25MHz。这将导致10.4微秒的完整转换周期(S/H采集和a/D转换)。

输入/输出

VECANA01是为双极性输入电压设计的,使用二进制二补数字输出码。每个A/D转换器都有一个可编程增益功能。这会改变转换器的满标度模拟输入范围和模拟分辨率。

差动和共模输入电压

VECANA01设计有从多路复用器输入到A/D转换器输入的全差分信号路径。这样做是为了提供优越的高频噪声抑制。与大多数差分输入半导体器件一样,差分输入电压和共模输入电压的组合存在复合限制。由于大多数模拟输入能够受到可编程增益功能的影响,这一问题变得稍微复杂一些。可能的差动和单端配置如图4a和4b所示。最大差动和共模限制如表3所示。

输入设置

当A/D转换器在一个转换周期内转换和传输其串行数字数据时,接收到一个设置字以用于下一个转换周期。13位字由ADINpin提供(见图1),并存储在缓冲输入设置寄存器中。字的输入选择和增益选择部分被解码并确定多路复用器和pga的状态(参见可配置参数部分)。

输入多路复用器和采样保持选择

对ADIN字的输入选择部分(位10、11和12)(见图2)进行解码,并确定多路开关的打开/关闭条件。这进而确定哪些输入信号连接到采样和保持,以及哪些采样和保持连接到PGAs/adc。

输入信号的符号

VECANA01包含七个比较器,它们获取前七个输入模拟信号的信号。符号比较器的数字输出是信号xu COMP。如果正输入值大于负输入值,则X-COMP输出变为高(逻辑“1”)或反之,X-COMP输出为低(逻辑“0”)(见表四)。

表四、投入产出关系。

图4。(a) 差分信号源。(b) 单端输入。

比较器UúCOMP、VúCOMP和WúCOMP的典型滞回值为10mV。比较器A_1、A_2、B_1和B_2的典型滞后值为50mV。交流电机控制应用通常使用10毫伏磁滞进行相位电流测量,50毫伏磁滞用于定位传感器测量。

超距离识别

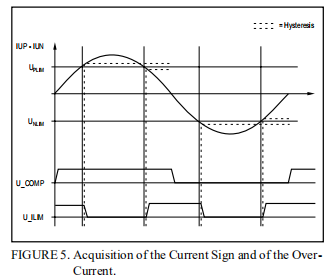

VECANA01还包括用于三个输入信号IU、IV和IW的三个窗口比较器。每个窗口比较器由两个比较器组成,两个比较器监控正量程极限(UPLIM)和负量程极限(UNLIM)的输入值。窗口比较器的输出值通过管脚UúILIM、VúILIM和WúILIM输出。这两个范围限制值与零点对称(UNLIM=–UPLIM),由pin确定

丹。超限整定功能(通常用于整定电流保护值)的图形视图见图5,DAN值将确定固定范围。通常,该引脚连接到DAOUT(DAC输出)。为了能够通过控制值DAC输入字编程范围值,DAC输入是一个8位宽的无符号值(控制数模转换器输出电压(DAOUT))。该D/A转换器的输出电压范围为0V至2.5V(见表I)。

表五:作为功能DAC输入的过电流限制。

如果输入电压超过正范围限制(IXP–IXN>UPLIM)或保持在负范围(IXP–IXN<UNLIM)下,则相应的窗口比较器输出为低(逻辑“0”)(U_ILIM、V_ILIM或W_ILIM)。如果输入值在限制范围内,比较器输出为高(逻辑“1”)。输入信号和输出信号如表六所示。

表六:作为DAC输入函数的极限值。

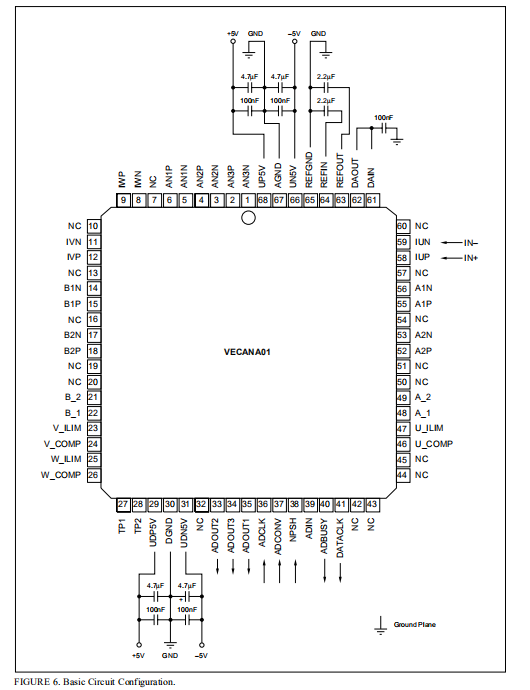

当增益选择为3时,比较器的输入电压范围与A/D转换器相同。比较器的典型磁滞值为50mV。图5显示了输入信号IVP–IUN的U-COMP和U-ILIM输出的逻辑状态。D/A转换器的输出电阻约为10kΩ。输出电压DAOUT应由一个大约100nF的电容器缓冲(见图6),得到的时间常数大约为1ms,通常不会干扰大多数应用。

PGAS/ADC的输入信号

表7显示了输入选择0-2的值与转换的信号之间的关系。

输入选择=7H-同步采样和转换输入信号IU、IV和IW。

图5。电流信号和过电流的采集。

注:(1)操作见表八。

表七。同步采样保持的输入控件。

输入选择=4H、5H、6H-同步采样并转换输入信号A1、B1和AN1。这些代码还会导致SH2和SH4对其输入进行采样。值4H、5H、6H对SH6和SH7的输入有不同的影响(见表八)。

表八。异步采样保持的输入控件。

输入选择=3H-通过SH2转换A2,通过SH4转换B2,和AN2(A2和B2来自在输入选择为4H、5H或6H的前一转换周期中采样的值)。

输入选择=2H-通过SH1转换A2,通过SH3转换B2,和AN2。

图6。基本电路配置。

表九:模拟输入-数字输出关系。

输入选择=1H-输入AN3由ADC3转换。异步采样保持SH6和SH7的输出分别由PGA1/ADC1和PGA2/ADC2转换。注意,SH6和SH7的输入由先前的输入选择值决定(见表VIII)。因此,要正确地转换一个异步采样保持的输出,首先需要使用先前的转换周期选择其输入。此外,只有在接收到ADCONV命令之前NPSH变低时,SH6或SH7的输出才会被转换。

输入选择=0 H-AN3由ADC3转换。PGA1/ADC1和PGA2/ADC2的输入未定义。

PGA增益

PGA增益由ADIN字中的增益选择部分(位8和位9)确定(见图2)。有一个增益输入,为所有三个PGA设置相同的增益。增益值和允许的满标度输入如表X所示。

表X.增益选择信息。

对于通道1和通道2,PGA设置所有三个模拟输入的增益。对于第三信道,PGA只改变IW输入的增益。无论增益选择值如何,输入端AN1、AN2和AN3以1.0V/V的固定增益连接到A/D转换器3。

异步示例保持的转换

说明

注:可编程增益功能适用于ADC1和ADC2的所有三个输入通道。然而,可编程增益功能仅适用于ADC3的第一输入(IW)。其他三个输入(AN1、AN2和AN3)不受增益选择输入的影响。它们以1V/V的固定增益工作,因此具有固定的±2.5V满标度输入范围。

解码输入选择值还可确定哪些输入应用于两个异步控制的样本保持(SH6和SH7)(见表VIII)。输入选择值可选择三个可能的输入之一

四、五或六岁。“无影响”状态表示这些输入选择值对SH6和SH7输入处的多路复用器没有影响。当出现输入选择的“无影响”值之一时,多路复用器将不会改变(即,其条件由“无影响”状态之前存在的输入选择的最后4、5或6值确定)。注意,输入Select=1H分别表示SH6和SH7到PGA1/ADCl和PGA2/ADC2的输出(见表七)。因此,为了正确地转换异步采样信号,首先需要选择具有一个加载/转换周期的输入信号(表VIII中的输入选择等于5或6),然后在随后的转换周期中转换采样保持输出(表VII中的输入选择=4)。

电源

VECANA01要求模拟和数字电源电压为±5V。基板连接到UP5V。模拟和数字电源引脚之间的电压差不允许超过最大值300mV。因此,建议使用图7所示的电路作为电源。模拟和数字电源由一个共同的电源驱动。中间电阻提供去耦功能。本地限流电压调节器从模拟电源电压±UB产生±5V。这保证了进一步降低噪音。二极管负责保护调节和防止极性反转。齐纳二极管可防止从过电压到模拟输入端的过电压。电阻器和电容器的典型值为:

RA≈3Ω

RD≈3Ω

CD≈22μF

钙≈22μF

CB≈100nF

铬≈2.2μF