AD5390点击型号即可查看芯片规格书

特征

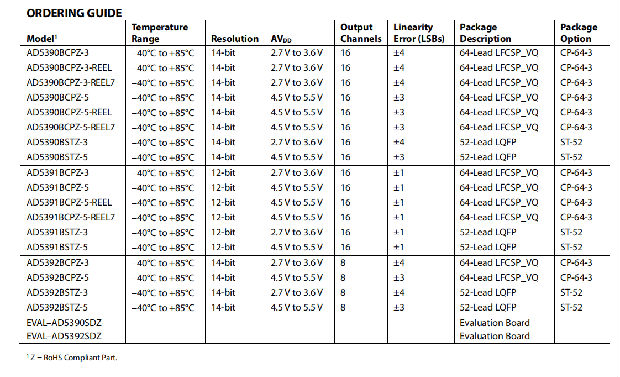

AD5390:16通道,14位电压输出DAC;AD5391:16通道,12位电压输出DAC;AD5392:8通道,14位电压输出DAC;保证单调内联:最大±1 LSB(AD5391);最大±3 LSB(AD5390-5/AD5392-5);最大±4 LSB(AD5390-3/AD5392-3);片上1.25 V/2.5 V,10 ppm/℃基准;温度范围:-40°C至+85°C;轨对轨输出放大器;断电模式包类型:64引线LFCSP(9 mm×9 mm);52引线LQFP(10 mm×10 mm);用户界面;串行SPI-、QSPI-、MICROWIRE-和DSP兼容(具有数据读回功能);I2C兼容接口;综合功能;通道监视器;通过LDAC同步输出更新;清除用户可编程代码的功能;优化转换速率的放大器升压模式;用户可编程的偏移和增益调整;切换模式启用方波生成;热监测仪;坚固的6.5千伏HBM和2千伏FICDM ESD额定值。

应用

仪表与工业控制;功率放大器控制;电平设置(ATE);控制系统;微机电系统(MEMs);可变光衰减器;光收发器(MSA 300,XFP)。

一般说明

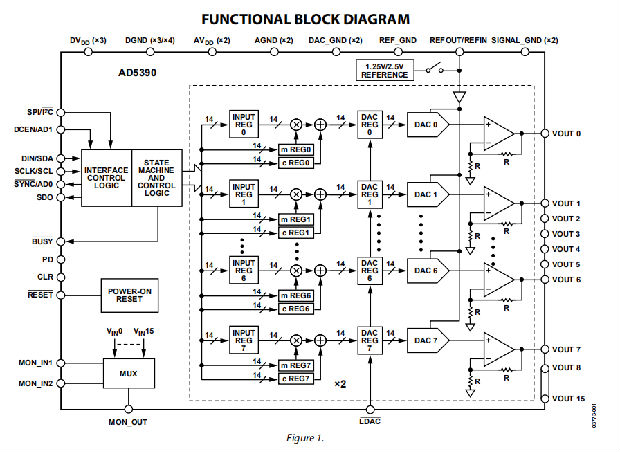

AD5390/AD5391分别是完整的单电源、16通道、14位和12位DAC。AD5392是一个完整的单电源、8通道、14位DAC。这些设备可用于64线LFCSP或52线LQFP。所有通道都有一个带轨对轨操作的片内输出放大器。所有设备包括一个内部1.25/2.5V、10ppm/℃基准、一个将模拟输出多路传输到公共MON U OUT引脚以进行外部监控的片上通道监控功能,以及一个优化输出放大器转换速率的输出放大器升压模式。

AD5390/AD5391/AD5392包含一个3线串行接口,接口速度超过30 MHz,与SPI®和QSPI兼容8482;,微丝™,以及支持400khz数据传输速率的DSP接口标准和IC兼容接口。

输入寄存器后跟DAC寄存器提供双缓冲,允许DAC输出使用LDAC独立或同时更新输入。每个通道都有一个可编程的增益和偏移调整寄存器,允许用户完全校准任何DAC通道。

每个通道的功耗通常为0.25毫安。

术语

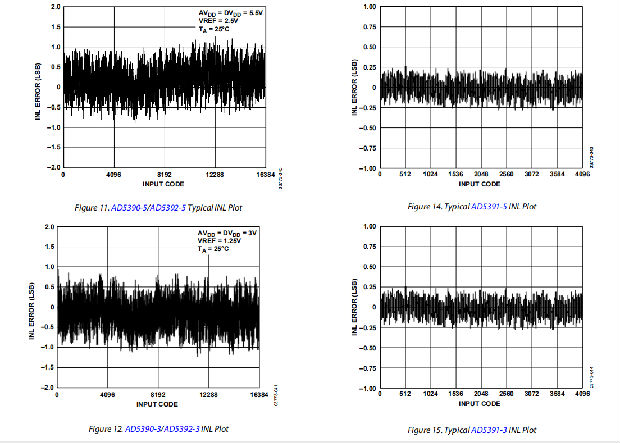

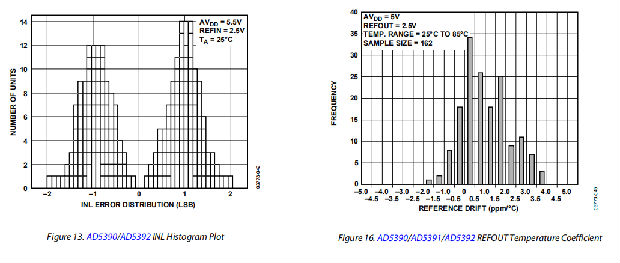

相对精度或终点线性(INL)对通过DAC传递函数端点的直线的最大偏差的测量。它是在调整零标度误差和满标度误差后测量的,用最低有效位(lsb)表示。

微分非线性(DNL)

任何两个相邻码之间的测量变化和理想1lsb变化之间的差异。指定的最大值为1 LSB的微分非线性确保了单调性。

零刻度误差

当所有0都加载到DAC寄存器中时,DAC输出电压中的错误。理想情况下,将所有0加载到DAC,m=所有1,c=2,VOUT(=0 V)。n个−1零刻度)零标度误差是测量VOUT(实际)和VOUT(理想)之间的差值,单位为mV。这主要是由输出放大器的失调引起的。

偏移误差

在传递函数的线性区域中,用mV表示的VOUT(实际)和VOUT(理想)之间的差的度量。在AD5390-5/AD5391-5/AD5392-5上测量偏移误差,其中代码32加载在DAC寄存器中,代码64加载在AD5390-3/AD5391-3/AD5392-3上的DAC寄存器中。

增益误差

DAC传输特性与理想值的斜率偏差,用DAC输出空载时的%FSR表示。增益误差在输出范围的线性区域中指定,在VOUT=10 mV和VOUT=AV−50 mV之间。

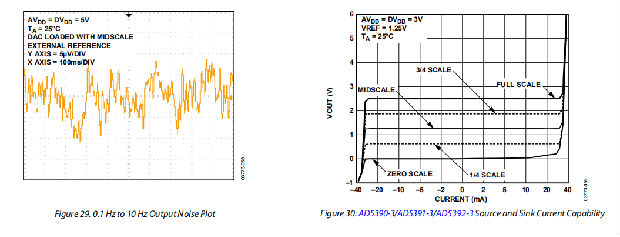

直流串扰

一个DAC在中刻度时输出电平的直流变化,以响应全刻度代码(全0到全1,反之亦然)和所有其他DAC的输出变化。它用LSB表示。

直流输出阻抗

有效输出源电阻。它以封装铅电阻为主。

输出电压稳定时间

一个数模转换器的输出在四分之一到四分之一的满标度输入变化中稳定到指定水平所需的时间。它是从繁忙的上升边缘来衡量的。

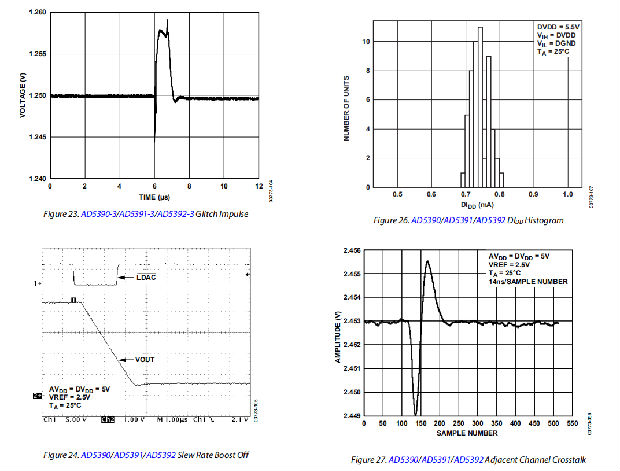

数模故障能量

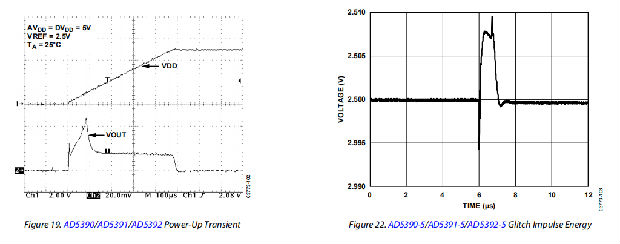

在主要代码转换时注入模拟输出的能量量。它被指定为nV-s中的故障区域。通过在0x1FF和0x2000之间切换DAC寄存器数据来测量。

DAC到DAC串扰

由于另一个数模转换器的数字变化和随后的模拟输出变化而在一个数模转换器的输出端出现的故障脉冲。受害信道加载了中尺度,并且在nV-s中指定了DAC到DAC的串扰。

数字串扰

由于另一个转换器的DAC寄存器代码的变化而传输到一个转换器输出的故障脉冲被定义为数字串扰,并在nV-s中指定。

数字馈通

当未选择设备时,设备数字输入上的高频逻辑活动可以跨设备和通过设备电容耦合,以在VOUT管脚上显示为噪声。它也可以沿着电源线和地线连接。这种噪声是数字馈通。

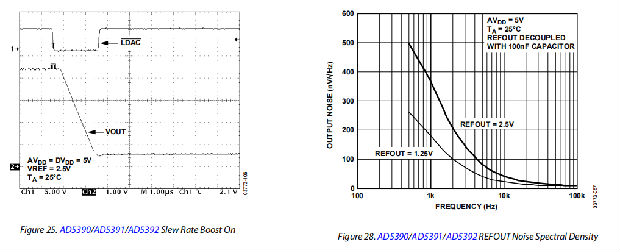

输出噪声谱密度

这是测量内部产生的随机噪声。随机噪声的特征是频谱密度(每√Hz的电压)。它是通过将所有DAC加载到中刻度并在输出端测量噪声来测量的。它以nV/(Hz)为单位,在10khz的1hz带宽上测量。

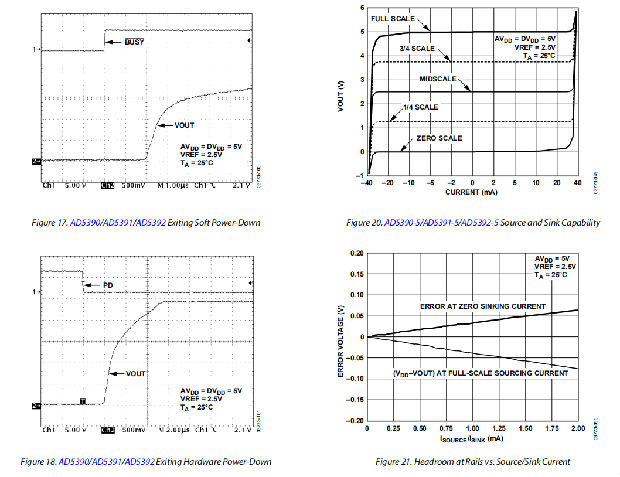

典型性能特征

功能描述

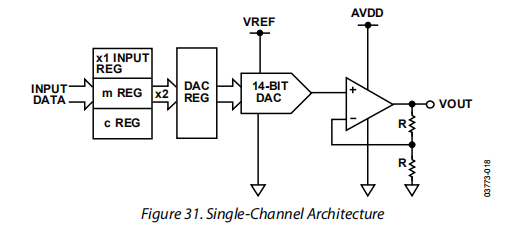

DAC体系结构

AD5390/AD5391是完整的单电源、16通道、电压输出DAC,分别提供14位和12位的分辨率。AD5392是一个完整的单电源、8通道、电压输出DAC,提供14位分辨率。所有设备均采用64线LFCSP和52线LQFP,并具有串行接口。该系列包括一个内部可选择的1.25 V/2.5 V、10 ppm/℃参考,可用于驱动缓冲参考输入(或者,可使用外部参考驱动这些输入)。所有通道都有一个带轨对轨输出的片上输出放大器,能够驱动一个5 kΩ负载,并具有200 pF电容。单个DAC通道的结构由12位和14位电阻串DAC和以2增益工作的输出缓冲放大器组成。这种电阻串结构保证了DAC的单调性。加载到DAC寄存器的12位和14位二进制数字代码决定了在输入到输出放大器之前电压在串上的哪个节点被抽头。这些设备上的每个通道都包含独立的偏移和增益控制寄存器,允许用户对偏移和增益进行数字微调。

这些寄存器允许用户使用内部m和c寄存器来校准整个信号链(包括DAC)中的错误,这些寄存器保存了校正因子。所有通道都是双缓冲的,允许使用LDAC管脚同步更新所有通道。图31显示了AD5390/AD5391/AD5392上单个通道的框图。

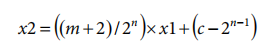

每个DAC的数字输入传递函数可以表示为:

其中:x2是加载到电阻串DAC的数据字;x1是写入DAC输入的12位和14位数据字登记;m是12位和14位的增益系数(默认为全部0x3FFE AD5390/AD5392和AD5391上的0xFFE);LSB增益系数为零;n=DAC分辨率(AD5390/AD5392和对于AD5391,n=12);c是12位和14位偏移系数(默认值为0x2000开AD5391上的AD5390/AD5392和0x800)。

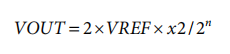

这些设备的完整传输功能可以是表示为:

其中:x2是加载到电阻串DAC的数据字。

VREF是施加到REFIN/REFOUT引脚的参考电压在使用外部参考时的DAC上(对于指定的对AD5390-5/AD5391-5/AD5392-5和1.25 V的性能在AD5390-3/AD5391-3/AD5392-3上)。

数据解码

AD5390/AD5392

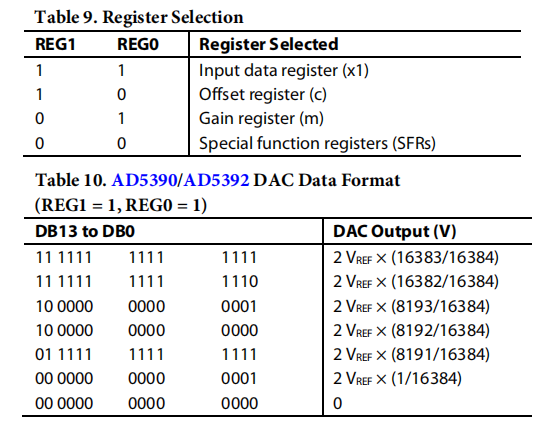

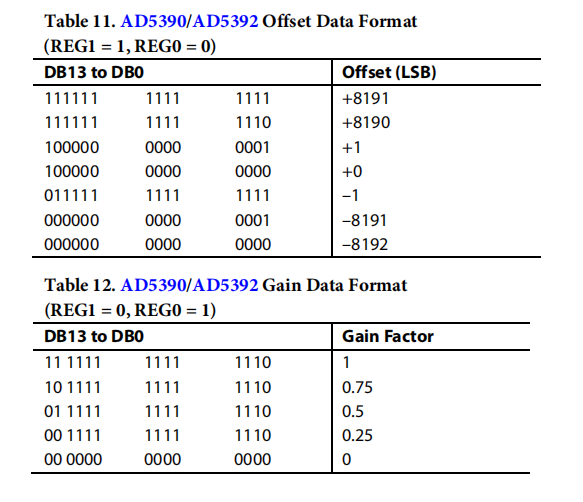

AD5390/AD5392包含一个内部14位数据总线。根据加载到输入串行寄存器的REG1和REG0位的数据对输入数据进行解码。如表9所示。

串行输入寄存器的数据被加载到寻址DAC输入寄存器、偏移(c)寄存器或增益(m)寄存器中。格式数据、偏移量(c)和增益(m)寄存器内容如表10至表12所示。

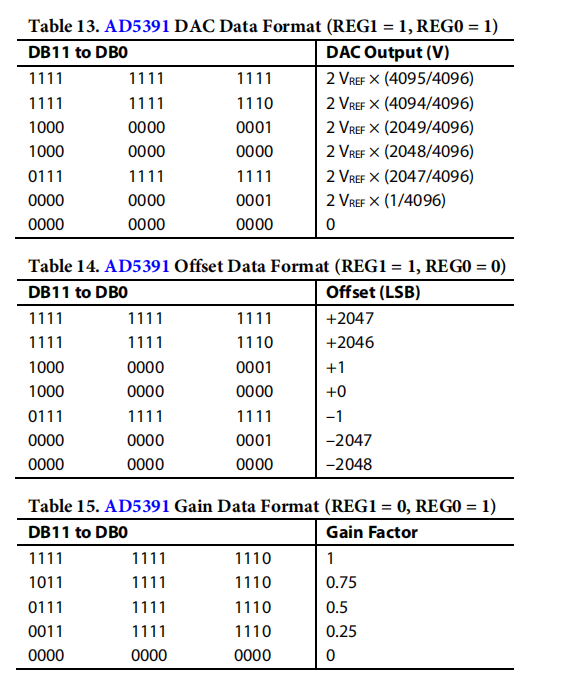

AD5391

AD5391包含一个内部12位数据总线。根据加载到输入串行寄存器的REG1和REG0位的值,对输入数据进行解码。串行输入寄存器的输入数据被加载到寻址DAC输入寄存器、偏移(c)寄存器或增益(m)寄存器中。格式数据、偏移量(c)和增益(m)寄存器内容如表13至表15所示。

接口

AD5390/AD5391/AD5392包含一个串行接口,可编程为与DSP、SPI和Microwire兼容,或与IC兼容。SPI/IC引脚用于选择接口模式。

为了最小化设备的功耗和片上数字噪声,接口只有在设备被写入时,即在同步的下降沿上,才完全通电。

与DSP、SPI和MICROWIRE兼容的串行接口

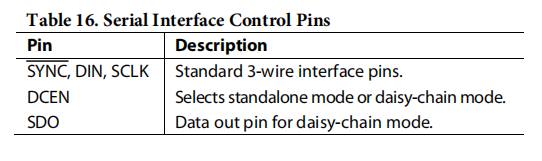

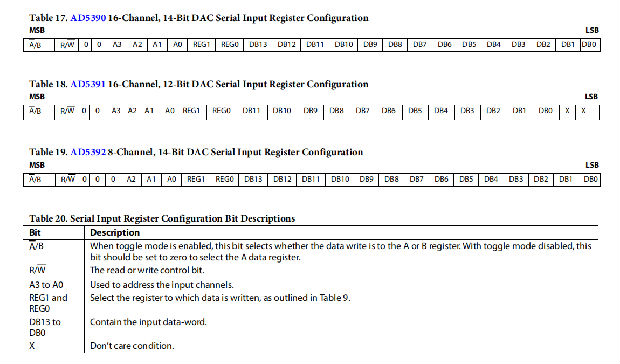

串行接口可在独立模式下至少使用三根电线或在菊花链模式下使用四根电线进行操作。菊花链允许许多设备级联在一起以增加系统信道数。SPI/IC管脚与逻辑1管脚相连,以配置此操作模式。串行接口控制引脚如表16所示。

图2到图4显示了在独立和菊花链模式下串行写入AD5390/AD5391/AD5392的时序图。串行接口的24位数据字格式如表17至表19所示。位的描述见表20。

单独模式

通过连接菊花链启用(DCEN)引脚低位,启用独立模式。串行接口可与连续和非连续串行时钟一起工作。第一次跌倒同步边缘启动写入周期并重置计数器,该计数器计算串行时钟的数量,以确保将正确的位数移位到串行移位寄存器中。任何同步时的其他边(下降边除外)将被忽略,直到24位进入时钟。一旦移入24位,SCLK将被忽略。再进行一次串行传输,计数器必须通过同步下降沿重置。

菊花链模式

对于包含多个设备的系统,可以使用SDO管脚将这些设备串接在一起。这种菊花链模式可用于系统诊断和减少串行接口线的数量。

通过连接DCEN引脚high,菊花链模式启用。同步的第一个下降沿开始写入循环。SCLK连续应用于输入移位寄存器当同步度低时。如果应用了超过24个时钟脉冲,则数据会从移位寄存器中波动出来,并出现在SDO线上。此数据在SCLK的上升沿上计时,在下降沿上有效。通过将第一个设备的SDO连接到链中下一个设备的DIN输入,构建了一个多设备接口。对于系统中的每个设备,需要24个时钟脉冲。因此,时钟周期的总数必须等于24N,其中N是链中AD5390/AD5391/AD5392设备的总数。

当所有设备的串行传输完成时,同步将处于高位。这将锁定菊花链中每个设备中的输入数据,并防止任何进一步的数据进入输入移位寄存器。

如果在24个时钟进入该部分之前进行高同步,则将其视为坏帧,并丢弃数据。串行时钟可以是连续时钟,也可以是门控时钟。一个只有当同步可以保持在正确的时钟周期数较低时,才能使用连续SCLK源。在门控时钟模式中,一种突发时钟,包含准确的时钟周期数必须使用并在最后一个时钟后进行高同步以锁定数据。

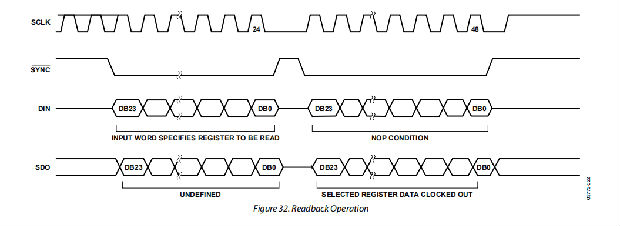

回读模式

通过在串行输入寄存器写入序列中设置R/W位=1来调用回读模式。当R/W=1时,位A3到位A0与位REG1和REG0关联,选择要读取的寄存器。写序列中剩余的数据位是不关心的位。在下一次SPI写入期间,SDO输出上出现的数据包含来自先前寻址寄存器的数据。对于单个寄存器的读取,NOP命令可用于对SDO上所选寄存器的数据进行时钟输出。

图32中的回读图显示了回读序列。例如,要读回AD5390/AD5391/AD5392上信道0的m寄存器,应执行以下顺序:首先,将0x404XXX写入AD5390/AD5391/AD5392输入寄存器。这将AD5390/AD5391/AD5392配置为读取模式,并选择通道0的m寄存器。注意,所有的数据位,从DB13到DB0,都是无关紧要的位。

接下来是第二次写入、NOP条件和0x000000。在该写入过程中,来自m寄存器的数据在DOUT行上打卡,即打卡的数据包含来自m寄存器的数据(从位DB13到位DB0),并且前10位包含先前写入的地址信息。在回读中模式下,同步信号必须帧数据。数据在SCLK上升沿上计时,在SCLK信号下降沿上有效。如果SCLK在回读的写操作和读操作之间高空闲,则第一位数据将被打卡在同步下降的边缘。

I2C串行接口

AD5390/AD5391/AD5392具有集成电路兼容的2线接口,由串行数据线(SDA)和串行时钟线(SCL)组成。SDA和SCL以高达400khz的速率促进dac和主机之间的通信。图6显示了2线接口时序图。

当通过将SPI/IC管脚配置为逻辑0来选择IC工作模式时,该设备作为从设备连接到IC总线,即该设备不产生时钟。AD5390/AD5391/AD5392具有7位从机地址10101(AD1)(AD0)。五个msb是硬编码的,两个lsb由AD1和AD0管脚的状态决定。AD1和AD0引脚的硬件配置工具允许在总线上配置其中四个设备。

I2C数据传输

在每个SCL时钟周期中传输一个数据位。在SCL时钟脉冲的高周期内,SDA上的数据必须保持稳定。SCL高时SDA的变化是配置启动和停止条件的控制信号。当IC总线不忙时,SDA和SCL都被外部上拉电阻器拉高。

启动和停止条件

主设备通过发出启动条件来启动通信。启动条件是在SCL高的SDA上从高到低的转换。停止条件是SDA上从低到高的转换,而SCL是高的。来自主设备的启动条件向AD5390/AD5391/AD5392发送开始传输的信号。停车条件使公共汽车腾空。如果生成的是重复启动条件(Sr)而不是停止条件,则总线将保持活动状态。

重复启动条件

重复启动(Sr)条件可指示总线上数据方向的变化。当总线主设备正在写入多个IC设备并且不想放弃总线控制时,可以使用Sr。

确认位(ACK)

确认位(ACK)是附加到任何8位数据字的第9位。接收设备总是生成ACK。AD5390/AD5391/AD5392设备在接收地址或数据时通过在第九个时钟周期内拉低SDA来生成ACK。

监视ACK允许检测不成功的数据传输。如果接收设备正忙或发生系统故障,则会发生不成功的数据传输。如果数据传输不成功,总线主机应重新尝试通信。

AD5390/AD5391/AD5392秒lave地址

总线主设备通过发出先有7位从设备地址的启动条件来启动与从设备的通信。空闲时,AD5390/AD5391/AD5392设备等待启动条件,然后等待从机地址。地址字的LSB是读/写(R/W)比特。AD5390/AD5391/AD5392设备仅为接收设备,与它们通信时R/W=0。在接收到正确的地址10101(AD1)(AD0)之后,AD5390/AD5391/AD5392通过将SDA拉低一个时钟周期来发出ACK。AD5390/AD5391/AD5392具有由AD1和AD0位确定的四个用户可编程地址。

I2C写入操作

有三种特定模式可将数据写入AD5390/AD5391/AD5392 DAC。

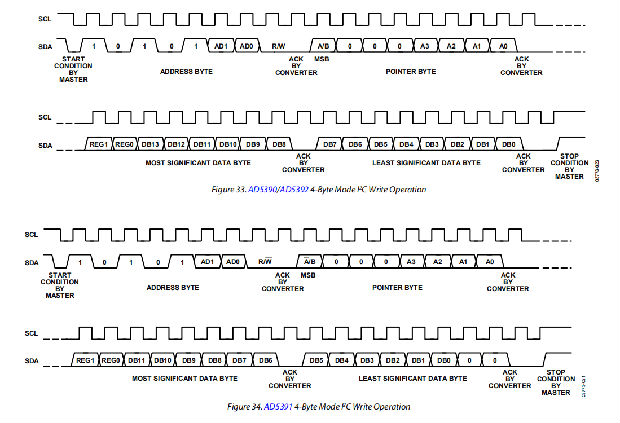

4字节模式

当写入AD5390/AD5391/AD5392 DAC时,开始一个地址字节(R/W=0),在此之后,DAC确认它准备通过拉低SDA来接收数据。地址字节后接指针字节。这个寻址DAC中要寻址的特定信道,DAC也会对其进行确认。地址位A3到A0表示AD5390/AD5391上的所有信道。地址位A2到A0寻址AD5392上的所有信道。地址位A3是AD5392上的零。然后将两个字节的数据写入DAC,如图33所示。随后出现停止条件。这允许用户在任何时候更新AD5390/AD5391/AD5392中的单个通道,并且需要从主机传输四个字节的数据。

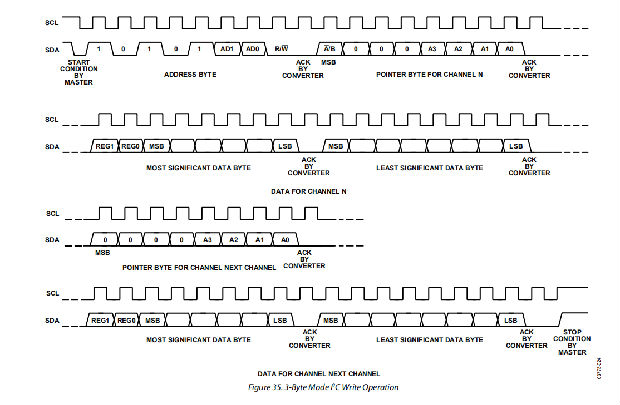

3字节模式

3字节模式允许用户在写入序列中更新多个信道,而无需每次写入设备地址字节。设备地址字节只需要一次,随后的通道更新需要指针字节和数据字节。在3字节模式下,用户从地址字节开始(R/W=0)之后,DAC确认它准备通过拉低SDA来接收数据。地址字节后接指针字节;这表示要寻址的DAC中的特定通道,DAC也会对其进行确认。地址位A3到A0表示AD5390上的所有信道/AD5391。地址位A2到A0表示AD5392。地址位A3是AD5392上的零。接下来是两个数据字节。REG1和REG0决定要更新的寄存器。

如果在数据字节之后没有发送停止条件,则可以通过发送一个新的指针字节,然后再发送数据字节来更新另一个通道。这种模式只需要发送三个字节来更新设备初始寻址后的任何信道,并减少更新AD5390/AD5391/AD5392信道时的软件开销。停止条件随时退出此模式。图35显示了一个典型的配置。

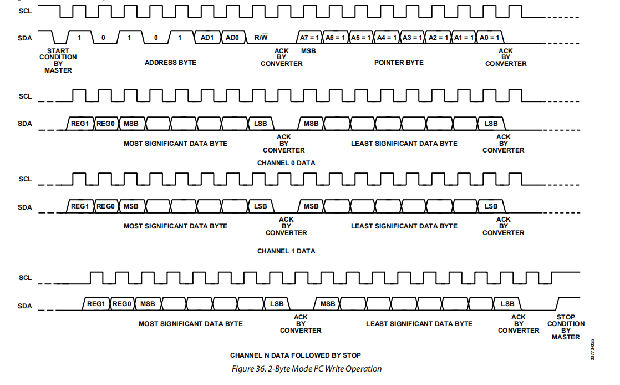

2字节模式

2字节模式允许用户在初始化此模式后按顺序更新频道。设备地址字节只需要一次,地址指针配置为自动递增或突发模式。

用户必须以地址字节(R/W=0)开头,在该字节之后,DAC确认它准备通过拉低SDA来接收数据。地址字节后面跟着一个特定的指针字节(0xFF),它启动突发操作模式。地址指针初始化为通道0,指针后面的数据加载到通道0。地址指针自动递增到下一个地址。

数据字节中的REG0和REG1位决定要更新的寄存器。在这种模式下,初始化之后,只需要两个数据字节即可更新通道。通道地址从地址0自动递增到最终地址,然后返回到正常的3字节操作模式。此模式允许将数据传输到一个块中的所有通道,并减少配置所有通道时的软件开销。停止条件随时退出此模式。在2字节模式下不支持切换操作模式。图36显示了一个典型的配置。

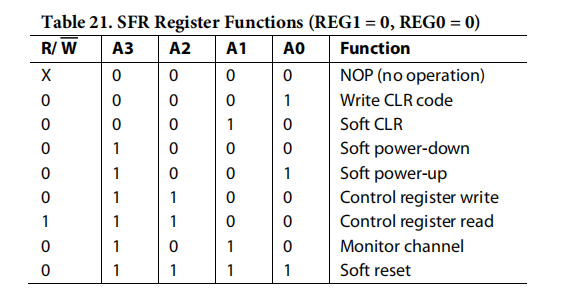

AD5390/AD5391/AD5392片上专用

功能寄存器

AD5390/AD5391/AD5392包含许多特殊功能寄存器(SFR),如表21所示。sfr用REG1=0和REG0=0寻址,并使用地址位A3到位A0解码。

SFR命令

NOP(无操作)

REG1=REG0=0,A3至A0=0000

不执行任何操作,但在回读模式下可用于在SDO上打卡以进行诊断。在NOP操作期间,BUSY输出低。

编写CLR代码

REG1=REG0=0,A3至A0=0001

DB13到DB0=包含CLR数据

将CLR行调低或执行软清除功能,使用用户可配置的CLR寄存器中包含的数据加载DAC寄存器的内容,并相应地将VOUT 0设置为VOUT 15。这不仅对于在清晰的条件下设置特定的输出电压非常有用,而且对于校准也非常有用。对于校准,用户可以将满标度或零标度加载到清除代码寄存器,然后发出硬件或软件清除命令,将此代码加载到所有DAC,从而消除对所有DAC进行单独写入的需要。开机时默认为全零。

软相干激光雷达

REG1=REG0=0,A3至A0=0010

DB13到DB0=不在乎

执行此指令执行CLR,其功能与外部CLR管脚提供的相同。DAC输出与CLR代码寄存器中的数据一起加载。在AD5390/AD5391上完全执行软CLR所需的时间为20微秒,在AD5392上为15微秒。它由忙碌的低时间表示。

软电源关闭

REG1=REG0=0,A3至A0=1000

DB13到DB0=不在乎

执行此指令将执行全局断电,这将使所有通道进入低功耗模式,将模拟电流最大减少到1微安,将数字功耗最大减少到20微安。在掉电模式下,输出放大器可以配置为高阻抗输出,也可以为接地提供100 kΩ负载。所有内部寄存器的内容在断电模式下保留。

软启动

REG1=REG0=0,A3至A0=1001

DB13到DB0=不在乎

此指令用于给输出放大器和内部参考信号通电。退出掉电模式的时间为8微秒。硬件掉电和软件功能在数字或功能中进行内部组合。

软复位

REG1=REG0=0,A5至A0=001111

DB13到DB0=不在乎

此指令用于实现软件重置。所有内部寄存器都重置为其默认值,即满标度为m,零标度为c。清除DAC寄存器的内容,将所有模拟输出设置为0 V。软复位激活时间最长为135微秒。仅在AD5390/AD5391/AD5392未处于断电模式时执行软复位。

监视通道

REG1=REG0=0,A3至A0=01010

DB13 to DB8=包含要寻址的通道的数据

监控

所有设备上都提供监控功能。此功能包括通过接口寻址的多路复用器,允许将任何通道输出路由到MON U OUT引脚,以便使用外部ADC进行监控。除了监视所有输出通道外,还提供两个外部输入,允许用户监视AD5390/AD5391/AD5392外部的信号。在将任何通道路由到MON U OUT引脚之前,必须在控制寄存器中启用通道监视器功能。在AD5390和AD5392 14位部件上,DB13到DB8包含被监视通道的通道地址。在AD5391的12位部分,DB11到DB6包含要监视的通道的通道地址。选择地址63表示MON U OUT引脚。

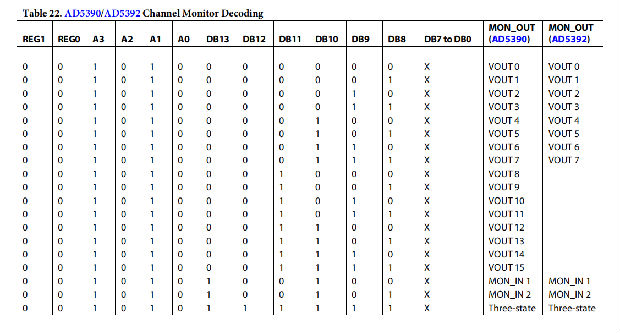

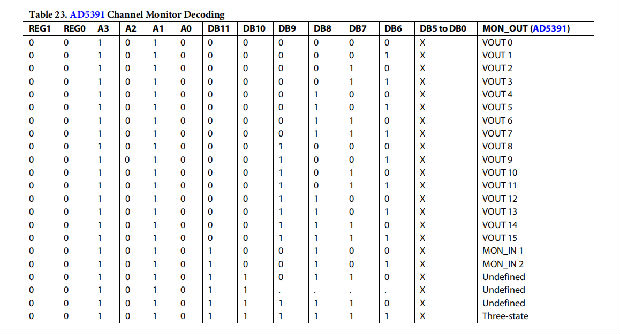

AD5390/AD5392的信道监视器解码如表22所示,AD5391的监视器解码如表23所示。

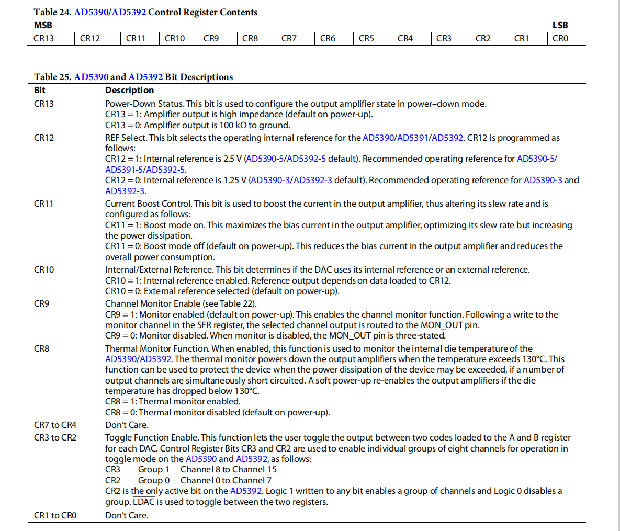

控制寄存器写入

表24显示了AD5390和AD5392的控制寄存器内容。表25提供了位描述。注意,REG1=REG0=0,A3到A0=1100,DB13到DB0包含控制寄存器数据。

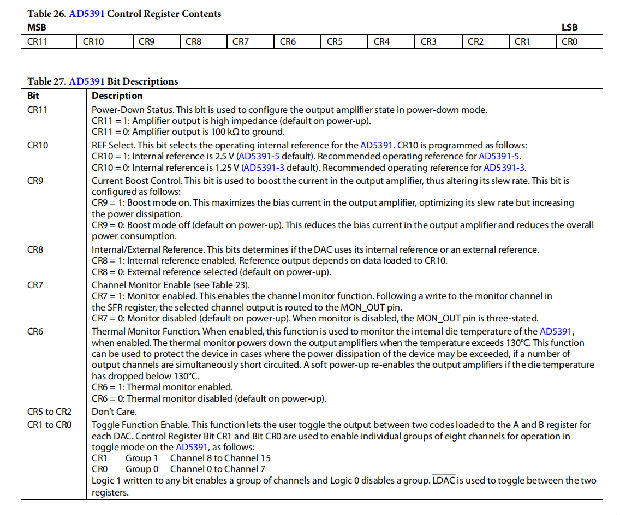

表26显示了AD5391的控制寄存器内容。表27提供了位描述。注意,REG1=REG0=0,A3到A0=1100,DB13到DB0包含控制寄存器数据。

硬件功能

复位功能

将重置行调低可重置所有内部内容注册到其上电重置状态。复位是一个负边缘敏感输入。默认值与满标度时的m对应,并且c为零刻度。所有DAC寄存器的内容通过将输出设置为0 V。此序列最多需要270μs。复位的下降沿启动复位过程。忙去持续时间低,复位完成后返回高。当忙时很低,所有接口都被禁用,所有LDAC忽略脉冲。当BUSY返回高位时,部件继续正常运行,复位引脚的状态被忽略直到检测到下一个下降沿。仅执行硬件AD5390/AD5391/AD5392未断电时复位模式。

异步清除功能

CLR为负边缘触发,并且忙将变低CLR执行的持续时间。降低CLR线路将DAC寄存器的内容清除为包含在用户可配置的CLR寄存器并设置模拟输出因此。此功能可用于系统校准将零刻度和满刻度一起加载到所有通道。这个在AD5390/AD5391上,CLR的执行时间为20μs,并且AD5392上为15μs。

忙和LDAC功能

BUSY是一个数字CMOS输出,指示AD5390/AD5391/AD5392设备。忙碌在x2数据的内部计算。如果在忙是低,此事件被存储。用户可以保持LDAC输入永远低,在这种情况下,DAC输出忙碌过后立即更新。忙也会变低在上电复位期间和检测到下降沿打开时复位引脚。在此期间,所有接口都被禁用,并且忽略LDAC上的任何事件。

AD5390/AD5391/AD5392包含一个额外功能其中,除非其x2寄存器具有自上次LDAC降低以来一直写信给。通常,当LDAC降低时,DAC寄存器为充满了x2寄存器的内容。然而,这些只有当x2数据改变时,设备才会更新DAC寄存器,从而消除不必要的数字串扰。

上电复位

AD5390/AD5391/AD5392包含开机复位发电机和状态机。上电复位将所有寄存器重置为预定义状态,模拟输出为配置为高阻抗输出。在上电复位过程中,忙碌引脚变低,防止数据写入装置。

断电

AD5390/AD5391/AD5392包含一个全局掉电功能,将所有通道置于低功耗模式,将模拟功耗最大降低到1μa,将数字功耗最大降低到20μa。在断电模式下,输出放大器可以配置为高阻抗输出或提供100 kΩ的负载接地。所有内部寄存器的内容在断电模式下保留。当退出掉电时,放大器的稳定时间在输出稳定到其正确值之前流逝。

微处理器接口

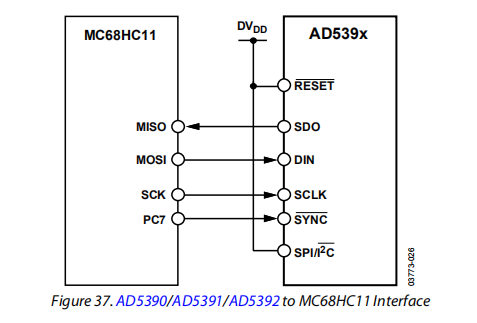

AD5390/AD5391/AD5392吨o MC68HC11型

MC68HC11上的串行外围接口(SPI)配置为主模式(MSTR=1),时钟极性位(CPOL)=0,时钟相位位(CPHA)=1。SPI通过写入SPI控制寄存器(SPCR)进行配置-请参阅68HC11用户手册。MC68HC11的SCK驱动AD5390/AD5391/AD5392的SCLK,MOSI输出驱动AD5390/AD5391/AD5392的串行数据线(DIN),MISO输入由D驱动。同步信号由端口线(PC7)导出。当数据被发送到AD5390/AD5391/AD5392时,同步线被取低(PC7)。显示在MOSI输出上的数据在SCK下降沿上是有效的。来自MC8HC11的串行数据以8位字节传输,在传输周期中只有8个下降的时钟边缘。

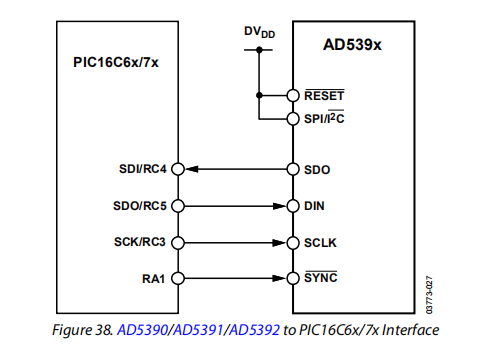

AD5390/AD5391/AD5392吨o图片16C6X/7x

PIC16C6x/7x同步串行端口(SSP)被配置为时钟极性位为0的SPI主机。这是通过写入同步串行端口控制寄存器(SSPCON)来完成的—请参阅PIC16/17微控制器用户手册。

在图38中,I/O端口RA1用于脉冲同步并启用AD5390/AD5391/AD5392的串行端口。该微控制器在每个串行传输操作期间仅传输8位数据;因此,根据模式的不同,需要三个连续的读/写操作。图38显示了连接图。

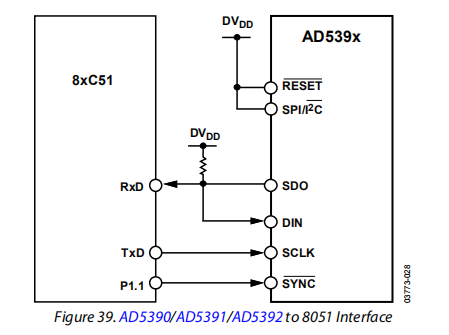

AD5390/AD5391/AD5392至8051

AD5390/AD5391/AD5392需要与串行数据同步的时钟。因此,8051串行接口必须在模式0下操作。在此模式下,串行数据通过RxD进入和退出,并在TxD上输出移位时钟。图39显示了8051如何连接到AD5390/AD5391/AD5392。因为AD5390/AD5391/AD5392将移位时钟上升沿上的数据移出,并将数据锁定在下降沿上,所以移位时钟必须反转。AD5390/AD5391/AD5392首先要求其数据具有MSB。因为8051首先输出LSB,所以发送例程必须考虑到这一点。

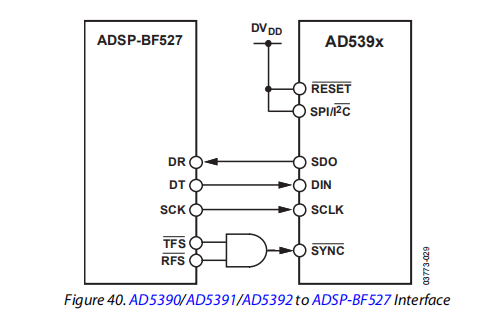

AD5390/AD5391/AD5392至ADSP-BF527

图40显示了AD5390/AD5391/AD5392和ADSP-BF527之间的串行接口。ADSP-BF527应设置为在运动传输交替帧模式下工作。ADSP-BF527 SPORT通过运动控制寄存器编程,应配置如下:内部时钟操作、主动低帧和16位字长。在启用运动后,通过将一个字写入Tx寄存器来启动传输。

应用程序信息

电源去耦

在任何精度很重要的电路中,仔细考虑电源和接地回路布局有助于确保额定性能。安装AD5390/AD5391/AD5392的印刷电路板的设计应使模拟和数字部分分开并限制在电路板的某些区域。如果AD5390/AD5391/AD5392位于多个设备需要AGND到DGND连接的系统中,则该连接应仅在一个点上进行。星形接地点应尽可能靠近设备。

对于带有多个引脚(AV、AVCC)的电源,建议将这些引脚连接在一起。AD5390/AD5391/AD5392应具有10μF并联的充足电源旁路,且每个电源上的0.1μF应尽可能靠近封装,理想情况下应正好对着设备。10μF电容器为钽珠型。0.1μF电容器应具有低有效串联电阻(ESR)和有效串联电感(ESI),例如提供高频低阻抗接地路径的普通陶瓷类型,以处理内部逻辑开关引起的瞬态电流。

AD5390/AD5391/AD5392的电源线应使用尽可能大的迹线,以提供低阻抗路径,并减少故障对电源线的影响。时钟等快速开关信号应使用数字接地屏蔽,以避免将噪声辐射到电路板的其他部分,且不得在参考输入附近运行。在DIN线和SCLK线之间布线的地线有助于减少它们之间的串扰(多层板上不需要,因为有一个单独的接地平面,但将这些线分开有助于减少串扰)。

避免数字和模拟信号交叉。板的相对侧上的痕迹应彼此成直角。这减少了通过电路板的馈通效应。到目前为止,微条技术是最好的,但双面板并不总是可行的。在这种技术中,电路板的组件侧专用于接地平面,而信号线则放置在焊接侧。

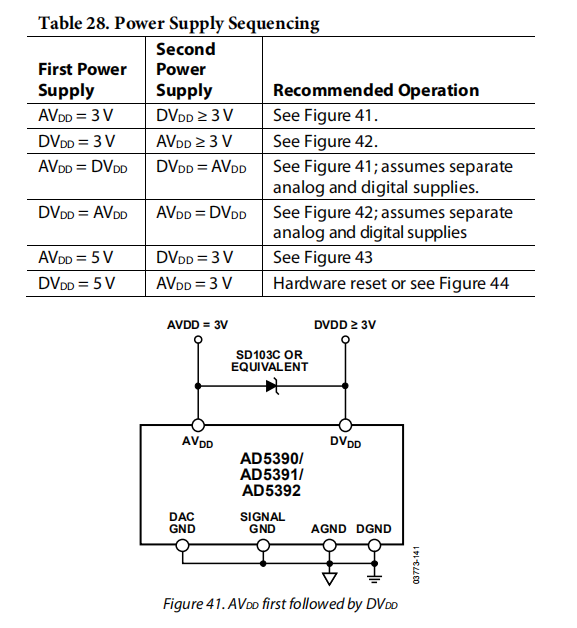

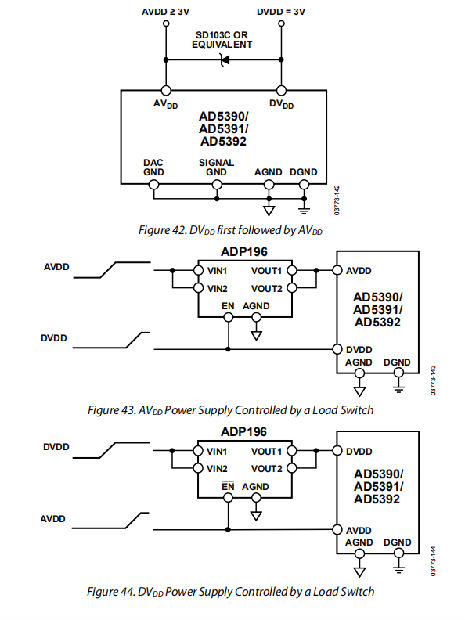

电源顺序

为了正确操作,请先使用DVD光碟,然后同时使用AVDD或在DVD光碟10毫秒内使用。这可确保通电复位电路将寄存器设置为其默认值,并将模拟输出保持在0 V,直到发生有效的写入操作。当AVDD不能在DVDD的10 ms内应用时,发出硬件重置。这将触发上电复位电路并加载默认寄存器值。在初始电源具有与第二电源相同或更低的电压的情况下,可以使用肖特基二极管临时供电,直到第二电源接通。表28列出了电源顺序和推荐的二极管连接。或者,可以使用诸如ADP196的负载开关来延迟第一电源,直到第二电源接通。图43显示了使用ADP196的典型配置。在这种情况下,首先应用AV。该电压不会出现在AD5390/AD5391/AD5392的AVDD引脚上,直到应用DVD并使EN引脚升高。结果表明,AVDD和DVDD同时适用于AD5390/AD5391/AD5392。

典型配置电路

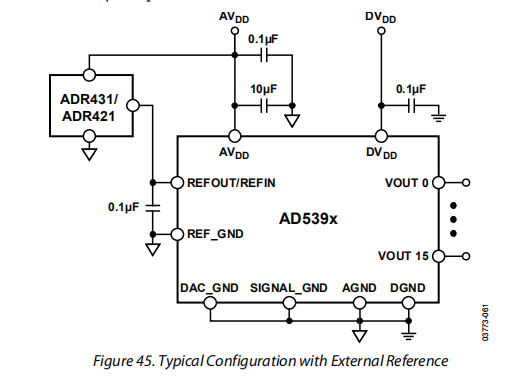

图45显示了AD5390/AD5391/AD5392与外部引用一起使用时的典型配置。在所示电路中,所有a GND、SIGNAL-GND和DAC-GND引脚都连接到一个公共AGND。AGND和DGND在AD5390/AD5391/AD5392设备上连接在一起。通电时,AD5390/AD5391/AD5392默认为外部参考操作。所有AV线连接在一起,由同一个5V电源驱动。建议使用0.1μF陶瓷和10μF钽电容器在靠近装置的地方进行解耦。在该应用中,AD5390-5/AD5391-5/AD5392-5的参考是从ADR421或ADR431 2.5 V参考外部提供的。

适用于AD5390-3/AD5391-3/AD5392-3的外部参考包括ADR280 1.2 V参考。应使用0.1μF电容器在装置的重新输出/重新输入引脚处断开基准。

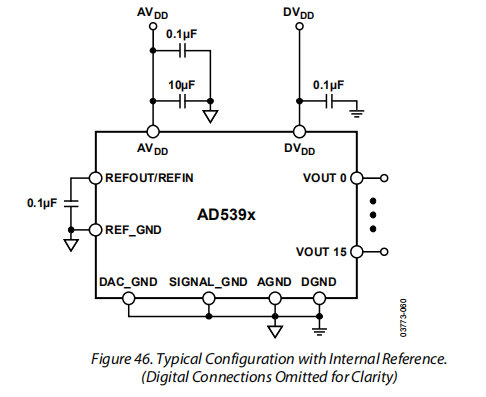

图46显示了使用内部引用时的典型配置。通电时,AD5390/AD5391/AD5392默认为外部引用;因此,需要通过写入AD5390/AD5391/AD5392控制寄存器来配置和打开内部引用。在AD5390/AD5392上,控制寄存器位CR12允许用户选择参考电压;位CR10用于选择内部参考电压。建议在AV=5V时使用2.5V参考电压,在AVDD=3V时使用1.25V参考电压。在AD5391上,控制寄存器位CR10允许用户选择参考电压;位CR8用于选择内部参考电压。

AD5390/AD5391/AD5392包含一个内部通电复位电路,具有10毫秒的断电时间。如果电源斜坡速率超过10 ms,则用户应在初始化过程中重置AD5390/AD5391/AD5392,以确保校准数据正确加载到设备中。

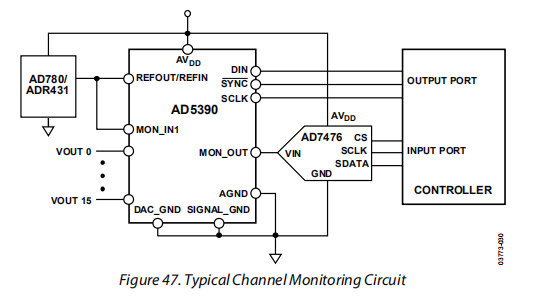

AD5390/AD5391/AD5392监视功能

AD5390包含通道监视器功能,该功能由通过接口寻址的多路复用器组成,允许将任何通道输出路由到此管脚,以便使用外部ADC进行监视。在将任何通道路由到MON U OUT引脚之前,必须在控制寄存器中启用通道监视器功能。

表22和表23包含将AD5390、AD5391和AD5392上的任何信道路由到MON U OUT引脚所需的解码信息。选择信道地址63三个状态的MON_OUT pin。AD5390/AD5391/AD5392还包含两个名为MON_IN 1和MON_IN 2的监视器输入管脚。用户可以将外部信号连接到

这些管脚,在软件控制下,可以多路传输到监控目的的监视器。图47显示了一个典型的监控电路,该电路在一个6导SOT封装中使用一个12位SAR ADC实现。外部参考输入连接到MON_IN 1,以便于监视。控制器输出端口选择要监视的通道,输入端口从ADC读取转换后的数据。

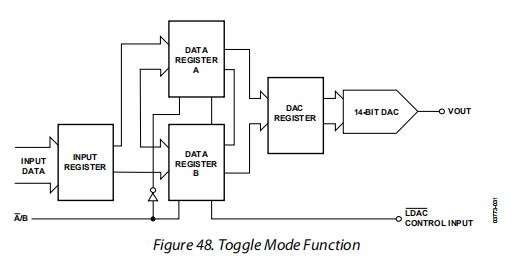

切换模式功能

切换模式功能允许使用在两个DAC数据寄存器之间切换的LDAC控制信号生成输出信号。此函数使用SFR控制寄存器进行配置,如下所示:使用REG1=REG0=0、A3到A0=1100的写入指定控制寄存器写入。使用AD5390/AD5392控制寄存器中的位CR3和位CR2,并使用AD5391控制寄存器中的位CR1和位CR0,在八个信道组中启用切换模式功能。(参见控制寄存器写入部分。)图48显示了切换模式实现的框图。AD5390/AD5391/AD5392上的每个DAC通道都包含A和B数据寄存器。注意,B寄存器只能在启用切换模式时加载。

要将AD5390/AD5391/AD5392配置为切换操作模式,事件顺序如下:

1、通过控制寄存器为所需通道启用切换模式。

2、将数据加载到所有A寄存器。

3、将数据加载到所有B寄存器。

4、应用LDAC。

LDAC用于在确定模拟输出。第一个LDAC配置输出以反映A寄存器中的数据。如果用户希望在所有通道的输出端产生方波,则该模式提供了显著的优势,这可能是驱动基于液晶的可变光衰减器所必需的。

例如,配置AD5390时,用户写入控制寄存器并设置CR3=1和CR2=1,从而启用八个组中的两个组进行切换模式操作。用户必须将数据加载到所有16个A寄存器和B寄存器。切换LDAC设置输出值以反映A和B寄存器中的数据,LDAC的频率确定方波输出的频率。第一个LDAC将A寄存器的内容加载到DAC寄存器。切换模式通过控制寄存器禁用;禁用切换模式后的第一个LDAC用A寄存器中包含的数据更新输出。

热监测功能

AD5390/AD5391/AD5392具有温度关闭功能,以在多个输出短路时保护芯片。每个输出放大器的短路电流通常为40毫安。在5 V电压下操作AD5390/AD5391/AD5392将导致200 mW/短路放大器的功耗。当五个通道短路时,这会导致额外的瓦特功耗。对于52导联LQFP,θ通常为44°C/W。

热监测器由用户使用AD5390/AD5392控制寄存器中的CR8和AD5391控制寄存器中的CR6启用。如果模具温度超过约130°C,AD5390/AD5391/AD5392上的输出放大器将自动断电。发生热关机后,如果温度降至130°C以下,用户可以通过执行软启动或通过控制寄存器关闭热监测功能来重新启用部件。

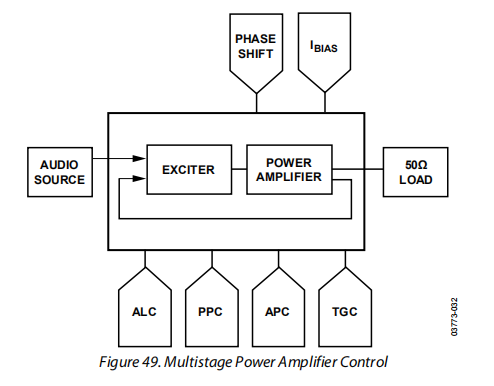

功率放大器控制

多级功率放大器的设计要求在输出级的操作和控制中有大量的设定值。AD5390/AD5391/AD5392由于其较小的尺寸(LFCSP)和8和16通道的集成,提供12和14位分辨率,因此非常适合这些应用。图49显示了典型的发射机架构,其中AD5390/AD5391/AD5392 DAC可用于以下控制电路:I控制、平均功率控制(APC)、峰值功率控制(PPC)、发射增益控制(TGC)和音频电平控制(ALC)。在整个放大器设计中,可变电压衰减器、移相器控制和直流设定点控制也需要DAC。

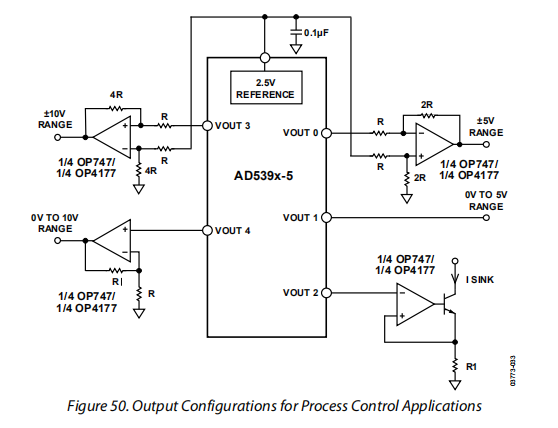

过程控制应用

AD5390-5/AD5391-5/AD5392-5是过程控制应用的理想选择,因为它提供8和16通道以及12位和14位分辨率的组合。这些应用通常需要0 V到5 V±5 V、0 V到10 V±10 V的输出电压范围,以及电流接收器和电源功能。AD5390-5/AD5391-5/AD5392-5由一个5V电源工作,因此,需要外部信号调节以实现此处描述的输出范围。图50显示了实现这些输出范围的配置。在这些应用中使用AD5390-5/AD5391-5/AD5392-5的主要优点是:封装尺寸小,引脚兼容能力可从12位升级到14位,集成芯片2.5V参考电压,最高温度系数为10ppm/℃,以及卓越的精度规范。AD5390-5/AD5391-5/AD5392-5包含每个信道的偏移和增益寄存器,因此用户可以在每个信道的基础上执行系统级校准。

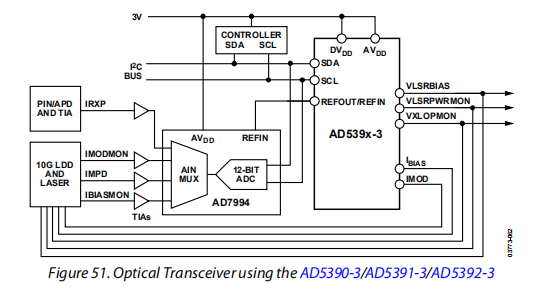

光纤通信收发模块

AD5390-3/AD5391-3/AD5392-3非常适合光收发器应用。例如,在300针MSA应用中,需要数模转换器来控制激光功率、APD偏置和调制器振幅。模块的模拟输出需要诊断信息。AD5390-3/AD5391-3/AD5392-3提供8/16通道的组合,64引线LFCSP中12/14位的分辨率,并在2.7 V到5.5 V的电源电压和内部参考电压下工作。AD5390-3/AD5391-3/AD5392-3还具有集成电路兼容和SPI接口,使它们成为这些应用中的理想组件。图51显示了光收发器应用中的典型配置。

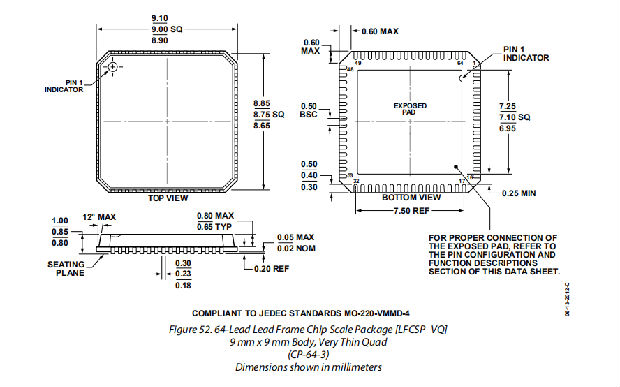

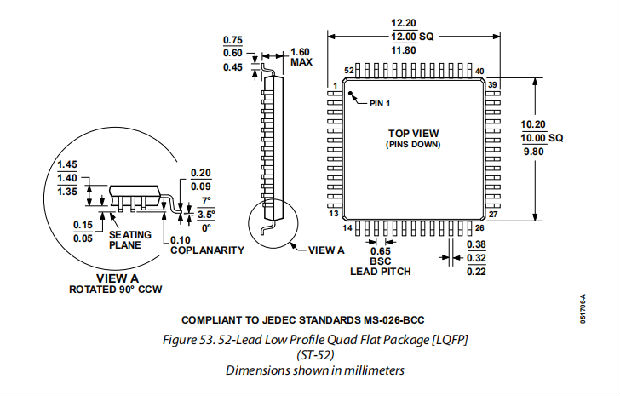

外形尺寸