ISL6530点击型号即可查看芯片规格书

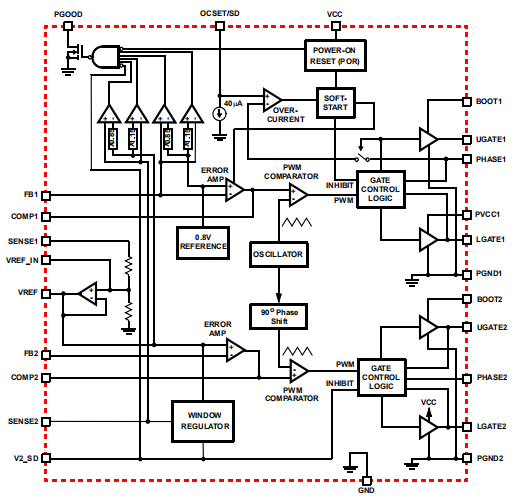

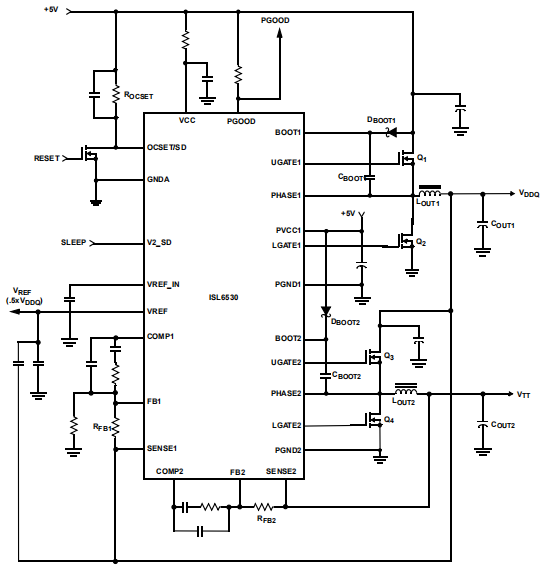

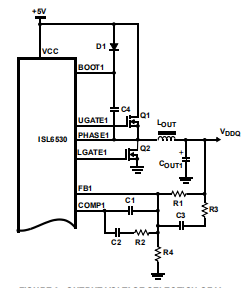

ISL6530为为高性能而优化的双DC-DC转换器DDRAM内存应用程序。它的设计目的是降低车速同步整流buck中的N沟道mosfet有效生成2.5V VDDQ的拓扑结构DDRAM存储器,用于DDRAM差分信号的VREF,以及用于信号终止的VTT。ISL6530集成了控制、输出调节、监视和保护功能集成到单个包中。转换器的VDDQ输出保持在2.5V通过集成的精密电压基准。VREF输出精确地调节到存储功率的1/2供应,最大温度公差为±1%以及线路电压变化。VTT精确跟踪VREF。在V2_SD睡眠模式下,VTT输出由低功率车窗调节器。ISL6530提供简单、单反馈回路、电压模式控制和快速瞬态响应。它包括两个锁相300kHz三角波振荡器替换90度,以最小化两者之间的干扰脉宽调制调节器。调节器具有误差放大器15MHz增益带宽积和6V/微秒转换速率为快速瞬变启用高转换器带宽表演。由此产生的脉宽调制占空比范围为0%到100%。ISL6530通过抑制脉冲宽度调制操作。ISL6530监控电流在VDDQ调节器中,使用上部的rDS(ON无需电流传感的MOSFET电阻器。

特征

为单通道和双通道DDRAM内存系统提供VDDQ、VREF和VTT电压

卓越的电压调节-VDDQ=2.5V±2%满量程-VREF=(VDDQ÷2)±1%超过全工作范围-VTT=VREF±30mV

支持“S3”睡眠模式-VTT通过低功率车窗调节器保持在VDDQ÷2最小化唤醒时间

快速瞬态响应-全0%至100%占空比

从+5V输入操作

VDD上的过电流故障监视器-不需要额外的电流传感元件-使用MOSFET的rDS(ON)

驱动廉价的N通道mosfet

转换器尺寸小-300kHz固定频率振荡器

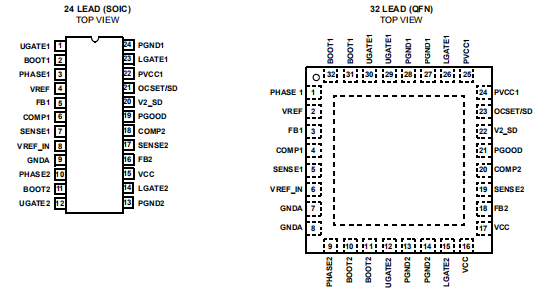

24引线,SOIC或32引线,5mm×5mm QFN

提供无铅(符合RoHS)

应用

DDRAM存储器的VDDQ、VTT和VREF调节系统-AMD®Athlon的主存储器8482; 和K8™,奔腾三、 奔腾IV、Transmeta、PowerPC™,阿尔法PC™,和基于UltraSparc®的计算机系统-图形系统中的视频存储器大功率跟踪DC-DC调节器

绝对最大额定值热信息

电源电压,VCC。+7.0伏

启动电压,VBOOTn-VPHASEn。+7.0伏

输入、输出或I/O电压。接地-0.3V至VCC+0.3V

静电放电分类。2级

操作条件

电源电压,VCC。+5V±10%

环境温度范围。0oC至70oC

结温范围。0oC至125oC

热阻θJA(oC/W)θJC(oC/W)

SOIC封装(注1)。65牛刀

QFN包(注2)。33 4个

最高结温。150摄氏度

最高储存温度范围。-65摄氏度至150摄氏度

最高铅温(焊接10s)。300摄氏度

(SOIC-仅限铅头)

有关推荐的焊接条件,请参阅技术简介TB389。

注意:超过“绝对最大额定值”中列出的应力可能会对设备造成永久性损坏。这是一个压力等级和操作

在本规范操作章节中所述的上述条件或任何其他条件下的装置并不隐含。

注:

1.θJA是用安装在自由空气中的高效热导率测试板上的元件测量的。详见技术简报TB379。

2.θJA是在自由空气中测量的,该部件安装在具有“直接连接”特性的高效热导率测试板上。θJC“外壳温度”是在包装底部外露金属垫的中心测量的。

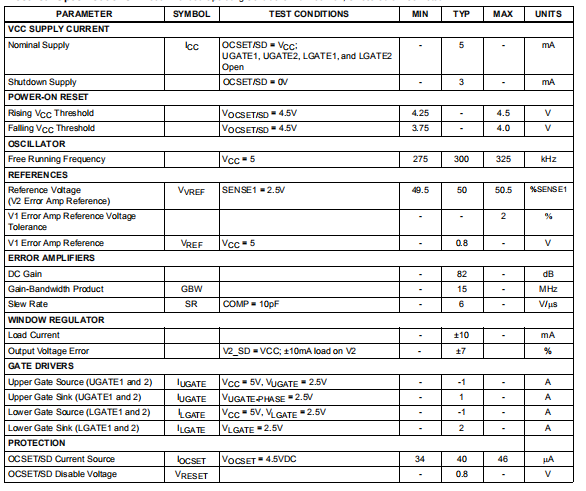

电气规范推荐的工作条件,Vcc=5V,除非另有说明

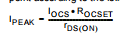

BOOT1和BOOT2这些引脚为上MOSFET提供偏压。单电容自举电路可用于创建一个适合驱动标准N 沟道MOSFET的引导电压。UGATE1和UGATE2将UGATE1和UGATE2连接到相应的上部MOSFET栅极。这些销为上MOSFETs。UGATE2也由自适应击穿保护以确定上场效应晶体管VTT调节器已关闭。LGATE1和LGATE2将LGATE1和LGATE2连接到相应的下部MOSFET栅极。这些销为低mosfet。这些管脚由自适应击穿保护以确定何时已关闭。PGND1和PGND2这些是门驱动器的电源接地连接控制脉冲宽度调制。把这些别针系在地平面上通过可用的最低阻抗连接。接触网/SD一个电阻器(ROCSET),从这个引脚连接到VDDQ稳压器的上部MOSFET设置过电流跳闸点。ROCSET,内部40微安电流源极(IOCS)和上MOSFET导通电阻(rDS(ON))设置VDDQ转换器过电流(OC)跳闸根据以下公式点:

过电流跳闸循环软启动功能。将OCSET/SD引脚拉到地上可重置ISL6530和所有外部mosfet关闭,允许两个输出电压电源轨浮动。普古德这个开漏输出的高电平表明VDDQ和VTT调节器在正常工作范围内电压范围。GNDA公司IC的信号接地。把这个别针系在地平面上通过可用的最低阻抗连接。VCC公司芯片的5V偏置电源连接到此引脚。这个引脚也是下栅极驱动器的正极电源,LGATE2号。将去耦良好的5V电源连接到此引脚。二级标准差V2-SD输入的高电平将V2控制器置于“睡眠”模式。在睡眠模式下,UGATE2和LGATE2低驱动,有效浮动VTT供应。当VTT供应“浮动”时,它保持在通过驱动VTT的低电流玻璃升降器的VDDQ通过传感器2引脚。玻璃升降器可以克服VTT上至少有±10mA的泄漏。当V2_SD高时,PGOOD低。阶段1和阶段2将相位1和相位2连接到相应的上部MOSFET源。这个销用作上部的一部分MOSFET自举驱动器。阶段1用于监控VDDQ上MOSFET的电压降过流保护调节器。相1引脚为由自适应直通保护电路监控确定VDDQ电源的上FET关闭。FB1、COMP1、FB2和COMP2COMP1、COMP2、FB1和FB2是可用的外部错误放大器的管脚。FB1和FB2管脚是反转每个误差放大器和COMP1的输入COMP2引脚是相关的输出。合适的AC跨这些管脚的网络用于补偿

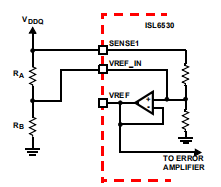

每个转换器的电压控制反馈回路。VREF和VREF_INVREF产生的电压等于感觉1。这个低电流输出连接到VREF正在通电的DDRAM设备的输入。同样的电压用作VTT误差的参考输入放大器。因此VTT控制在VDDQ的50%。VREF_-IN被用作一个选项来加速内部电阻分压器网络,用于设置输出电压和VTT电源的参考电压。一个VREFúIN与接地之间的100pF电容器建议正确操作

PVCC1型

这是下栅极驱动器LGATE1的正电源。PVCC1连接到一个良好的去耦5V。传感器1和传感器2SENSE1和SENSE2都直接连接到VDDQ和VTT电源的调节输出,分别是。SENSE1用作创建VREF_输出电压和VTT的参考电压供应。传感器2用作在V2-SD模式下启用的车窗调节器。

功能描述

概述

ISL6530包含两个控制和驱动电路同步降压型PWM电压调节器。两个调节器利用5V自举输出拓扑,允许使用低成本N通道mosfet。监管者是由300kHz时钟。时钟是相位锁定和移位的90度以最小化控制器之间的噪声耦合。第一个调节器包括精度为0.8V的基准电压,并且旨在为DDRAM内存提供适当的VDDQ系统。VDDQ控制器实现过电流利用上部MOSFET的rDS(ON)进行保护。出现故障后,VDDQ调节器软启动通过数字软启动电路。ISL6530中包括一个精确的VREF参考输出。VREF是.5xVDDQ的缓冲表示。VREF公司通过连接的精密内部电阻分压器导出到SENSE1终端。第二个PWM调节器设计用于提供VTTDDRAM信号线的终端。提及VTT调节器为VREF。因此,VTT调节器提供终端电压等于.5xVDDQ。上部排水管VTT电源的MOSFET连接到VDDQ电压。VTT控制器的设计使VTT轨道上的下沉和源电流。ISL6530双控制器带来两个好处拓扑结构。首先,由于VREF总是.5xVDDQ,VTT电源将在软启动循环期间跟踪VDDQ电源。其次,VDDQ电源中的过电流保护同时保护VTT电源。初始化ISL6530在应用输入功率。输入电源的特殊顺序必要的。上电复位(POR)功能持续监控VCC引脚的输入偏置电源电压。这个POR功能在5V偏置后启动软启动操作电源电压超过其POR阈值。

软起动

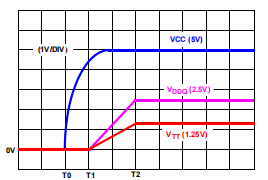

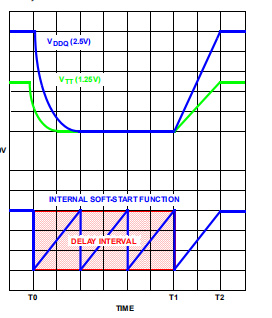

POR函数启动数字软启动序列。这个VDDQ调节器的脉冲宽度调制误差放大器参考输入为钳制到与软起动电压成比例的水平。作为软启动电压上升,脉冲宽度调制比较器产生为输出充电的增加宽度的相位脉冲电容器。这种方法提供了一种快速且可控的输出电压上升。软启动序列通常需要大约7毫秒。保持VTT调节器基准自动跟踪VDDQ软启动的斜坡,因此为VTT启用软启动。图2显示了典型应用程序的软启动序列。在t0,+5V的VCC偏置电压开始上升。一旦VCC上的电压在时间t1超过POR阈值,两者输出开始其软启动序列。三角波从PWM振荡器比较了上升误差放大器输出电压。作为误差放大电压增加,磨牙销上的脉冲宽度增加到在时间t2达到其稳态占空比。

穿透保护当两个上部同时打开MOSFET和下MOSFET,有效地使输入电压对地短路。保护从射穿状态的监管者,ISL6530包含专门的电路,确保互补mosfet不同时开启。VDDQ采用的自适应直通保护调节器查看下浇口驱动销LGATE1和相位节点,相位1,用于确定MOSFET是否开或关。如果相位1低于0.8V,则上栅极为定义为关闭。同样,如果LGATE1低于0.8V,则下MOSFET被定义为关断。这种方法击穿保护允许VDDQ调节器仅限源电流。由于下沉电流的必要性,VTT调节器采用了一种改进的保护方案VDDQ调节器。如果电压来自UGATE2或LGATE2到GND小于0.8V,则MOSFET被定义为关,而另一个MOSFET是打开。因为较低的MOSFET栅极和较高的MOSFET栅极的电压电压互感器电源的MOSFET栅极被测量为确定MOSFET的状态,设计者是鼓励考虑引入栅极驱动器和它们之间的外部组件实际实施前各自的MOSFET栅极这些措施。这样做可能会通过保护干扰射击。

断电模式

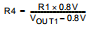

DDRAM系统包括一个睡眠状态,其中VDDQ存储器的电压保持不变,但信号是暂停的。在此模式下,VTT终端电压为不再需要了。VTT总线上的唯一负载是DDRAM和存储器控制器集成电路。当ISL6530的V2_SD输入驱动高时VTT调节器处于“睡眠”状态。在睡梦中说明主VTT调节器被禁用,同时上下mosfet被关闭。VTT总线通过低电流窗口保持在接近.5xVdd通过传感器2引脚驱动VTT的调节器。将VTT保持在.5xVDDQ消耗的功率可以忽略不计并可在不使用需要软启动VTT调节器。在这个权力期间下降模式,PGOOD保持在低位。输出电压选择VDDQ调节器的输出电压可以是编程为车辆识别号(即+5V)和内部参考,0.8V。使用外部电阻分压器相对于参考电压调整输出电压然后反馈到误差放大器的反向输入端,见图3。但是,由于R1的值影响其他补偿组件的值建议将其值保持在5kΩ以下。R4可以是根据以下公式计算:

如果所需的输出电压为0.8V,只需布线VOUT1通过R1返回到FB管脚,但不要填充R4。

VTT参考超速档ISL6530允许设计器绕过内部50%作为VTT参考的VDDQ的跟踪。这个ISL6530设计用于将VDDQ电压除以50%通过两个内部匹配电阻。这些电阻通常为200kΩ。一种可以用来绕过内部VTT参考生成是为了提供外部参考直接连接到VREF_IN管脚。进行此操作时,传感器1引脚必须保持不连接。当由于VTT调节器不采用自己软启动。第二种方法是加速内部电阻器。图4显示了如何实现这个方法。这个用于超速驱动内部电阻器的外部电阻器应小于2kΩ,公差为1%或更好。此方法仍然在电阻网络和VREF引脚上的任何负载。如果有的话无需加载VREF引脚,则无需缓冲以及电阻网络产生的参考电压可以直接绑定到VREF

变频器停机

将OCSET/SD引脚拉至0.8V以下关闭两个调节器。在这个状态下,PGOOD将保持低调。松开OCSET/SD引脚后,IC进入进入软启动循环,使两个输出都回到监管。电压监测ISL6530提供一个PGOOD信号,可以进行通信VDDQ和VTT的调节是否在调节的±15%,V2_SD引脚保持在低位,且偏压集成电路的电压高于POR电平。如果所有的标准以上是真的,PGOOD引脚将处于高阻抗水平。如果上面列出的一个或多个标准是错误的,PGOOD引脚将保持在低位。过电流保护过电流功能可防止转换器短路使用上MOSFET导通电阻rDS(on)输出监视电流的VDDQ。这种方法增强了变频器的效率和降低成本电流感应电阻器。过电流功能循环软启动功能提供故障保护的打嗝模式。电阻器(ROCSET)对过电流跳闸电平进行编程(见图1)。内线40微安(典型)电流汇在ROCSET上产生电压指的是车辆识别号。当电压通过上部VDDQ的MOSFET(也指VIN)超过通过ROCSET的电压,过电流功能启动软启动顺序。图5说明了响应于VDDQ上的过电流事件。在时间T0,过电流通过VDDQ的上MOSFET感测到状态调节器。因此,两个调节器都很快关闭内部软启动功能开始产生软启动斜坡。输出所看到的延迟间隔是相当于三个软启动循环。第四个内部软启动循环在时间T1。两个输出都通过时间t2,只要过电流事件已清除。如果过电流的原因在延迟间隔,将检测到过电流情况两个监管者都会因为另一个三个软启动周期的延迟间隔。结果打嗝保护方式将继续重复无限期

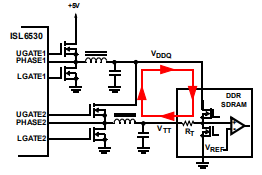

电流下沉

ISL6530 VTT稳压器采用了一种MOSFET射通保护方法,允许转换器下沉电流和源电流。应谨慎行事当使用ISL6530设计转换器时已知转换器可能吸收电流。当转换器下沉电流时,它表现为调节输入电压的升压变换器。这个意味着转换器正在向输入端注入电流调节器导轨。如果这股水流无处可去,例如在轨道上或通过限压保护装置,该轨道上的电容会吸收电流。这种情况将允许电压增加输入轨的高度。如果钢轨的电压水平被提升到超过最大电压的水平连接到输入轨的任何组件的额定值,然后这些部件可能会出现不可逆故障或经历可能缩短寿命的压力。确保除了轨道上的电容将防止这种故障模式。以确保电流不会增加输入轨VTT调节器的电压,建议VTT调节器的输入轨是VDDQ的输出调节器。电压互感器调节器产生的电流将进入VDDQ轨道,然后进入DDRSDRAM内存模块并返回到VTT调节器。图6显示了推荐的配置和产生电流回路

应用指南

布局注意事项

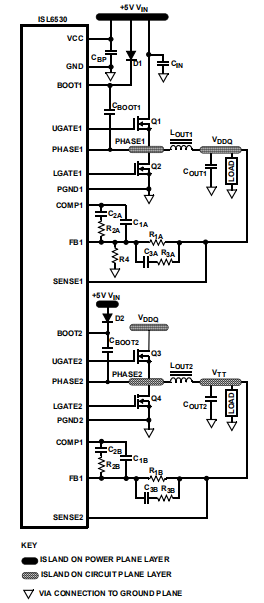

布局在高频开关中非常重要转换器设计。电源设备在300kHz,由此产生的电流从一个设备过渡到另一个原因是互连线路上的电压尖峰阻抗和寄生电路元件。这些电压尖峰会降低效率,将噪音辐射到电路中,并导致装置过电压应力。小心部件布局和印刷电路板设计使电压最小化转换器中出现尖峰。例如,考虑PWM的关断转换MOSFET。在关闭之前,MOSFET将负载电流。在关闭期间,电流停止在并被较低的MOSFET接收。任何开关电流通路中的寄生电感产生开关间隔期间电压尖峰较大。小心组件选择,关键组件的紧密布局,短而宽的轨迹使电压的大小最小化钉子。DC-DC中有两组关键组件使用ISL6530的转换器。开关元件是最关键的是因为他们会因此会产生大量的噪音。接下来是连接敏感节点或提供临界旁路电流信号耦合建议使用多层印刷电路板。图7显示中关键组件的连接转换器。注意电容器CIN和COUT表示许多物理电容器。奉献一个固体层,通常是PC板的中间层,用于接地对所有关键部件进行平面和接地连接这一层有通孔。将另一个实体层作为动力飞机把这架飞机分成共同电压水平。保持金属从输出电感的相位端子短路。权力飞机应支持输入功率和输出功率节点。在顶部和底部使用铜填充多边形相位节点的电路层。使用剩余的打印内容用于小信号布线的电路层。电线的痕迹来自到MOSFET栅极的栅极引脚应保持短宽到可以轻松处理1A的驱动电流。