448点击型号即可查看芯片规格书

关键词:集成电路芯片自动测试设备DFT技术

随着芯片集成度的越来越高,如今的IC测试面临着前所未有的挑战:

测试时间越来越长,百万门级的SoC测试可能需要几个月甚至更长的时间;

测试矢量的数目越来越多,覆盖率却难以提高,人们不知道究竟要用多少测试矢量才能覆盖到所有的器件;

测试设备的使用成本越来越高,直接影响到芯片的成本。

一、测试的概念和原理

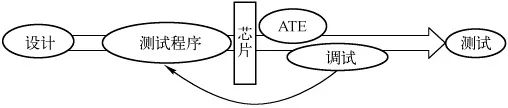

集成电路(IC)测试是IC产业链中重要的一环,而且是不可或缺的一环,它贯穿于从产品设计开始到完成加工的全过程。目前所指的测试通常是指芯片流片后的测试,定义为对被测电路施加已知的测试矢量,观察其输出结果,并与已知正确输出结果进行比较而判断芯片功能、性能、结构好坏的过程。图1说明了测试原理,就其概念而言,测试包含了三方面的内容:已知的测试矢量、确定的电路结构和已知正确的输出结果。

10090953.jpg" src="https://img.icspec.com/technologyArticle/dc163f26-6a03-11ed-bcbe-b8ca3a6cb5c4.jpg" />

图1集成电路测试原理

二、测试及测试矢量的分类

1.按测试目的分类

根据测试的目的不同,可以把集成电路测试分为4种类型。

(1)验证测试(Verification Testing,也称作Design Validation)

当一款新的芯片第一次被设计并生产出来,首先要接受验证测试。在这一阶段,将会进行功能测试,以及全面的AC、DC参数的测试。通过验证测试,可以诊断和修改设计错误,为最终规范(产品手册)测量出芯片的各种电气参数,并开发出测试流程。

(2)生产测试(Manufacturing Testing)

当芯片的设计方案通过了验证测试,进入量产阶段之后,将利用前一阶段调试好的流程进行生产测试。在这一阶段,测试的目的就是明确做出被测芯片是否通过测试的判决。由于每一颗芯片都要进行生产测试,所以测试成本是这一阶段的首要问题。从这一角度出发,生产测试通常所采用的测试向量集不会包含过多的功能向量,但是必须有足够高的模型化故障的覆盖率。

(3)可靠性测试(Reliability Testing)

通过生产测试的每一颗芯片并不完全相同,最典型的例子就是同一型号产品的使用寿命不尽相同。可靠性测试就是要保证产品的可靠性,通过调高供电电压、延长测试时间、提高温度等方式,将不合格的产品(如会很快失效的产品)淘汰出来。

(4)接受测试(Acceptance Testing)

当芯片送到用户手中,用户将进行再一次的测试。例如,系统集成商在组装系统之前,会对买回的各个部件进行此项测试。

2.按测试方式的分类

根据测试方式的不同,测试矢量也可以分为3类。

(1)穷举测试矢量(Exhaustive Vector)

穷举测试矢量是指所有可能的输入矢量。该测试矢量的特点是覆盖率高,可以达到100%,但是其数目惊人,对于具有n个输入端口的芯片来说,需要2n个测试矢量来覆盖其所有的可能出现的状态。例如,如果要测试74181ALU,其有14个输入端口,就需要214=16384个测试矢量,对于一个有38个输入端口的16位的ALU来说,以10 MHz的速度运行完所有的测试矢量需要7.64个小时,显然,这样的测试对于量产的芯片是不可取的。

(2)功能测试矢量 (Functional Vector)

功能测试矢量主要应用于验证测试中,目的是验证各个器件的功能是否正确。其需要的矢量数目大大低于穷举测试,以74181ALU为例,只需要448个测试矢量,但是目前没有算法去计算矢量是否覆盖了芯片的所有功能。

(3)结构测试矢量 (Structural Vector)

这是一种基于故障模型的测试矢量,它的最大好处是可以利用电子设计自动化(EDA)工具自动对电路产生测试向量,并且能够有效地评估测试效果。74181ALU只需要47个测试矢量。这类测试矢量的缺点是有时候工具无法检测所有的故障类型。

三、自动测试设备

与IC测试有关的另外一个重要概念就是自动测试设备(ATE,Automatic Test Equipment)。使用ATE可以自动完成测试矢量的输入和核对输出的工作,大大提高了测试速度,但是目前其仍旧面临不小的挑战。

该挑战主要来自于两方面。首先是不同芯片对于同种测试设备的需求。在一般情况下,4~5个芯片需要用同一个测试设备进行测试,测试时间只有一批一批的安排。每种设计都有自己的测试矢量和测试环境,因此改变被测芯片时,需要重新设置测试设备和更新测试矢量。其次是巨大测试矢量对于测试设备本身性能的要求。目前,百万门级SoC的测试矢量规模非常大,可能达到数万个,把这些测试矢量读进测试设备并初始化需要相当长的时间。解决这一方法的途径是开发具有大容量矢量存储器的测试矢量加载器。例如,Advantest的W4322的高速测试矢量加载服务器,可以提供72 GB的存储空间,可以缩短80%的矢量装载时间。

四、可测性的概念

可测性是现在经常使用,却经常被理解错的一个词。其框架式的定义是,可测性是在一定的时间和财力限制下,生成、评价、运行测试,以满足一系列的测试对象(例如,故障覆盖率、测试时间等)。对一些具体的集成电路来说,对该定义的解释由于使用工具和已有的技术水平的不同而不同。目前工业界使用的一个范围比较窄的定义是,可测性是能够测试检验出存在于设计产品中的各种制造缺陷的程度。

1.可测性设计(DFT,Design For Testability)

所谓可测性设计是指设计人员在设计系统和电路的同时,考虑到测试的要求,通过增加一定的硬件开销,获得最大可测性的设计过程。简单来说,可测性设计即是指为了达到故障检测目的所做的辅助性设计,这种设计为基于故障模型的结构测试服务,用来检测生产故障。目前,主要的可测性设计方法有扫描通路测试、内建自测试和边界扫描测试等。

为什么说DFT是必需的?让我们先来看看传统的测试方法,如图2所示。在传统测试方法中,设计人员的职责止于验证阶段,一旦设计人员认定其设计满足包括时序、功耗、面积在内的各项指标,其工作即告结束。此后,测试人员接过接力棒,开始开发合适的测试程序和足够的测试图形,用来查找出隐藏的设计和制造错误。但是,在其工作期间很少了解设计人员的设计意图,因此,测试人员必须将大量宝贵的时间花在梳理设计细节上,而且测试开发人员必须等到测试程序和测试模型经过验证和调试之后才能知道早先的努力是否有效。沿用传统测试方法,测试人员别无选择,只能等待流片完成和允许他使用昂贵的自动测试设备(ATE)。这就导致了整个设计-测试过程周期拉大,充斥着延误和效率低下的沟通。

图2 传统的设计测试流程

自20世纪80年代以来,规模较大的半导体生产商就开始利用DFT技术来改善测试成本,降低测试复杂度。如今,前端设计人员都能清楚地认识到只要使用恰当的工具和方法,在设计的最初阶段就对测试略加考虑,会在将来受益匪浅,见图3。DFT技术与现代的EDA/ATE技术紧密地联系在一起,大幅降低了测试对ATE资源的要求,便于集成电路产品的质量控制,提高产品的可制造性,降低产品的测试成本,缩短产品的制造周期。

图3 现在的设计测试流程

2.可控制性和可观测性

可控制性(Controllability)和可观测性(Observability)是可测性设计中的重要概念。可控制性表示通过电路初始化输入端控制电路内部节点逻辑状态的难易程度,如果电路内部节点可被驱动为任何值,则称该节点是可控的。可观察性表示通过控制输入变量,将电路内部节点的故障传播到输出端以便对其进行观察的难易程度。如果电路内部节点的取值可以传播到电路的输出端,且其值是预知的,则称该节点是可观察的。

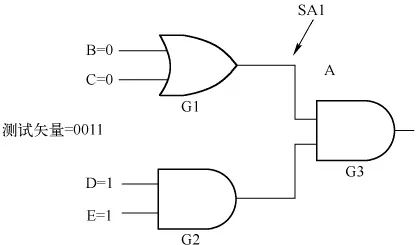

所谓集成电路的可控制性可以理解为将该信号设置成0或者1的难度。如图4所示,对于与门G3输入端口A的固定为逻辑值1的故障,可以通过在外围端口B、C、D、E施加矢量0011来检测,因此认为该节点是可控制的。

图4 可控制性举例

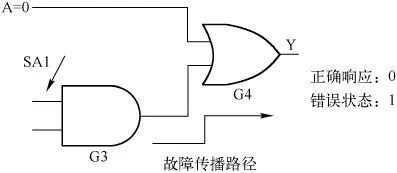

可观测性是指观察这个信号所产生故障的难度。如图5所示,G3输入端口A的固定为逻辑值1的故障可以通过施加0向量而传输到外围端口Y,因此认为其为可观测的。

图5 可观测性举例

五、可测性设计的优势和不足

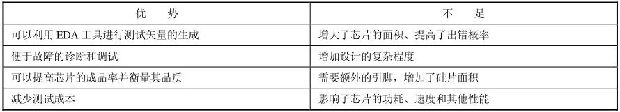

人们通常会问,为什么要在原有的电路中加入额外的测试结构?这个问题确实很难回答,DFT的经济性涉及包括设计、测试、制造、市场销售等各个方面。不同的人衡量的标准也不一样,设计工程师通常觉得DFT附加的电路会影响芯片的性能,而测试工程师会认为有效的可测性设计将大大提高故障覆盖率。表1列出了可测性设计的一些优势和不足。

表1 DFT的优势和不足

来自工业界的许多实例证明,加入额外的测试结构确实有助于芯片成品率的提高,从而大幅降低了芯片的制造成本。当然为了弥补一些缺陷,DFT技术本身也在不断地改进和发展。

六、常用的可测性设计

1.内部扫描测试设计

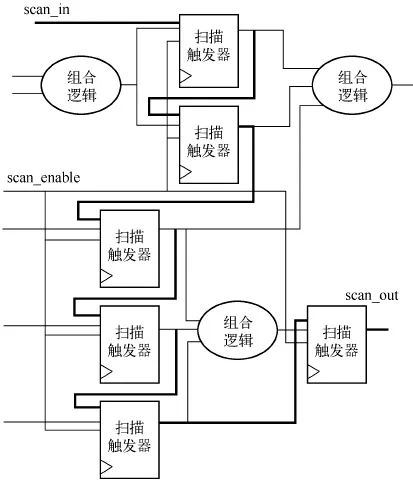

内部扫描设计的主要任务就是要增加内部状态的可控制性和可观察性。对于集成电路而言,其做法是将内部时序存储逻辑单元连接成移位寄存器形式,从而可将输入信号通过移位输入内部存储逻辑单元以满足可控制性要求。同样,以移位方式将内部状态输出以满足可观察性要求。采用扫描路径设计的芯片在测试方式下工作时,内部构成一个长的移位寄存器。

如图6所示,扫描测试工具首先把普通的触发器变成了带扫描使能端和扫描输入的触发器,然后把这些触发器串联在一起。当scan_enable无效时,电路可以正常工作,当scan_enable有效时,各触发器的值将可以从来自片外的scan_in信号串行输入。这样就可以对各片内寄存器赋值,也可以通过scan_out得到它们的值。支持扫描测试设计的工具有Synopsys公司的DFT Compiler及Mentor的DFT Advisor。

图6 扫描测试电路

2.自动测试矢量生成(ATPG,Automation Test Pattern Generation)

ATPG采用故障模型,通过分析芯片的结构生成测试向量,进行结构测试,筛选出不合格的芯片。通常ATPG工具和扫描测试工具配合使用,可以同时完成测试矢量的生成和故障仿真。

首先是故障类型的选择。ATPG可以处理的故障类型不仅是阻塞型故障,还有延时故障和路径延时故障等,一旦所有需要检测的故障类型被列举,ATPG将对这些故障进行合理的排序,可能是按字母顺序、按层次结构或者随机排序。

在确定了故障类型后,ATPG将决定如何对这类故障进行检测,并且需要考虑施加激励向量测试点,需要计算所有会影响目标节点的可控制点。此类算法包括D算法等。

最后是寻找传输路径,可以说这是向量生成中最困难的,需要花很多时间去寻找故障的观测点的传播。因为通常一个故障拥有很多的可观测点,一些工具一般会找到最近的那一个。不同目标节点的传输路径可能会造成重叠和冲突,当然这在扫描结构中是不会出现的。支持产生ATPG的工具有Mentor的Fastscan和Synopsys的TetraMAX。

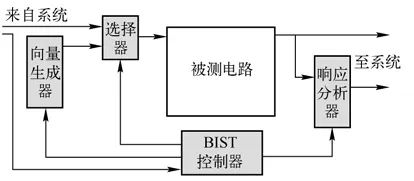

3.存储器内建自测试(Memory Built-in-self-test)

内建自测试是当前广泛应用的存储器可测性设计方法,它的基本思想是电路自己生成测试向量,而不是要求外部施加测试向量,它依靠自身来决定所得到的测试结果是否正确。因此,内建自测必须附加额外的电路,包括向量生成器、BIST控制器和响应分析器,如图7所示。BIST的方法可以用于RAM、ROM和Flash等存储设备,主要用于RAM中。大量关于存储器的测试算法都是基于故障模型的。常用的算法有棋盘式图形算法和March算法。

图7 BIST的基本结构

支持BIST的工具有Mentor的mBISTArchitect和Synopsys的SoCBIST。

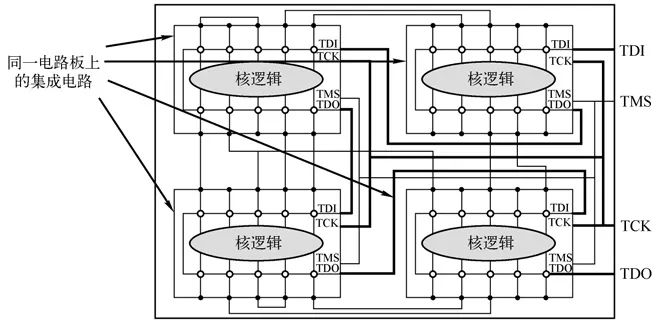

4.边界扫描测试(Boundary Scan)

边界扫描的原理是在核心逻辑电路的输入和输出端口都增加一个寄存器,通过将这些I/O上的寄存器连接起来,可以将数据串行输入被测单元,并且从相应端口串行读出。在这个过程中,可以实现芯片级、板级和系统级的测试。其中,最主要的功能是进行板级芯片的互连测试,如图8所示。

图8 利用边界扫描进行板级测试

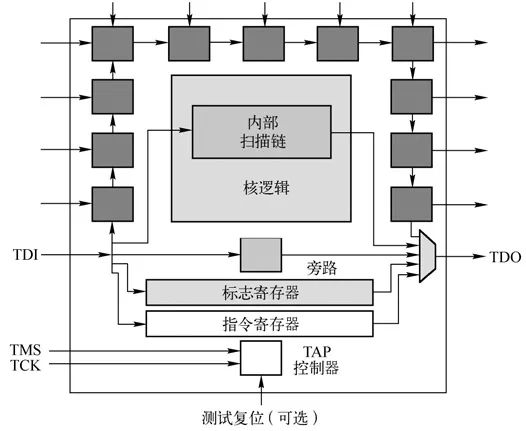

边界扫描是欧美一些大公司联合成立的一个组织——联合测试行动小组(JTAG)为了解决印制电路板(PCB)上芯片与芯片之间互连测试而提出的一种解决方案。由于该方案的合理性,它于1990年被IEEE采纳而成为一个标准,即IEEE 1149.1。该标准规定了边界扫描的测试端口、测试结构和操作指令,其结构如图9所示。该结构主要包括TAP控制器和寄存器组。其中寄存器组包括边界扫描寄存器,旁路寄存器,标志寄存器和指令寄存器。主要端口为TCK、TMS、TDI、TDO,另外还有一个用户可选择的端口TRST。

支持边界扫描的自动设计工具有Mentor的BSD Architect和Synopsys的BSD Compiler。

图9 IEEE 1149.1结构