8226点击型号即可查看芯片规格书

710点击型号即可查看芯片规格书

HMCAD1511点击型号即可查看芯片规格书

特征

8位高速单/双/四ADC单通道模式:FSmax=1000msps双通道模式:FSmax=500 MSPS四通道模式:FSmax=250 MSPS8226;集成交叉点开关(Mux阵列)1倍至50倍数字增益没有丢失的代码高达32倍1X增益:49.8dB信噪比。10X增益:48分贝信噪比•内部低抖动可编程时钟分频器超低功耗710兆瓦,包括1000毫秒每秒的I/O•0.5微秒睡眠启动时间,断电后15微秒内部参考电路,无所需外部组件粗增益和精增益控制每个ADC的数字精细增益调整内部偏移校正1.8V电源电压控制接口引脚上的1.7-3.6V CMOS逻辑串行LVDS/RSDS输出7x7 mm QFN 48(LP7D)包装

典型应用

USB供电示波器数字示波器卫星接收器

销兼容零件

HMCAD1511的引脚与HMCAD1520兼容

HMCAD1511与管脚兼容,可以配置为作为HMCAD1510操作,具有所述功能和性能在HMCAD1510数据表中

一般说明

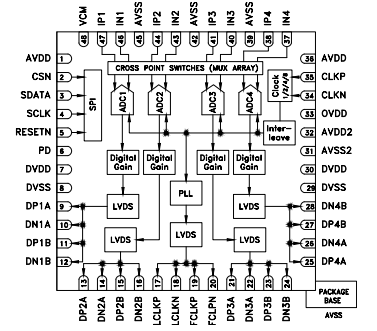

HMCAD1511是一种多用途高性能低功耗模数转换器(ADC),采用时间交错以提高采样率。集成交叉点开关激活用户选择的输入。在单通道模式下,可以选择四个输入中的一个作为单ADC通道的有效输入。双重的通道模式,四个输入中的任意两个可以选择到每个ADC通道。在四通道模式下,任何输入都可以分配给任何ADC通道。一个内部的,低抖动和可编程的时钟分频器使得所有操作都可以使用一个时钟源模式。HMCAD1511基于专有结构,采用内部参考电路、串行控制接口和串行LVDS/RSDS输出数据。数据和帧同步时钟用于数据捕获在接收器处。内部1至50倍数字粗增益,ENOB>7.5至16倍增益,允许数字实现示波器增益设置。内部数字精细增益可以为每个ADC单独设置,以校准增益误差。可以通过串行控制接口(SPI)将各种模式和配置设置应用于ADC。每个通道可单独断电,通过此接口可选择数据格式。全芯片闲置模式可由单个外部引脚设置。寄存器设置决定了这个管脚的确切功能。HMCAD1511设计用于方便地与来自多个供应商的现场可编程门阵列(FPGAs)接口。

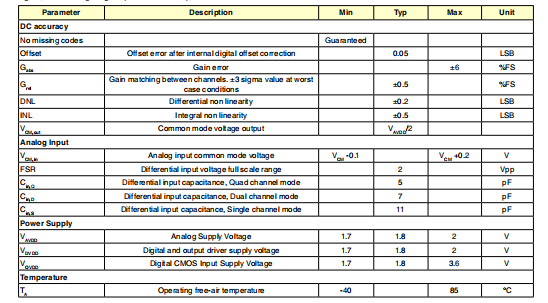

直流规范

AVDD==1.8V,DVDD=1.8V,OVDD=1.8V,FS=125msps,四通道模式,50%时钟占空比,1dbfs 70mhz输入信号,1x/0dB数字增益(精细和粗糙),除非另有说明

启动初始化

作为HMCAD1511通电顺序的一部分,必须进行复位和断电循环,以确保正确的启动初始化。在启动初始化之前,确保电源电压已正确设置正在执行。重置可以通过以下两种方式之一完成:

1.通过在复位引脚(异步)上施加低通脉冲(最小20 ns)。

2.通过使用串行接口将“rst”位设置为高。当这个位子已经设定好了。“rst”位自复位为零。使用此方法时,不要应用任何低通复位引脚上的脉冲。断电循环可通过以下两种方式之一完成:

1.通过在PD引脚上施加高速脉冲(至少20 ns)(异步)。

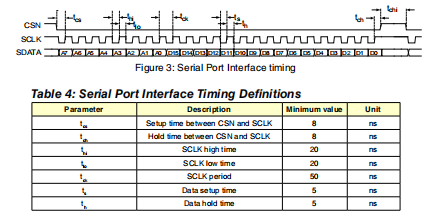

2.循环寄存器0Fhex中的'pd'位到高位(寄存器值'0200'hex),然后再到低位(寄存器值'0000'hex)。串行接口HMCAD1511配置寄存器可通过由管脚SDATA(串行)构成的串行接口访问接口数据)、SCLK(串行接口时钟)和CSN(芯片选择,低电平)。设置CSN时发生以下情况

低:串行数据被转移到芯片中在SCLK的每个上升沿,SDATA上的值被锁定SDATA每24个SCLK上升沿加载到寄存器中一个激活的CSN脉冲中可以加载24位字数据的倍数。如果加载到SDATA在一个活动CSN脉冲期间,仅保留前24位。多余的位被忽略。每24位字分为两部分:前8位构成寄存器地址剩余的16位构成寄存器数据可接受的SCLK频率从20MHz到几赫兹。占空比不必严格控制。

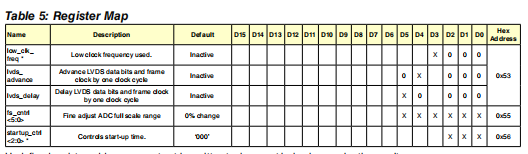

不能写入未定义的寄存器地址;可能会导致不正确的行为。在对寄存器编程时,未使用的寄存器位(空表单元格)必须设置为“0”。当芯片处于断电模式时,所有寄存器都可以写入。这些寄存器在写入时需要断电循环(请参阅启动初始化)。

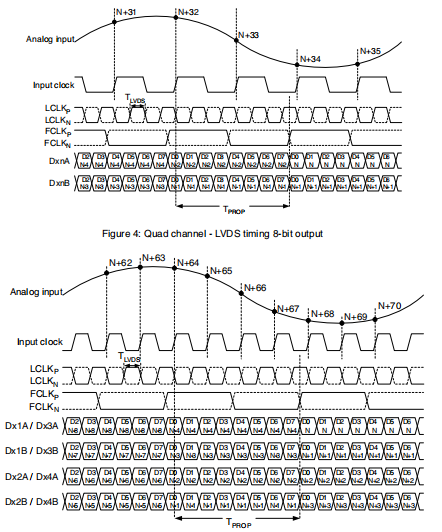

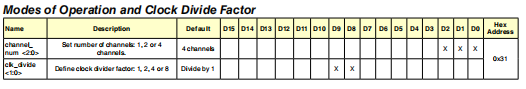

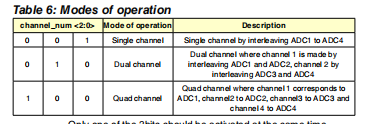

HMCAD1511有三种主要工作模式,由寄存器位通道控制,如表6。断电模式,如“启动初始化”一节所述,必须在更改后或更改期间激活以确保正确操作。所有的工作模式都利用交错来实现高采样速度。四通道模式交错2个ADC分支,双通道模式交错4个ADC分支,而单通道模式交织所有8个ADC分支。

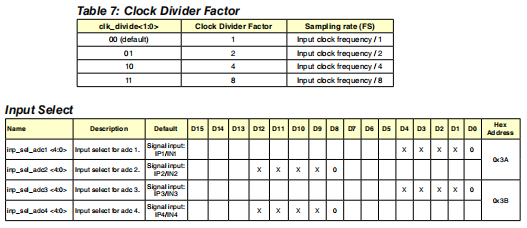

clk_divide<1:0>允许用户应用高于采样率的输入时钟频率。分频器将输入时钟频率除以1、2、4或8的因子,由clk_divide<1:0>寄存器定义。通过设置clk_divide<1:0>值相对于channel_num<2:0>值,相同的输入时钟频率可用于所有频道数量设置。e、 g:当通道数从1增加到4时,最大采样数速率降低了4倍。通过让clk_divide<1:0>跟随channel_num<2:0>值,并将其从1更改为4.内部时钟分频器将在不改变输入时钟频率的情况下降低采样率。

每个ADC通过一个完全灵活的交叉点开关连接到四个输入信号,该开关由inp_sel_adcx设置。单一的通道模式,四个输入中的任何一个都可以选择为单个ADC通道的有效输入。在双通道模式下,可以选择四个输入中的任意两个到每个ADC通道。在四通道模式下,任何输入都可以分配给任何ADC通道。输入的切换可以在正常操作期间完成,并且没有额外的动作是必要的。切换将在每个SPI命令结束时立即发生。

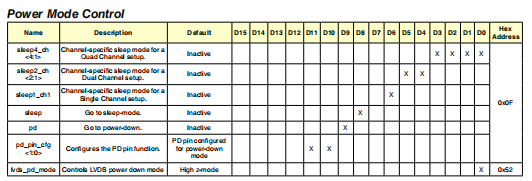

HMCAD1511设备有多种电源管理模式,从启动时间短的睡眠模式到完全启动模式断电,功耗极低。有两种睡眠模式,都有LVDS时钟(FCLK,LCLK)运行,以保持与接收器的同步。第一种是浅睡眠模式(睡眠*_ch)启动时间短,第二个a深度睡眠模式(睡眠),启动时间与完全断电时间相同。设置sleep4_ch<n>='1'将在睡眠模式下的四通道设置中设置通道<n>。设置sleep2_ch<n>=“1”组在睡眠模式下的双通道设置中的通道<n>。设置sleep1_ch1='1'将ADC通道设置为睡眠模式下的单通道设置。这是一种启动时间短的浅睡眠模式。设置sleep='1',使所有通道进入睡眠状态,但保持FCLK和LCLK运行以保持LVDS同步。启动时间与完全断电时间相同。功耗明显低于设定值使用sleep*u ch寄存器来睡眠的所有频道。设置pd='1'将使芯片完全断电,包括带隙基准电路。从这个开始启动时间模式明显长于睡眠模式。与LVDS接收器的同步丢失,因为LCLK和FCLK输出处于高Z模式。设置pdn_pin_cfg<1:0>=“x1”可将电路配置为在PD pin设置为高。这相当于使用sleep*u ch将所有通道设置为休眠。无法关闭通道电源分别使用PD引脚。设置pdn_pin_cfg<1:0>=“10”可将电路配置为在以下情况下进入(深度)睡眠模式PD引脚设置为高(等于设置sleep='1')。当pdn_pin_cfg<1:0>='00'为默认值时,电路进入PD引脚设置为高时的断电模式。

lvds_pd_mode寄存器配置lvds数据输出驱动程序是关机还是保持睡眠状态

和睡眠频道模式。LCLK和FCLK驱动程序不受此寄存器的影响,并且始终处于睡眠和睡眠频道模式。如果lvds_pd_mode设置为low(默认),lvds输出将置于high Z模式,并且驱动程序完全断电。如果lvds_pd_mode设置为high,则lvds输出设置为常数0,并且驱动程序仍处于打开状态在睡眠和睡眠频道模式下。

操作理论

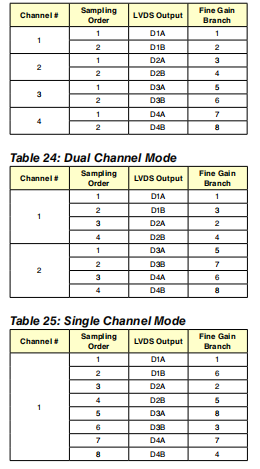

HMCAD1511是一种多模高速CMOS ADC,由8个ADC分支组成,配置为信道模式,使用交织实现高速度采样。出于所有实际目的,该装置可以认为包含4个ADC。好的收益是分别为八个分支调整。HMCAD1511使用LVDS输出,如'寄存器说明,LVDS输出配置和控制”。所需的时钟(FCLK,LCLK)LVDS接口由内部PLL生成。HMCAD1511从一个时钟输入操作,该输入可以是差分的,也可以是单端的。抽样四个通道中的每一个产生时钟使用精心匹配的时钟从时钟输入缓冲树。内部时钟分配器用于在交织期间控制每个ADC的时钟。这个时钟树由操作模式控制。HMCAD1511使用内部生成的引用。微分参考值为1V。这将导致与零对应的-1V差分输入ADC的代码,以及+1V至cor的差分输入响应满标度代码(代码255)。ADC采用流水线转换器结构。每个流水线级将其输出数据馈送到数字纠错逻辑中,确保出色的差分线性,无漏码。HMCAD1511由两套补给和理由。模拟电源和接地装置被识别为AVDD和AVSS,而数字装置被识别为DVD和DVSS。交错效应与采样顺序交错adc将产生交错伪影由之间的增益、偏移和定时不匹配引起ADC分支。HMCAD1511的设计优化以最小化这些影响。不是的不过,为了完全消除不匹配,因此可能需要额外的补偿,尤其是在使用高数字增益设置时。这个内部数字精细增益控制可用于补偿ADC分支之间的增益误差。由于HMCAD1511的优化,没有抽样之间的一一对应关系顺序,LVDS输出顺序和分支编号。表23、24和25概述了相应的分支、LVDS输出和采样顺序对于不同的高速模式。

推荐使用

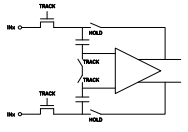

模拟输入HMCAD1511 ADC的模拟输入是一个开关电容跟踪和保持放大器的不同操作优化。在中间电源的共模电压下运行即使性能良好指定的范围。VCM引脚提供适合作为共模电压参考的电压。这个可切换VCM电压的内部缓冲器关闭后,驾驶能力可通过编程改变,使外部vcm bc<1:0>寄存器。

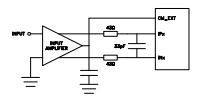

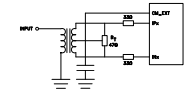

图12显示了输入网络工作的简化图。信号源必须足够低为采样电容器充电的输出阻抗在一个时钟周期内。一个小的外部电阻(例如。建议22欧姆)与每个输入串联因为它有助于减少瞬态电流和阻尼振铃行为。小差动并联电容器电阻器的芯片侧可用于提供动态充电电流,可提高性能。电阻器与电容器,因此值必须由申请要求。直流耦合图13显示了直流耦合。注意,必须根据指定值控制共模输入电压。优选地,CM-EXT输出应用作设置共模电压的参考。

输入放大器可能在一个配套芯片内或者是一个专用的放大器。几个合适的单端到差分驱动放大器存在于市场。系统设计器应确保所选放大器的规格足以整个系统和驾驶能力符合具有HMCAD1511输入规格。详细的配置和使用说明必须是在所选驱动程序的文档中找到,并且图13中给出的值必须根据对驾驶员的建议进行调整。

可使用信号变压器或串联电容器使交流耦合输入网络。图14显示使用trans former的推荐配置。确保变压器有足够的选择线性,并且变压器是合适的。带宽应该优选地超过ADC的采样率多次。同样重要的是尽量减少差分ADC输入之间的相位不匹配HD2性能。这种变压器耦合在一起输入是高频的首选配置信号作为大多数差分放大器在高频时没有足够的性能。变压器和PCB线路之间的磁性连接可能影响信道串扰,因此必须采取在印刷电路板布局时考虑。