特点和优点

▪ 低RDS(开)输出

▪ 自动电流衰减模式检测/选择

▪ 混合和慢电流衰减模式

▪ 低功耗同步整流

▪ 内部UVLO和热关机电路

▪ 交叉电流保护

说明

A3984是一个完整的微步马达驱动器,内置翻译,操作简单。它设计用于在全阶、半阶、四阶和十六阶模式下操作双极步进电机,输出驱动容量高达35 V和±2 A。A3984包括一个固定关闭时间的电流调节器,该电流调节器能够在慢衰减模式或混合衰减模式下操作。

翻译是A3984易于实现的关键。只需在步进输入端输入一个脉冲就可以驱动马达一个微步。没有相序表、高频控制线或复杂的编程接口。A3984接口非常适合复杂微处理器不可用或负担过重的应用。

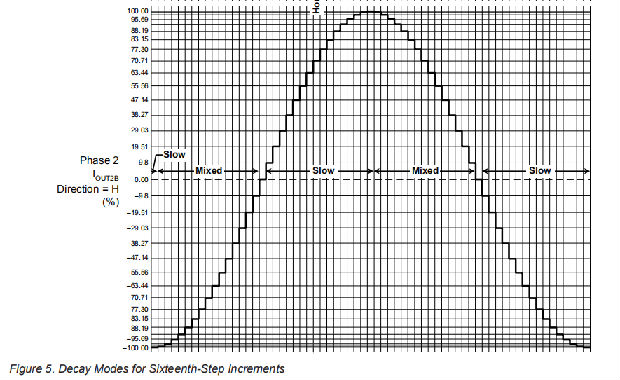

A3984中的斩波控制自动选择电流衰减模式(慢速或混合)。当在步进输入引脚处出现信号时,A3984确定该步进是否在每个电机相位中产生更高或更低的电流。如果更改为更高的电流,则衰减模式设置为慢速衰减。如果更改为较低电流,则电流衰减设置为混合(设置最初为固定关闭时间的31.25%的快速衰减,然后为剩余关闭时间的缓慢衰减)。这种电流衰减控制方案可以降低电机的可听噪声,提高步进精度,降低功耗。

提供内部同步整流控制电路,以改善在脉宽调制操作期间的功耗。

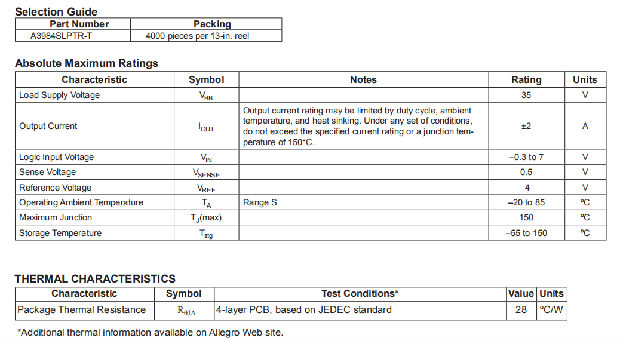

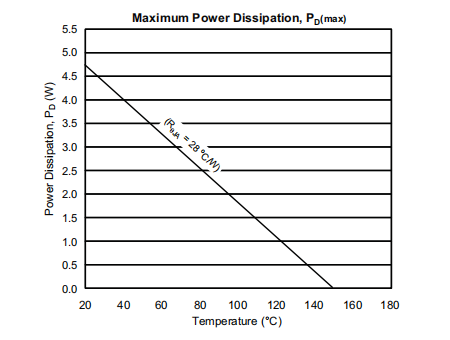

绝对最大额定值

内部电路保护包括:滞后热关机、欠压锁定(UVLO)和交叉电流保护。不需要特殊的通电顺序。

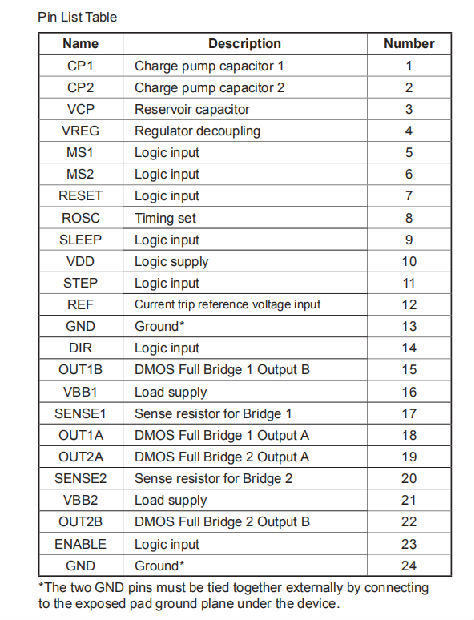

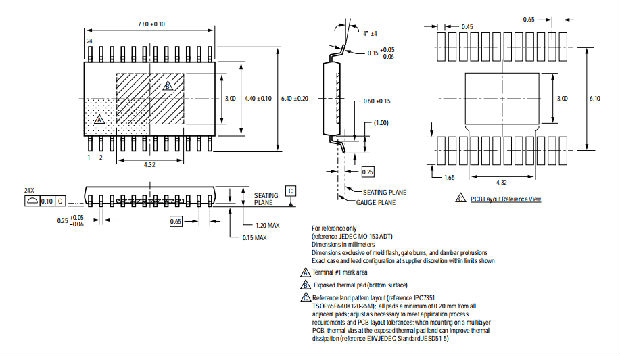

A3984采用低剖面(最大1.2 mm)、24针TSSOP和外露热垫(LP包)供应。不含铅,100%哑光镀锡引线框架。

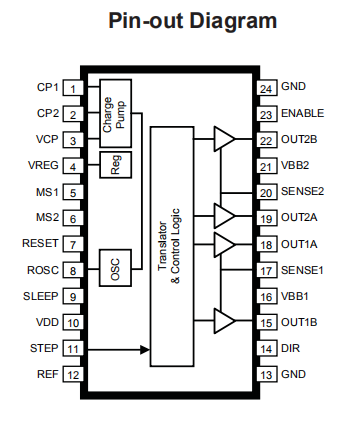

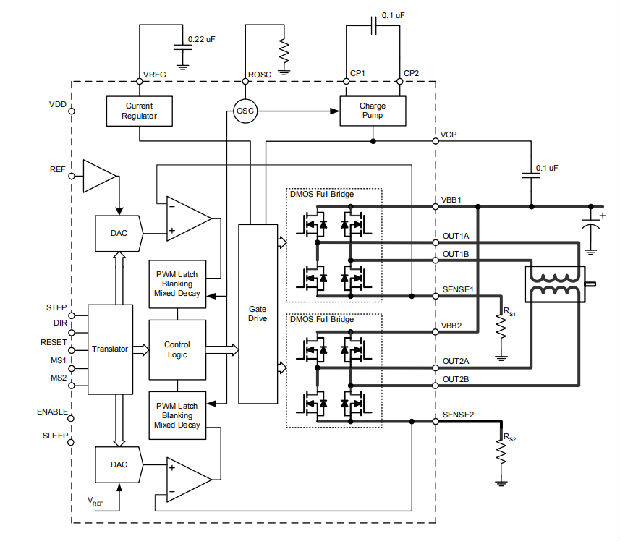

功能框图

功能描述

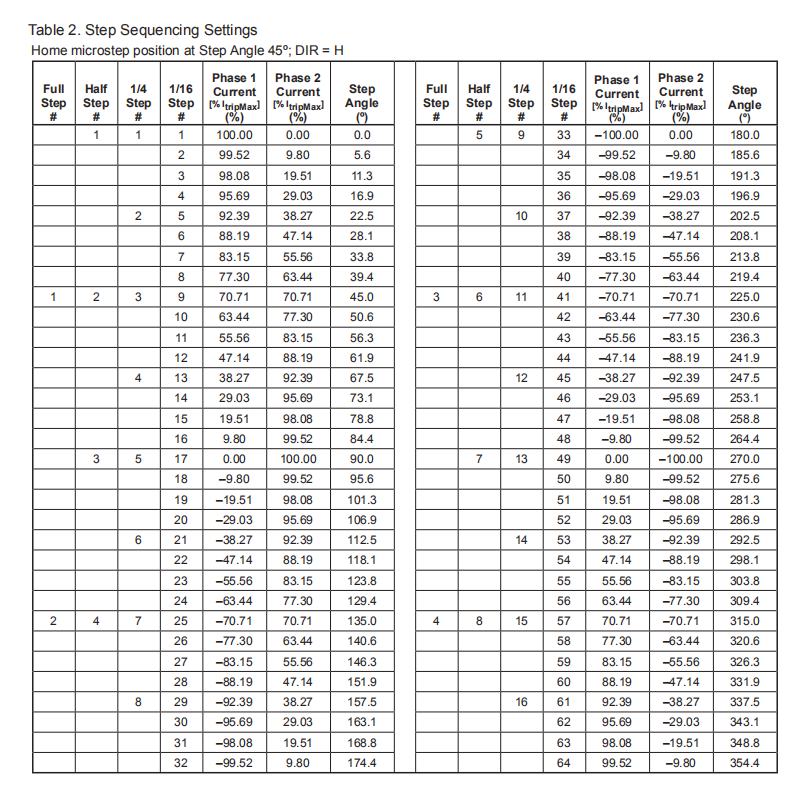

设备操作。A3984是一个完整的微步马达驱动器,带有一个内置的转换器,操作简单,控制线最少。它被设计成在全阶、半阶、四阶和十六阶模式下操作双极步进电机。两个输出全桥和所有N通道DMOS场效应晶体管中的电流通过固定的关断时间PMW(pulse width modulated)控制电路进行调节。在每个步骤中,每个全桥的电流由其外部电流检测电阻器(RS1或RS2)、参考电压(VREF)和其DAC的输出电压(依次由转换器的输出控制)的值设置。

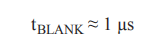

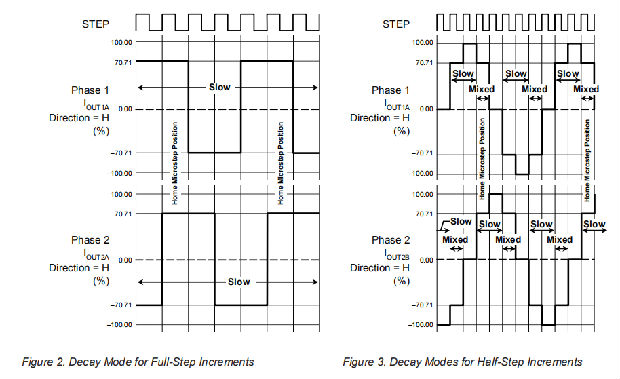

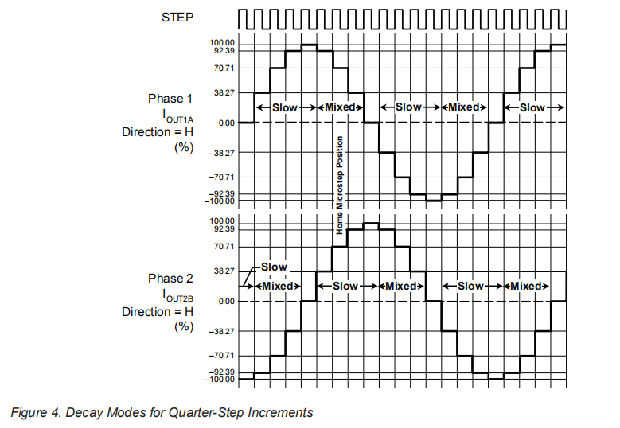

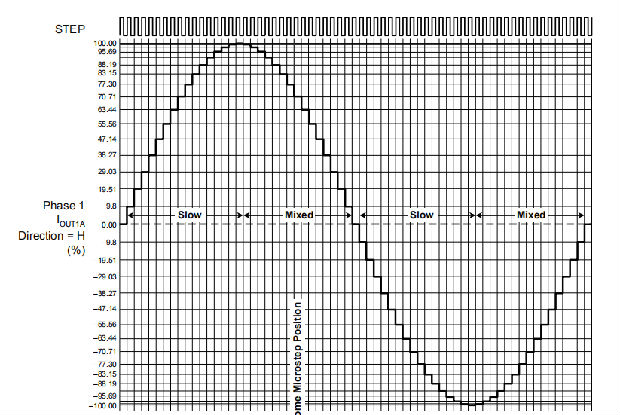

在通电或复位时,转换器将DAC和相电流极性设置为初始初始状态(如图2至图5所示),并将电流调节器设置为两个相的混合衰减模式。当阶跃输入上出现阶跃指令信号时,转换器自动将DAC排序到下一级和当前极性。(当前电平序列见表2)微步分辨率由输入MS1和MS2的组合效应设置,如表1所示。

步进时,如果DAC的新输出电平低于其以前的输出电平,则活动全桥的衰减模式设置为混合。如果dac的新输出电平高于或等于其先前的电平,则活动全桥的衰减模式设置为慢速。这种自动电流衰减选择通过减少由电机反电动势引起的电流波形失真来改善微步进性能。

复位输入(复位)。重置输入将转换器设置为预定义的初始状态(如图2至图5所示),并关闭所有DMOS输出。所有阶跃输入将被忽略,直到重置输入设置为高。

步骤输入(步骤)。步进输入上的一个从低到高的转换使翻译器按顺序排列,并使马达前进一个增量。转换器控制DAC的输入和每个绕组中的电流流向。增量的大小由输入MS1和MS2的组合状态决定。

微步选择(MS1和MS2)。选择微步格式,如表1所示。MS2具有50 kΩ下拉电阻。对这些输入所做的任何更改在下一步上升边缘之前都不会生效。

方向输入(DIR)。这决定了马达的旋转方向。低时,方向为顺时针,高时,方向为逆时针。对该输入的更改在下一步上升边缘之前不会生效。

内部脉宽调制电流控制。每个全桥都由一个固定的断开时间的PWM电流控制电路控制,该电路将负载电流限制在理想值ITRIP。最初,启用一对对角的源和汇DMO输出,电流流过电机绕组和电流检测电阻器RS。当跨过R的电压与DAC输出电压相等时,电流检测比较器重置PWM锁存器。然后,闩锁关闭源DMOS fet(在慢衰减模式下)或接收器和源DMOS fet(在混合衰减模式下)。

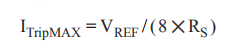

电流限制的最大值是通过选择RS和VREF引脚的电压来设置的。跨导函数由电流限制的最大值itrimax(A)近似,该值由:

其中RS是感测电阻器的电阻(Ω),V REF是REF引脚(V)上的输入电压。

DAC输出以精确的步骤将VREF输出减少到电流感应比较器,使得:

(每个步骤的%itrimpax见表2。)

不超过SENSE1和SENSE2引脚的最大额定值(0.5 V)至关重要。

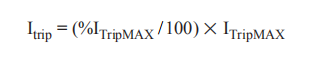

固定的休息时间。内部的脉冲宽度调制电流控制电路使用一个一次性电路来控制DMOS FET保持关闭的持续时间。一次性关闭时间tOFF由从ROSC正时引脚连接到接地的外部电阻器的选择决定。如果ROSCpin与外部电压绑定>3v,则tOFF默认为30μs。

为此,可以将ROSC引脚安全地连接到VDD引脚目的。tOFF(μs)的值约为:

空白。此函数用于清空电流检测的输出内部电流切换输出时的比较器控制电路。比较器输出被隐藏以防止反向恢复电流引起的假过电流检测钳位二极管和与电容有关的开关瞬态负载。空白时间tBLANK(μs)约为:

充油泵(CP1和CP2)。充油泵用于产生大于VBB的栅极电源以驱动源端DMOS门。0.1μF陶瓷电容器,应连接在CP1和CP2之间。此外,0.1μF陶瓷电容器需要在VCP和VBB之间起到储能作用用于操作高端DMOS门。

VREG(VREG)。内部产生的电压用于操作水槽侧DMOS输出。VREG引脚必须是与0.22μF电容器分离接地。VREG在内部监控。在故障情况下,DMOS输出A3984被禁用。

启用输入(启用)。此输入打开或关闭所有DMOS输出。当设置为逻辑高时,输出被禁用。当设置为逻辑低时,内部控制使输出为必修的。转换器还输入STEP、DIR、MS1和MS2作为内部排序逻辑,所有这些都保持活动,独立于启用输入状态。

关闭。发生故障时,温度过高(TJ过高)或欠压(在VCP上),A3984的DMOS输出在排除故障条件之前禁用。通电时UVLO(欠压锁定)电路禁用DMOS输出并将翻译器重置为原始状态。

睡眠模式(睡眠)。当电机不在使用中,该输入将禁用大部分内部电路包括输出DMOS FET,电流调节器,和充油泵。睡眠引脚逻辑低,导致A3984进入睡眠模式。逻辑高允许正常操作,以及启动(此时A3984驱动电机回家微步位置)。当从睡眠模式中出现时,为了使充油泵稳定,在发出Step命令。

混合衰变操作。这座桥可以混合使用衰减模式,取决于步骤顺序,如图所示3到5。当到达触发点时,A3984最初进入31.25%关闭时间的快速衰减模式。托夫。在那之后切换到慢衰减模式为剩余的飞行时间。

同步整流。当一个脉冲宽度调制关闭周期由内部固定-关闭时间周期触发,负载电流接收器根据控制逻辑选择的衰减模式进行计算。此同步整流功能打开电流衰减期间的FET,有效地使身体短路具有低DMOS RDSON的二极管。这显著降低了功率差,并且可以消除对外部肖特基的需要二极管在许多应用中。关闭同步整流当零电流水平为检测。

低压包,24针TSSOP,带外露热垫

Allegro MicroSystems,LLC保留随时根据详细规范要求进行改进的权利,以提高其产品的性能、可靠性或可制造性。在下订单之前,提醒用户确认所依赖的信息是最新的。

Allegro的产品不得用于生命支持设备或系统,前提是合理预期Allegro产品的故障会导致该生命支持设备或系统的故障,或影响该设备或系统的安全性或有效性。

本文提出的交流铜离子注入法是一种可靠的交流铜离子注入法。Allegro MicroSystems,LLC不对其使用承担任何责任,也不对因其使用而产生的任何专利或第三方的其他权利的附带责任。