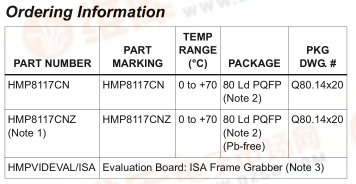

HMP8117点击型号即可查看芯片规格书

656点击型号即可查看芯片规格书

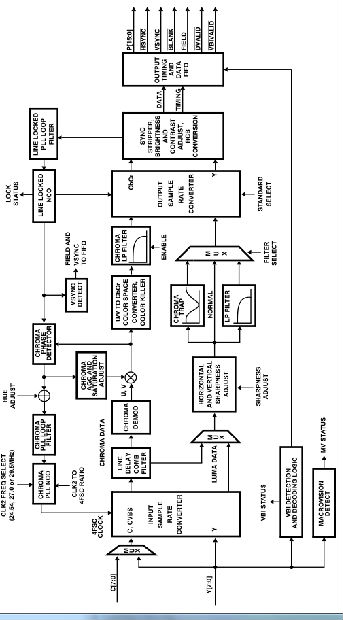

HMP8117是一个高品质的NTSC和PAL视频带内部A/D转换器的解码器。它与NTSC M、PAL B、D、G、H、I、M、N和组合N(N C)视频标准。复合和S-video(Y/C)输入格式都是支持。一个2线梳状滤波器加上一个用户可选择的色度陷阱滤波器提供高质量的Y/C分离。用户调整包括亮度,对比度,饱和度,色调和锐度。垂直消隐间隔(VBI)数据,如闭合字幕,宽屏信号和图文电视,可以是捕获并输出为BT.656辅助数据。关闭字幕和宽屏信号信息也可以通过I 2 C接口读出。录像机8482; 功能提供认可的宏视觉™复制保护旁路和检测。

笔记:

1.Intersil无铅+退火产品采用特殊无铅材料套;模塑化合物/模具连接材料和100%哑光锡平板终端饰面,符合RoHS并兼容同时具有SnPb和无铅焊接操作。Intersil无铅产品在无铅峰值回流焊温度下被归类为MSL满足或超过IPC/JEDEC J STD-020的无铅要求。

2.PQFP也称为QFP和MQFP。

特征

(M)NTSC和(B,D,G,H,I,M,N,N C)PAL操作-视频标准的可选自动检测-ITU-R BT.601(CCIR601)和方形像素操作

视频分析仪功能-宏观视觉™ 旁路和检测数字抗混叠滤波器断电模式数字输出格式-VMI兼容-8位,16位4:2:2 YCbCr-15位(5,5,5),16位(5,6,5)RGB-线性或伽马校正-8位BT.656模拟输入格式-三个模拟复合输入-模拟Y/C(S-video)输入“原始”(过采样)VBI数据捕获“切片”VBI数据捕获功能-闭路字幕-宽屏信号(WSS)-BT.653系统B、C和D图文电视-北美广播电视文本(NABTS)-世界系统图文电视(WST)2线(1H)梳状过滤器Y/C分离器快速I 2 C接口提供无铅加退火(符合RoHS)

应用

多媒体PC

视频会议

视频压缩系统

视频安全系统

液晶投影仪和顶置面板

介绍

HMP8117设计用于解码基带合成或S-video NTSC和PAL信号,并将其转换为数字YCbCr或RGB数据。除了表演基本的解码操作,这些设备包括硬件解码不同类型的VBI数据生成全屏蓝色、黑色和彩色条形图案。数字锁相环用于与所有NTSC和PAL同步标准。色度锁相环用于保持用锁相环实现色度解调保持垂直空间对齐。锁相环的设计在VCR磁头开关、VCR存在时保持锁定技巧模式和多径噪声。HMP8117为宏视觉(MV)复制保护旁路和检测。外部视频处理在视频信号数字化之前,解码器有一些需要的外部处理注意事项演说。本节讨论HMP8117。模拟视频输入HMP8117支持三个组合或两个复合和一个S-视频输入。三个模拟视频输入(CVBS 1-3)用于选择三个复合视频源中的哪一个解码。为了支持S-video应用程序,Y通道驱动CVBS3(Y)模拟输入,C通道驱动C模拟输入。模拟输入必须与视频信号交流耦合,如应用程序部分所示。

抗混叠滤波器

虽然提供了23抽头数字半带抗混叠滤波器对于每个A/D通道,外部无源滤波器是推荐最佳性能。数字滤波器具有5.4MHz的平坦响应,约为-3dB使用27MHz输入CLK2样本的6.3MHz带宽速度。对于CVBSx输入,滤波器连接在你和阴针。对于C(色度)输入,反-别名过滤器应该在C输入之前连接。推荐的过滤器配置显示在参考图20中的示意图。这些过滤器是平的响应频率为4.2兆赫,约为-3分贝带宽8MHz。如果从HMP8115升级或HMP8112A,可以使用以前的滤波器配置但带宽略有下降。其他更高或低性能滤波器配置可以被替代。视频数字化在A/D转换之前,输入信号被偏移并缩放到已知视频级别。数字化后,采样率转换器梳状滤光片用于分色和解调。A/D转换每个CVBSX视频输入通道都有一个视频钳位电路这与PLL定时无关。输入夹提供在a/D中定位同步端的粗略信号偏移量转换器采样范围,以便AGC和DC-恢复逻辑可以运行。A/D转换视频数据以CLK2频率采样,然后进行处理通过输入采样率转换器。的输出级别AGC和直流恢复处理后的ADC为:

AGC和直流恢复

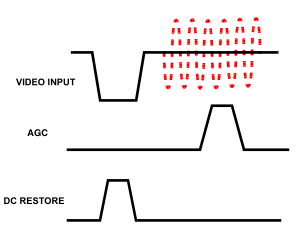

AGC放大器衰减或放大模拟视频信号以确保空白电平生成代码56或59。取决于视频标准。不同于理想空白水平56或59用于控制模拟视频信号的衰减或增益。获得数字低通滤波器AGC的稳定直流基准从输入信号的后廊移除色度突发。直流还原定位视频信号,以便同步提示生成代码0。AGC的内部定时窗口直流恢复如图3所示。适当的当输入信号自动检测或手动选择。

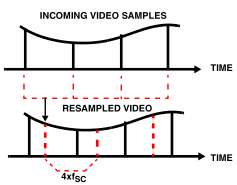

输入信号检测如果连续16行未检测到输入视频信号周期,为先前的检测到或编程的视频标准。面具在“输入信号丢失”的情况下提供中断允许主机在需要时启用蓝场输出。垂直同步和场检测垂直同步和磁场检测电路使用较短的时间计数器,用于检测视频中的垂直同步序列数据流。低时间计数器累积低时间在任何同步脉冲期间遇到,包括锯齿和均衡脉冲。当低时间计数超过垂直同步检测阈值,VSYNC已断言立刻。字段同时断言已断言VSYNC。对于奇数字段和即使是田野也很高。字段由中的位置确定检测到VSYNC的视频线。如果VSYNC是在测线的前半部分检测到,该字段为奇数。如果VSYNC在一行的后半部分被检测到,场是均匀的。如果失去垂直同步或噪音过大防止检测到垂直同步,字段输出将继续切换。如果在337之后行,未检测到1或3的垂直同步周期(可选)由GENLOCK控制寄存器04 H。当这种情况发生时PLL初始化为采集状态。Y/C分离复合视频信号具有luma(Y)和chroma(C)信息混合在同一视频信号中。Y/C分离过程负责分离将视频信号合成为这两个分量。这个HMP8117使用梳状滤波器来最小化与Y/C分离过程相关。输入采样率转换器输入采样率转换器用于转换视频数据以CLK2速率采样到虚拟4xf SC采样速率梳状滤波和颜色解调。插值滤波器是用于生成4xf SC示例,如图2所示。

梳状滤波器

使用单线延迟的2线梳状滤波器执行Y/C分离过程的一部分。S-video期间操作时,Y信号绕过梳状滤波器;C信号由梳状滤波器处理,因为它是色度解调器。在PAL操作期间,色度还应启用陷阱过滤器以提高性能。由于使用的是单行存储,因此色度通常与luma数据有半行垂直偏移。今年五月消除,垂直校准色度和亮度样品,以牺牲luma的垂直分辨率为代价。钻头输出格式寄存器02 H的0控制该选项。色度解调梳状滤波器的输出使用获得专利的频域转换以完成Y/C分离并解调色度。解调是在虚拟4xfsc采样率下进行的,使用插值数据采样以生成U和V数据。这个解调过程由2个U/V采样率决定。输出采样率转换器输出采样率转换器转换Y、U和V数据从虚拟4xf SC采样率到所需的输出采样速率(即13.5MHz)。它还垂直对齐基于数字视频中嵌入的水平同步信息数据流。输出采样率由输入决定视频标准和选定的矩形/方形像素模式。输出像素速率是CLK2输入时钟的1/2频率。除使用4:4:4输出格式的RGB模式。CLK2输入解码器需要CLK2的稳定时钟源输入。为了获得最佳性能,使用终端电阻器最小化脉冲超调和CLK2输入上的反射。由于色度解调使用虚拟4xf SC,因此何抖动在CLK2上,将作为色度误差在输出像素。CLK2时钟频率必须是根据视频从下表1中选择的有效选项标准和所需的像素模式。

像素输出端口

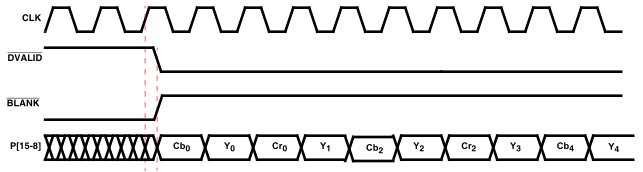

像素数据通过P0-P15引脚输出。参见表4输出管脚定义为输出模式的函数。请参阅“循环打滑和实时”一节“像素抖动”用于PLL和接口考虑。8位YCbCr输出每个YCbCr数据字节输出在CLK2号。Y Cb Cr数据被多路复用为[Cb Y cry′cbyCr Y′…],第一个活动数据包含Cb数据。像素输出定时如图所示。BLANK、HSYNC、VSYNC、DVALID、VBIVALID和FIELD输出跟随CLK2的上升沿。空白时被断言并且VBIVALID被解除断言,YCbCr输出Y的值为16,Cb和Cr的值为128的输出由GENLOCK控制寄存器04 H。

注:

1.Y 0是直线的第一个活动亮度像素数据。Cb 0和cr0是一行中的第一个活动色度像素数据。Cb和Cr将每由于4:2:2子采样而循环。像素数据在消隐期间不输出,但值被迫消隐水平。

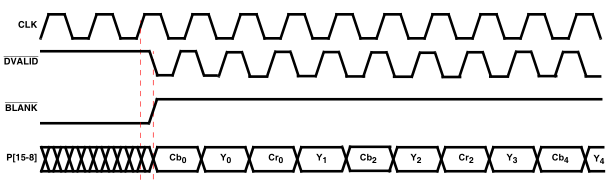

16位YCbCr、15位RGB或16位RGB输出对于16位YCbCr、15位RGB数据或16位RGB输出模式,数据输出跟随CLK2的上升沿已断言DVALID。线性或伽马校正可以输出RGB数据。像素输出定时如所示图10至13。BLANK、HSYNC、VSYNC、DVALID、VBIVALID和FIELD输出跟随CLK2的上升沿。空白时被断言并且VBIVALID被解除断言,YCbCr输出Y的值为16,Cb和Cr的值为128;RGB输出值为0。DVALID输出的行为由位4决定(DVLD_LTC)和GENLOCK的位5(DLVD_DCYC)控制寄存器04 H

笔记:

2.Y 0是直线的第一个活动亮度像素数据。Cb 0和cr0是一行中的第一个活动色度像素数据。Cb和Cr将每由于4:2:2子采样而循环。像素数据在消隐期间不输出,但值被迫消隐水平。

3.当DVLD_LTC设置为1时,DVALID的极性需要设置为active low,否则DVALID在活动视频期间将保持低电平,并且只有在消隐期间才用时钟进行选通。

图文电视

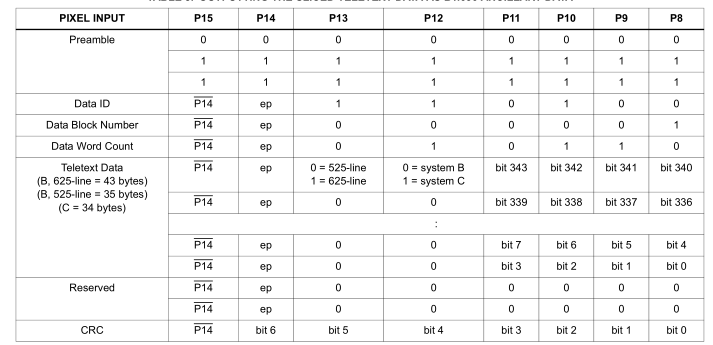

HMP8117支持ITU-R BT.653 625线和525线图文电视系统B,C和D捕捉。NABTS(北美广播图文规范)与BT.653相同525线系统C,也用于传输英特尔跨播™ 信息。WST(World System Teletext)是与BT.653系统B相同。图16显示了包含图文电视数据的视频信号的结构。监控包含图文信息的扫描线。如果启用了teletext并且存在teletext数据,则teletext数据作为BT.656辅助数据输出。图文电视检测teletext解码器监视扫描线,查找16位时钟磨合(有时称为时钟同步码)。如果找到,它会锁定时钟运行时,图文电视数据被采样并加载到移位寄存器,然后将数据传输到内部保存寄存器。如果找不到时钟磨合,则假定扫描线包含视频数据,除非检测到其他VBI信息,例如WSS。如果在23号线或289号线之前发现NTSC和(M)PAL,或(B、D、G、H、I、N、N C)PAL的336线,VBI Teletext检测状态位立即设置为“1”。如果没有通过这些行找到,状态位立即重置为“0”。访问图文电视数据teletext数据必须作为BT.656辅助数据输出。I 2 C接口没有输出带宽需要时提供图文信息。说明了teletext BT.656辅助数据格式图描述了传入的电信文本的部分作为辅助数据的一部分进行切片和输出的信号。在水平方向包含电传文本的行后的消隐间隔信息。实际的BT.656字节包含teletext数据只包含实际数据包的4位。请注意只有图16的数据包作为辅助数据发送;数据流中不包括时钟磨合。

笔记:

4.MSB是位号:对于系统C为271,对于系统B 525行为279,对于系统B 625行为343。

5.两个系统的时钟运行范围均为16位,不包括在BT.656辅助数据流中。

6.在525/60系统上,B和C系统的比特率分别为5.727272mbits/s和625/50系统的比特率分别为6.9375和5.734375mbits/s。

7.图文电视VBI视频信号

笔记:

8.ep=P8-P13的偶数奇偶校验。

9.CRC=通过最后一个用户数据字的数据ID的P8-P14之和。预设为所有零,忽略进位。

10.对于525线系统B,位280-343为“0”。

11.对于系统C,位272-343为“0”。

“原始”VBI数据捕获空白扫描线期间VBI数据的“原始”数据捕获可以选择性地实现。在本例中,活动的以CLK2速率对空白扫描线的行时间进行采样,输出到像素输出。这允许软件对VBI数据进行解码。行掩码寄存器指定要在哪些扫描行上生成“原始”VBI数据。如果启用了原始VBI All位,则视频线被视为原始VBI数据,不包括均衡线和锯齿线。捕获“原始”VBI数据的开始和结束时间扫描线由起始和结束的原始VBI决定登记册。这允许正确捕获“原始”VBI数据不考虑活动视频的空白输出定时。从“原始”VBI数据中减去空白级别采样,结果输出到像素输出。注“切片”和“原始”VBI数据都可以在同一条线。在NTSC操作期间,VBI数据的第一行可能是第10行和第272行,最后一个可能的行是最后一个空白扫描线。第1-9行和第264-271行始终是平淡无奇。

实时控制接口

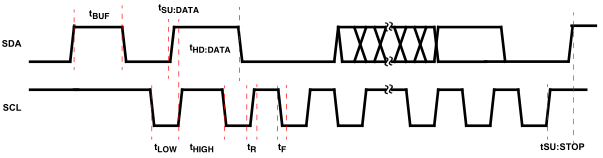

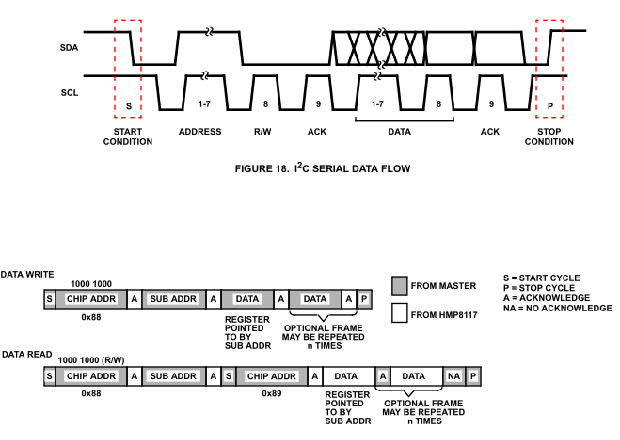

实时控制接口(RTCI)输出定时作为BT.656辅助设备的NTSC/PAL编码器的信息数据。这允许编码器生成“干净”输出视频。表中显示了通过BT.656辅助数据获得的RTCI信息9号。如果启用,则此传输每行发生一次,并且在SAV序列开始之前完成。对于NTSC编码,PSW位始终为“0”。在PAL期间编码,表示V的符号(“0”=负数;“1”=正)扫描线。主机接口所有内部寄存器都可以写入或由主机读取任何时候的处理器,除了那些标识为只读。控制寄存器的位描述如下从表10开始列出。HMP8117支持快速模式(高达400kbps)I 2 C由SDA和SCL引脚组成的接口。装置用作通过串行接口。当接口未激活时,SCL和必须使用外部4kΩ上拉将SDA拉高电阻器。SA输入引脚确定HMP8117。如果SA引脚拉低,则地址为1000100x乙。如果通过10kΩ的拉力将SA销拉高-上电阻,地址是1000101xB。(在地址是i2cread标志。)当SCL线路低且当SCL线拉高时保持稳定。更改SCL高时SDA线路的状态将解释为I 2 C总线启动或停止条件,如所示图。在I 2 C写入周期中,从机之后的第一个数据字节地址被视为控制寄存器子地址,并且写入内部地址寄存器。任何剩余数据在I 2 C写入周期中发送的字节被写入控件寄存器,从地址寄存器,如第一个字节所示。地址然后寄存器在每个附加数据之后自动递增在写周期中在I 2 C总线上发送的字节。写入寄存器或保留寄存器中的保留位是忽略。

为了执行从特定控制寄存器的读取在HMP8117中,I 2 C总线写入必须首先是执行以正确设置地址寄存器。然后一个可以执行I 2 C总线读取以从所需的控制寄存器。由于需要读取周期实际上有两种启动条件如图所示。地址寄存器是在I 2 C读取期间,每读取一个字节后自动递增循环。保留寄存器返回值00 H