1212点击型号即可查看芯片规格书

AD5532HS点击型号即可查看芯片规格书

特征

高集成度:1212平方毫米LFBGA中的32通道DAC;保证单调;与DSP/微控制器兼容的串行接口;信道更新率1.1兆赫;输出阻抗0.5;可选输出电压0 V至5 V或-2.5 V至+2.5 V异步复位设备;温度范围-40 C至+85 C。

应用

光网络;水平设置;仪表;自动测试设备;工业控制系统;数据采集;低成本I/O。

一般说明

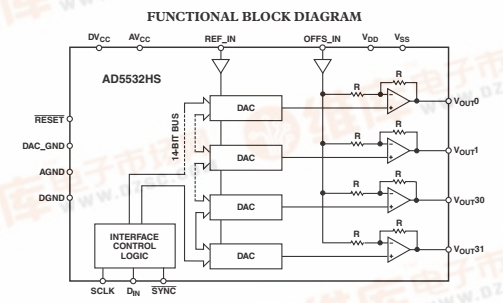

AD5532HS是一个32通道电压输出14位DAC,具有高速串行接口。选定的DAC寄存器通过3线接口写入。串行接口以高达30兆赫的时钟频率工作,并与数字信号处理器和微控制器接口标准兼容。输出电压范围为0 V至5 V或-2.5 V至+2.5 V,由插脚上的OFFS_处的偏移电压确定。由于输出放大器的净空,它被限制在V+2 V到V–2 V的范围内。

该装置在AV=5 V±5%,DV=2.7 V至5.25 V,V=-4.75 V至-12 V和V=+4.75 V至+12 V的条件下运行,并要求参考电压稳定在2.5 V。

产品亮点

1、32个14位DAC在一个包,保证单调。

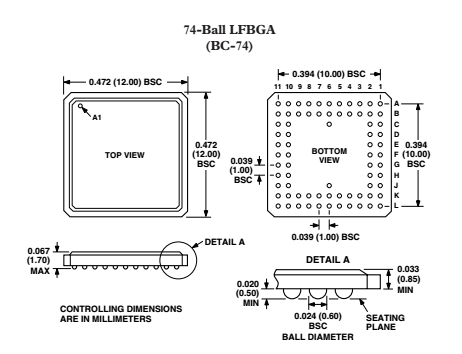

2、AD5532HS采用74球LFBGA封装,机身尺寸为12毫米x 12毫米。

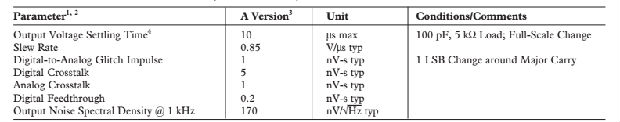

交流特性(VDD=+4.75 V至+12 V,VSS=-4.75 V至-12 V;AVCC=4.75 V至5.25 V;DVCC=2.7 V至5.25 V;AGND=DGND=DAC_GND=0 V;REF_IN=2.5 V;所有输出均为空载。所有规格TMIN至TMAX,除非另有说明。)

笔记

1、见术语;

2、由设计和特性保证,不进行生产测试;

3、B型:工业温度范围-40°C至+85°C;

4、从写入序列结束时开始计时。规格如有更改,恕不另行通知。

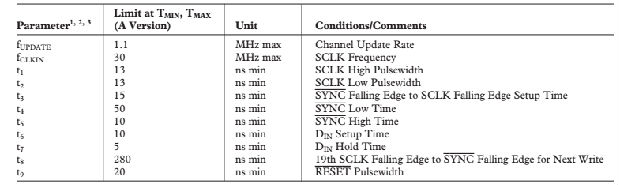

定时特性(VDD=+4.75 V至+12 V,VSS=-4.75 V至-12 V;AVCC=4.75 V至5.25 V;DVCC=2.7 V至5.25 V;AGND=dgd=DAC_GND=0 V;所有规格TMIN至TMAX,除非另有说明。)

笔记

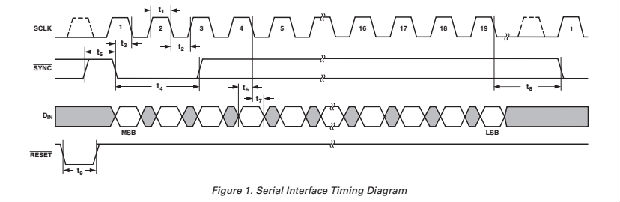

1、参见图1中的时序图。

2、由设计和特性保证,不进行生产测试。

3、所有输入信号的规定值为t=t=5ns(DV的10%至90%),并从(V+V)/2的电压电平开始计时。规格如有更改,恕不另行通知。

术语

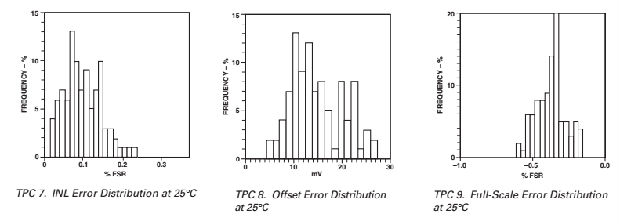

积分非线性(INL)

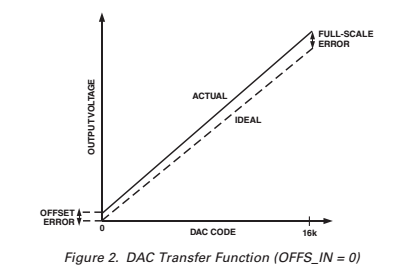

通过DAC传递函数端点的直线最大偏差的测量。它表示为满量程的百分比。

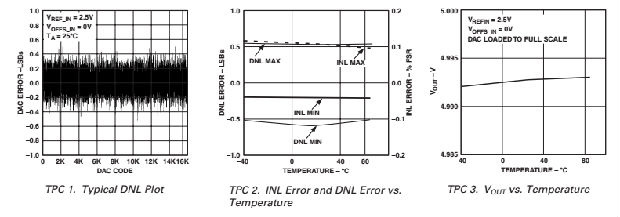

微分非线性(DNL)

任何两个相邻码之间的测量变化和理想1lsb变化之间的差异。指定的DNL最大值为±1 LSB,确保单调性。

偏移误差

在所有0都加载到DAC的情况下,对设备输出中存在的错误进行测量。它包括DAC和输出放大器的偏移量。以mV表示。

满标度误差

所有1s加载到DAC时输出误差的测量。理想情况下,如果off-IN=0,输出应为2 REF-IN。它表示为满量程的百分比。

直流电源抑制比(PSRR)

一种测量电源电压(V和V)变化时模拟输出变化的方法。用分贝表示。V和V变化为±5%。

直流串扰

一个DAC在中刻度时输出电平的直流变化,以响应全刻度代码变化(全0到全1,反之亦然)和所有其他DAC的输出变化。以微伏表示。

输出温度系数

一种测量模拟输出随温度变化的方法。以ppm/℃表示。

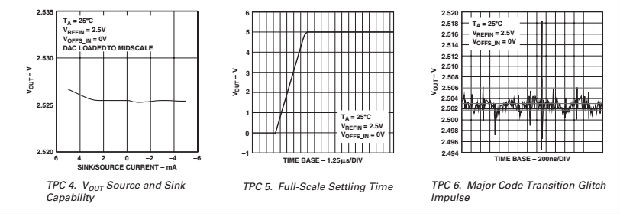

输出电压稳定时间

从最后一个数据位进入DAC直到输出稳定在其最终值的±0.5LSB范围内所用的时间。

数模故障脉冲

当DAC寄存器中的代码改变状态时注入模拟输出的故障区域。它被指定为在主进位转换(011。11到100。00或100。00至011。11) 是的。

数字串扰

当一个满标度的代码变化(所有1到所有0,反之亦然)被写入另一个DAC时,在中标度传输到一个DAC的输出的故障脉冲。它以nV secs表示。

模拟串扰

传输到一个由于另一个的输出(V)的满标度变化而产生的DAC数模转换器。故障区域以nV secs表示。

数字馈通

当部件未被写入时,即同步度高时,从数字控制输入注入模拟输出的脉冲的测量。它以nV secs为单位指定,并在数字输入引脚上以最坏情况变化进行测量,例如从0到1,反之亦然。

输出噪声谱密度

测量内部产生的随机噪声的一种方法。随机噪声的特征是频谱密度(每根赫兹电压)。它是通过将所有dac加载到中刻度并在输出端测量噪声来测量的。测量单位为nV/√Hz。

典型性能特征——AD5532HS

功能描述

AD5532HS在一个包中包含32个DAC。14位数字字通过串行接口加载到32个DAC寄存器中的一个。然后将其转换(带增益和偏移)为模拟输出电压(V0–V31)。

要更新DAC的输出电压,需要的DAC通过串行端口寻址。加载5位DAC地址和14位DAC数据后,选定的DAC转换代码。通电时,所有DAC都加载零。

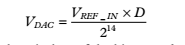

数模转换部分

每个DAC通道的结构由一个电阻串DAC和一个输出缓冲放大器组成。REF_IN管脚处的电压为cor响应DAC提供参考电压。由于DAC的输入编码是直接二进制的,因此理想的DAC输出电压由下式给出:

其中D=加载到DAC寄存器的二进制代码的十进制等效值,即0–16383。

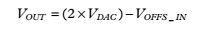

输出缓冲级增益和偏移

输出缓冲阶段的功能是转换0 V–2.5 V的DAC输出,范围更广。这是通过将DAC的输出增加两倍,并通过pin中的电压on off来抵消电压来实现的。

VDAC是DAC的输出。

VOFFS_-IN是管脚中OFFS_处的电压。

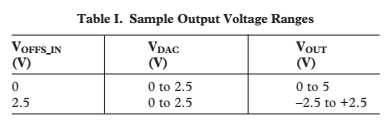

表1显示了输出电压范围与用户提供的偏置电压的关系。

VOUT仅受输出放大器的净空限制。

VOUT必须在最大额定值范围内。

复位功能

AD5532HS上的重置功能可用于将设备上的所有节点重置为开机重置状态。所有dac都加载了0,所有寄存器都被清除。复位功能通过将复位引脚调低来实现。

串行接口

串行接口由三个管脚控制,如下所示:

SYNC:此pin是串行接口的帧同步pin。

SCLK:这个引脚是串行时钟输入。它的工作时钟频率高达30兆赫。

DIN:这个引脚是串行数据输入。SCLK下降沿上的数据必须有效。

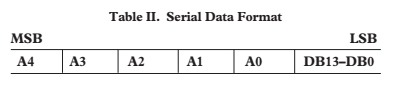

为了更新单个DAC通道,将19位数据字写入AD5532HS。见表二。

A4–A0位

用于对32个通道中的任何一个进行寻址(A4=MSB of address,A0=LSB)。

DB13–DB0位

它们用于将14位字写入寻址DAC寄存器。

图1显示了串行写入AD5532HS的时序图。串行接口可与连续和非连续串行时钟一起工作。SYNC的第一个下降沿重置一个计数器,该计数器对串行时钟的数量进行计数,以确保正确的位数在串行移位寄存器中移入和移出。同步时的任何其他边都将被忽略,直到正确的位数移入或移出。一旦19位移入或移出,SCLK将被忽略。为了进行另一个串行传输,计数器必须通过同步下降沿重置。用户必须允许两次连续写入之间的时间间隔为280 ns(min)(请参阅计时规范)。

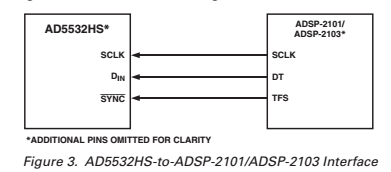

微处理器接口AD5532HS-to-ADSP-21xx接口

ADSP-21xx系列DSP易于与AD5532HS接口,无需额外的逻辑。

启用运动后,通过将一个字写入Tx寄存器来启动数据传输。在写入序列中,数据在DSP串行时钟的每个上升沿上计时,并在SCLK下降沿上计时到AD5532HS。提供AD5532HS所需的19位数据字的最简单方法是从ADSP-21xx发送两个10位数据字。确保数据在TX寄存器中正确定位,以便发送的前19位包含有效数据。运动控制寄存器的设置如下:

TFSW=1,交替帧;

INVTFS=1,有效低帧信号;

DTYPE=00,右对齐数据;

ISCLK=1,内部串行时钟;

TFSR=1,每字帧;

ITFS=1,内部帧信号;

SLEN=1001,10位数据字。

图3显示了连接图。

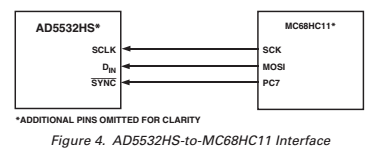

AD5532HS-to-MC68HC11接口

MC68HC11上的串行外围接口(SPI)配置为主模式(MSTR=1)、时钟极性位(CPOL)=0和时钟相位位(CPHA)=1。SPI通过写入SPI控制寄存器(SPCR)进行配置-请参阅68HC11用户手册。68HC11的SCK驱动AD5532HS的SCLK,而MOSI输出驱动AD5532HS的串行数据线(DIN)。同步信号来自端口线(PC7)。当数据被发送到AD5532HS时,同步线被取低(PC7)。显示在MOSI输出上的数据在SCK下降沿上是有效的。68HC11在每个串行传输操作期间仅传输8位数据;因此,需要三个连续的写入操作来传输19位数据。首先传输数据MSB。务必左对齐SPDR寄存器中的数据,以便传输的前19位包含有效数据。必须将PC7拉低才能开始传输。在任何进一步的写入周期发生之前,它会被调高并再次拉低。见图4。

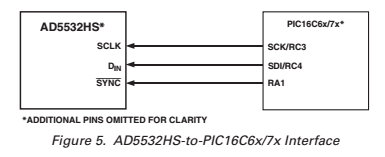

AD5532HS-to-PIC16C6x/7x接口

PIC16C6x/7x同步串行端口(SSP)被配置为时钟极性位为0的SPI主机。这是通过写入同步串行端口控制寄存器(SSPCON)来完成的。请参阅用户PIC16/17微控制器用户手册。在此示例中,I/O端口RA1用于脉冲同步并启用AD5532HS的串行端口。该微控制器在每个串行传输操作期间仅传输8位数据;因此,需要三个连续的写入操作来传输19位数据。首先传输数据MSB。务必左对齐SPDR寄存器中的数据,以便传输的前19位包含有效数据。RA1必须被拉低才能开始转移。在任何进一步的写入周期发生之前,它会被调高并再次拉低。图5。

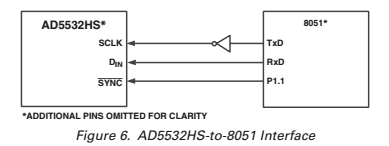

AD5532HS-to-8051接口

AD5532HS需要与串行数据同步的时钟。因此,8051串行接口必须在模式0下操作。在此模式下,串行数据从8051到RxD退出,并在TxD上输出移位时钟。同步信号来自端口线(P1.1)。图6显示了8051是如何连接到AD5532HS的。由于AD5532HS将移位时钟上升沿上的数据移出,并将数据锁定在下降沿上,因此移位时钟必须反转。还要注意,AD5532HS首先需要其带有MSB的数据。因为8051首先输出LSB,所以发送例程必须考虑到这一点。

应用电路

光网络控制环路中的AD5532HS

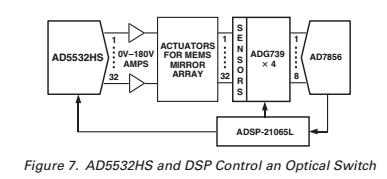

AD5532HS可用于需要大量dac来执行控制和测量功能的光网络应用中。在图7所示的电路中AD5532H的0 V–5 V输出被放大到0 V–180 V,然后用于控制驱动器,以确定光开关中MEMS反射镜的位置。每个镜子的确切位置是用传感器测量的。使用四个双4通道矩阵开关(ADG739)对传感器读数进行调制,并反馈给8通道14位ADC(AD7856)。

控制回路由ADSP-21065L驱动,该ADSP-21065L是一个32位SHARC数字信号处理器,具有SPI兼容的运动接口。它将数据写入DAC,控制多路复用器,并通过3线串行接口从ADC读取数据。

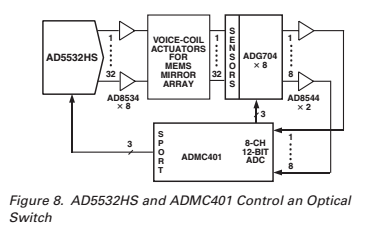

或者,AD5532HS可以由ADMC401电机控制器驱动,如图8中的控制回路所示。DAC输出被馈入八个AD8534四跨导放大器,以产生用于确定后视镜位置的音圈执行器的电流。测量每个反射镜的准确位置,并将读数混入ADMC401的片上8通道ADC中。

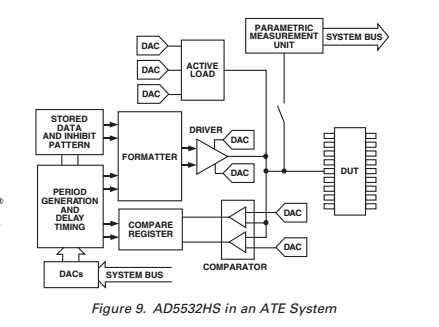

典型ATE系统中的AD5532HS

AD5532HS非常适合用于自动测试设备。需要几个dac来控制pin驱动器、比较器、有源负载和信号定时。传统上,在这个应用中使用采样和保持装置。

AD5532HS具有以下优点:无需刷新,无下垂,消除基座误差,无需额外滤波消除故障。在较小的区域实现更高级别的集成(见图9)。

电源去耦

在任何精度很重要的电路中,仔细考虑电源和接地回路布局有助于确保额定性能。安装AD5532HS的印刷电路板的设计应使模拟和数字部分分开,并限制在板的某些区域。如果AD5532HS位于多个设备需要AGND到DGND连接的系统中,则应仅在一个点进行连接。星形接地点应尽可能靠近设备。对于带有多个引脚(V、V、AV)的电源,建议将这些引脚连接在一起。AD5532HS应具有10μF的充足电源旁路,并与每个电源上的0.1μF并联,每个电源应尽可能靠近封装,理想情况下应紧靠设备。10μF电容器为钽珠型。0.1μF电容器应具有低有效串联电阻(ESR)和有效串联电感(ESI),与提供高频低阻抗接地路径的普通陶瓷类型一样,以处理内部逻辑开关产生的瞬态电流。

AD5532HS的电源线应使用尽可能大的迹线,以提供低阻抗路径,并减少故障对电源线的影响。时钟等快速开关信号应使用数字接地屏蔽,以避免将噪声辐射到电路板的其他部分,且不得在参考输入附近运行。在D线和SCLK线之间布线的地线将有助于减少它们之间的串扰(多层板上不需要,因为将有一个单独的接地平面,但分离这些线将有助于)。必须尽量减少REF_IN上的噪音。在避免数字和模拟信号交叉。板的相对侧上的痕迹应彼此成直角。这减少了通过电路板的馈通效应。微带技术是目前为止最好的,但并不总是可能与双面板。在这种技术中,电路板的组件侧专用于接地平面,而信号线则放置在焊料侧。

与所有薄包装一样,在组装过程中,必须注意避免包装弯曲,避免包装表面的点荷载。

外形尺寸

尺寸单位为英寸和(mm)。