6N137点击型号即可查看芯片规格书

4661点击型号即可查看芯片规格书

5000点击型号即可查看芯片规格书

3750点击型号即可查看芯片规格书

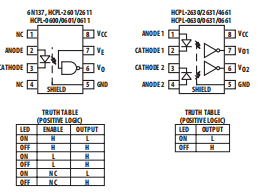

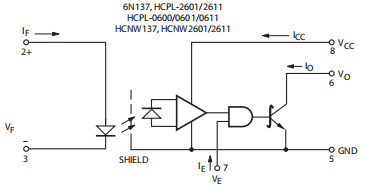

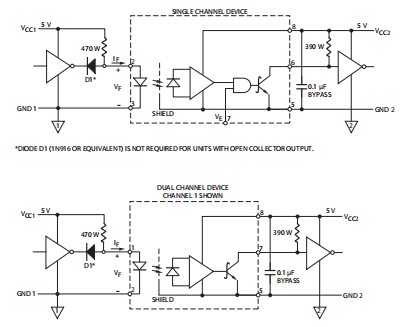

6N137、HCPL-26xx/06xx/4661、HCNW137/26x1为结合GaAsP发光的光耦合栅极二极管和集成高增益光电探测器。使能。输入允许探测器被频闪。的输出探测器集成电路是一种开集电极肖特基箝位晶体管。内屏蔽提供有保证的共模;Vcm下高达15000 V/s的瞬态抗扰度规范100伏。这种独特的设计提供了最大的交流和直流电路在实现TTL兼容性的同时隔离。光耦。交流和直流操作参数由允许无问题的系统性能。

特征

15 kV/μs最小共模抑制(CMR)对于HCNW2611、HCPL-2611、HCPL-4661,VCM=1千伏,HCPL-0611、HCPL-0661高速:典型的10 MBd与LSTTL/TTL兼容低输入电流能力:5毫安保证的超温交直流性能:–40°C至+85°C提供8针浸渍、SOIC-8、宽体包装频闪输出(仅单通道产品)安全批准-UL认可-1分钟3750 Vrms和5000 Vrms根据UL1577 CSA认证(5000 Vrms/1),持续1分钟分钟额定值适用于HCNW137/26X1和选项020[6N137、HCPL-2601/11/30/31、HCPL-4661]产品仅限)-经批准的IEC/EN/DIN EN 60747-5-5

VIORM=567 V峰值,用于06xx选项060

VIORM=630 V峰值,用于6N137/26xx选项060对于HCNW137/26x1,VIORM=1414 V峰值

提供MIL-PRF-38534密封型(HCPL-56xx/66xx)

应用

隔离线接收器

计算机外围接口

微处理器系统接口

用于A/D、D/A转换的数字隔离

开关电源

仪表输入/输出隔离

接地回路消除

更换脉冲变压器

电机驱动中的功率晶体管隔离

高速逻辑系统的隔离

6N137、HCPL-26xx、HCPL-06xx、HCPL-4661、HCNW137和HCNW26x1适用于高速逻辑接口、输入/输出缓冲,作为传统线路接收器无法忍受的环境中的线路接收器,建议在极高的地面或感应噪声环境中使用。

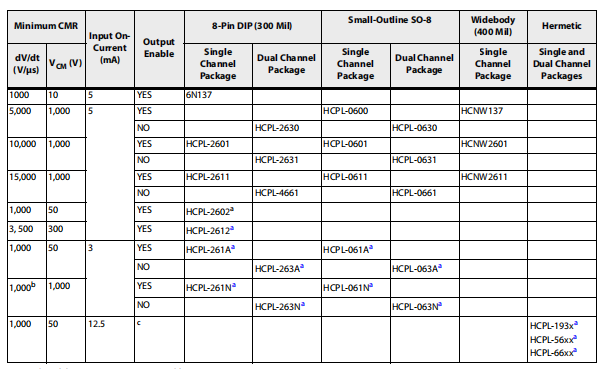

a.技术数据可在单独的Avago出版物上获得。

b.使用Avago应用电路,可实现15千伏/微秒,VCM=1千伏。

c. Enable仅适用于单通道产品,HCPL-193x设备除外。

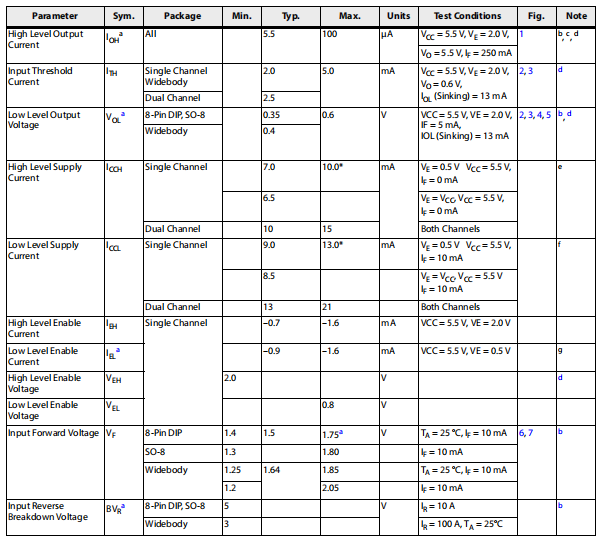

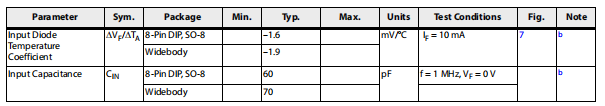

电气规范

除非另有规定,否则超过推荐温度(TA=-40°C至+85°C)。VCC=5 V,TA=25°C时的所有典型值。所有启用测试条件仅适用于单通道产品。见注释。

注:电源线需要旁路,每个光耦附近有一个0.1μF陶瓷圆盘电容器如图所示。电容器两端和隔离针之间的总引线长度不应超过20毫米。

a、 JEDEC注册了6N137的数据。JEDEC注册指定0°C至+70°C。Avago指定-40°C至+85°C。

b、 每个频道。

c.6J137的JEDEC登记规定了250μA. Avago的最大IOH,保证100μA的最大IOH。

d、 启用输入上的高逻辑状态不需要外部上拉。如果不使用VE管脚,将VE连接到VCC将提高CMR性能。为了仅限单渠道产品。

E.JEDEC注册的6N137指定最大ICCH为15毫安。AVAGO保证最大ICCH为10毫安。

f. JEDEC注册的6N137指定最大ICCL为18毫安。AVAGO保证最大的ICCL为13毫安。为6N137的JEDEC注册指定最大IEL为2毫安。阿瓦戈保证最大的IEL为1.6毫安。

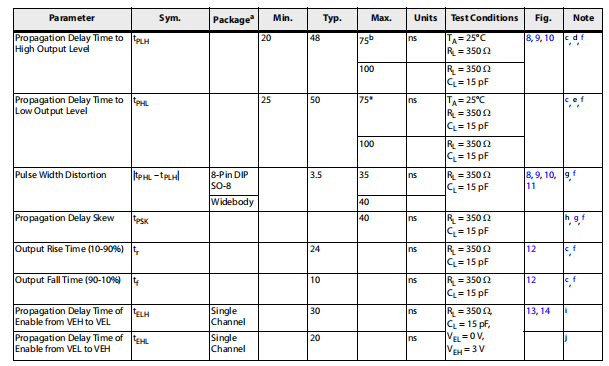

开关规范(AC)

超过推荐温度(TA=-40°C至+85°C),VCC=5V,如果=7.5mA,除非另有规定。TA=25°C,VCC=5 V时的所有典型值。

a.额定值适用于所有设备,除非包装栏中另有说明。

b、 JEDEC注册了6N137的数据。

c、 每个频道。

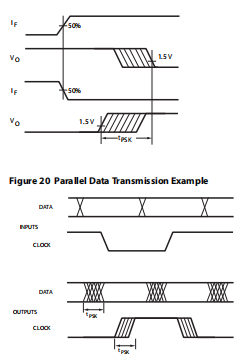

d、 从输入脉冲下降沿上的3.75毫安点到输出脉冲上升沿上的1.5伏点测量tPLH传播延迟。

e、 从输入脉冲上升沿上的3.75毫安点到输出脉冲下降沿上的1.5伏点测量tPHL传输延迟。

f、 启用输入上的高逻辑状态不需要外部上拉。如果不使用VE管脚,将VE连接到VCC将提高CMR性能。为了仅限单渠道产品。

g、 有关详细信息,请参阅标题为“传播延迟、脉冲宽度失真和传播延迟扭曲”的应用部分。

h、 tPSK等于在任何给定温度和规定试验条件下,机组之间出现的tPHL和/或tPLH的最差情况差。

i、 tELH使能传输延迟是从使能输入脉冲下降沿上的1.5 V点到输出脉冲。

j、 tEHL使能传输延迟从使能输入脉冲上升沿上的1.5v点测量到输出脉冲。

传输延迟,脉冲宽度失真和传播延迟偏差传播延迟是描述如何逻辑信号迅速地通过系统传播。这个从低到高的传播延迟(tPLH)是时间量需要输入信号传播到输出端,使输出从低变为高。同样地传播延迟从高到低(tPHL)是时间量输入信号传播到输出所需的使输出从高变为低(见图)。tPLH和tPHL不同时的脉冲宽度失真(PWD)结果价值。PWD定义为tPLH和TPHL经常确定最大数据速率能力传输系统。PWD可以用百分比表示将PWD(单位:ns)除以最小脉冲宽度(单位:ns)正在传送。通常,PWD约为最小脉冲宽度是可以接受的;准确的数字取决于特定应用(RS232、RS422、T-l等)。

传播延迟偏差(tPSK)是考虑在并行数据应用程序中并行数据线上的信号是一个问题。如果并行数据是通过一组光耦发送的传播延迟将导致数据到达输出不同时间的光耦。如果这个差异传播延迟足够大,它将决定并行数据可以通过其发送的最大速率光耦合器。传播延迟偏差定义为最小和最大传播延迟,TPLH或tPHL,对于任何一组正在运行的光耦在相同条件下(即相同的驱动电流、电源电压、输出负载和工作温度)。作为如图所示,如果一组光耦的输入同时打开或关闭,tPSK是最短传播延迟(tPLH)之间的差异或tPHL,以及最长的传播延迟,无论是tPLH还是tPHL。正如前面提到的,TPSK可以确定最大并行。数据传输速率。图是具有时钟和通过光耦合器发送的数据线。图中显示输入和输出的数据和时钟信号光耦合器。为了获得最大的数据传输速率,时钟信号的两个边缘被用于对数据进行时钟;如果只使用一个边缘,时钟信号将需要两倍的速度。

传播延迟偏差表示边缘可能是通过光耦发送的。图显示了两个数据中的不确定性还有时钟线。重要的是这两个方面不确定度不重叠,否则时钟信号可能到达在所有的数据输出都结束之前,或者在某些数据输出可能在时钟信号到达之前开始改变。从这些考虑,绝对最小脉冲宽度在并行应用中可以通过光耦合器发送的是tPSK的两倍。谨慎的设计应该使用稍长的脉冲宽度,以确保电路的其余部分不会导致故障。tPSK指定的光耦合器提供以下优点传输延迟保证规范,脉冲宽度失真和传播延迟超过推荐值温度、输入电流和电源范围。