128点击型号即可查看芯片规格书

ADV7310点击型号即可查看芯片规格书

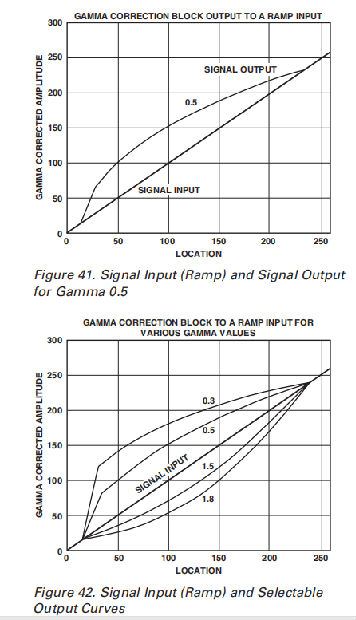

伽马校正

[高清为24小时-37小时,SD为66小时-79小时]Gamma校正可用于SD和HD视频。对于每个标准,有20个8位宽寄存器。它们用于编程伽马校正曲线A和B。HD伽马曲线A在地址24h到2Dh编程,HD伽马曲线B在地址2h到7h编程。SD伽马曲线A在地址66h到6Fh编程,SD伽马曲线B在地址70h到79h编程。

通常伽马校正是用来补偿信号输入和亮度水平输出之间的非线性关系(如在阴极射线管上看到的)。它也可以应用于非线性处理的任何地方。

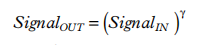

伽马校正使用函数:

其中=伽马功率因数。

伽马校正仅对luma数据执行。用户可以选择两条不同的曲线中的任意一条,曲线A或曲线B。任何时候,只能使用其中一条曲线。

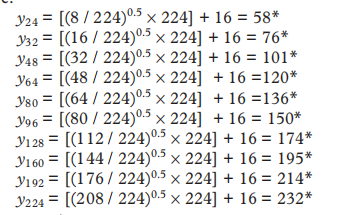

曲线的响应在10个预定义位置编程。在更改这些位置的值时,可以修改gamma曲线。在这些点之间,使用线性插值生成中间值。考虑到曲线的总长度为256点,这10个位置分别位于24、32、48、64、80、96、128、160、192和224处。位置0、16、240和255是固定的,不能更改。

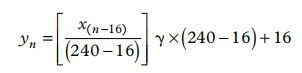

对于16到240的长度,伽马校正曲线的计算如下:

其中:y=伽马校正输出;x=线性输入信号=伽马功率因数;要对伽马校正寄存器进行编程,需要y必须使用以下公式计算:

其中:x(n-16)=x沿x轴的点的值;n=24、32、48、64、80、96、128、160、192或224;yn=y沿y轴的值,该值必须写入。

伽马校正寄存器

例如:

*四舍五入到最接近的整数

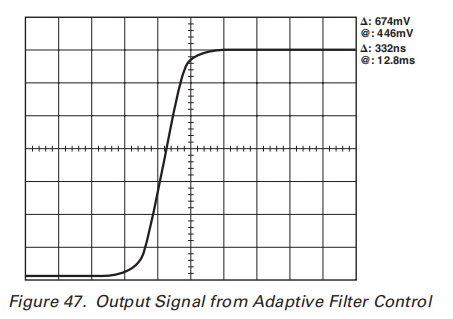

图46和47中的伽马曲线仅为示例;用户定义的任何曲线在16到240之间都是可以接受的。

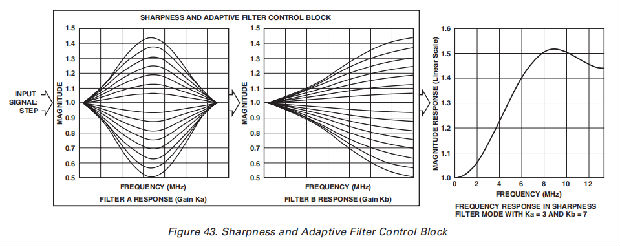

高清清晰度滤波控制与自适应滤波控制[子地址20h,38h–3Dh]

ADV7310/ADV7311上有三种过滤模式:锐度过滤模式和两种自适应过滤模式。

高清清晰度过滤模式

要在下图所示的频率范围内增强或衰减Y信号,必须使用以下寄存器设置:必须启用HD sharpness filter,并且必须将HD adaptive filter enable设置为disabled。

要选择256个单独响应中的一个,每个滤波器的相应增益值(范围从-8到+7)必须编程到地址20h的HD清晰度滤波器增益寄存器中。

高清自适应滤波模式

HD自适应滤波器阈值A、B、C寄存器、HD自适应滤波器增益1、2、3寄存器和HD锐度增益寄存器用于自适应滤波器模式。要激活自适应滤波器控制,必须启用HD清晰度滤波器,并且必须启用HD自适应滤波器。

将输入信号的导数与三个可编程阈值进行比较:HD自适应滤波器阈值A、B、C。尽管可以使用0到255范围内的任何值,但建议的阈值范围为16到235。

然后,可以使用HD自适应滤波器增益1、2、3寄存器和HD锐度滤波器增益寄存器中的设置来衰减边缘。

根据HD自适应滤波器模式控制的设置,有两种自适应滤波器模式可用:

1、当自适应滤波器模式设置为0时,使用模式A。在这种情况下,滤波器B(LPF)将用于自适应滤波器块。此外,在需要时,仅应用HD锐度滤波器增益、HD自适应滤波器增益1、2、3中的增益B的编程值。增益A值是固定的,不能改变。

2、当自适应滤波器模式设置为1时,使用模式B。在此模式下,使用滤波器a和滤波器B的级联。当需要时,HD锐度滤波器增益、HD自适应滤波器增益1、2、3中的增益A和增益B的设置都变为激活状态。

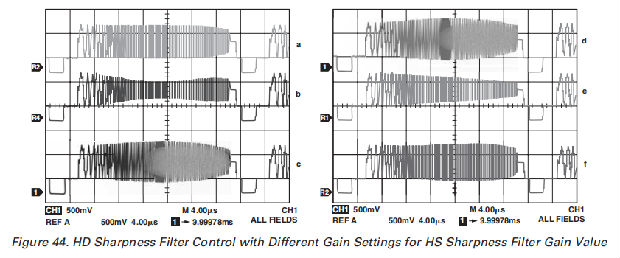

HD锐度滤波器及自适应滤波器的应用使用时还可以看到锐度过滤器的效果

实例内部生成的交叉填充图案。

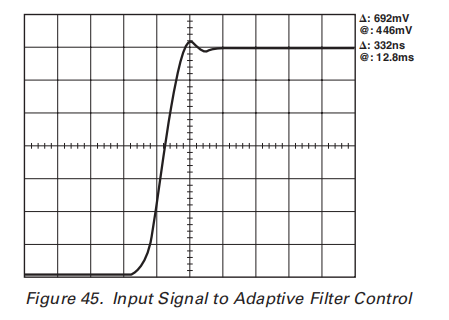

自适应滤波控制应用

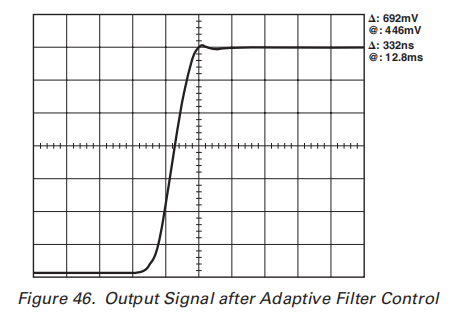

图45和46示出了要由自适应滤波器控制块处理的典型信号。

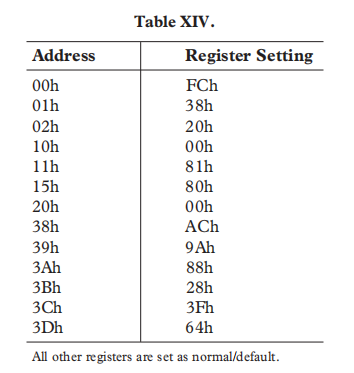

以下寄存器设置用于获得图46所示的结果,即,消除Y信号上的振铃。

输入数据由外部信号源生成。

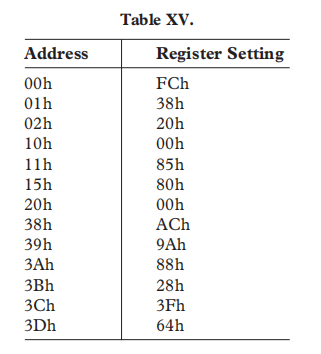

自适应滤波器控制也可以使用内部生成的交叉阴影测试模式和切换自适应滤波器控制位[地址15h,位7]来演示。

SD数字降噪[子地址63h、64h、65h]

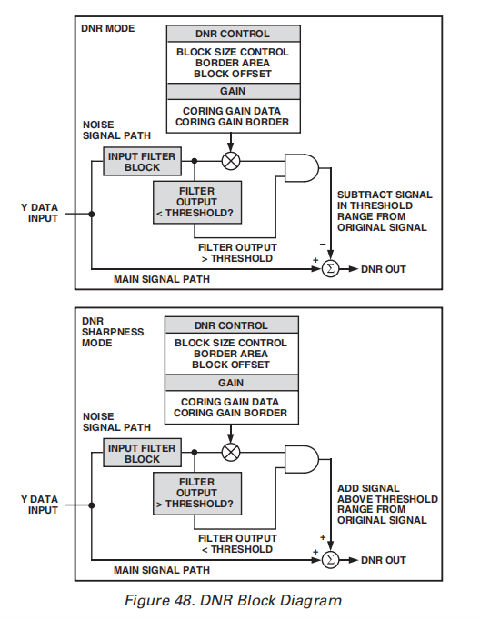

DNR仅应用于Y数据。滤波器块选择输入信号的高频、低振幅分量[DNR input select]。将滤波器输出的绝对值与可编程阈值[DNR阈值控制]进行比较。有两种DNR模式可用:DNR模式和DNR锐度模式。

在DNR模式下,如果滤波器输出的绝对值小于阈值,则假定为噪声。将从原始信号中减去该噪声信号的可编程量[取芯增益边界,取芯增益数据]。在DNR锐度模式下,如果滤波器输出的绝对值小于编程阈值,则假定为噪声,与之前一样。否则,如果电平超过阈值(现在被识别为有效信号),则信号的一部分[取芯增益边界,取芯增益数据]将被添加到原始信号中,以增强高频分量并锐化视频图像。

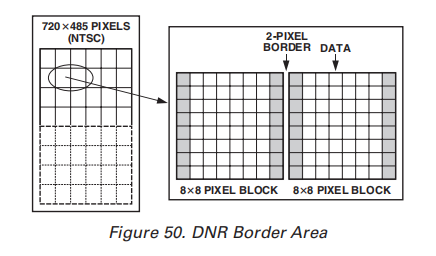

在MPEG系统中,通常以8像素×8像素的块处理MPEG2系统的视频信息,或以16像素×16像素的块处理MPEG1系统的视频信息[块大小控制]。DNR可以应用于已知包含噪声的块过渡区域。通常,块过渡区域包含两个像素。可以将此区域定义为包含四个像素[边界区域]。

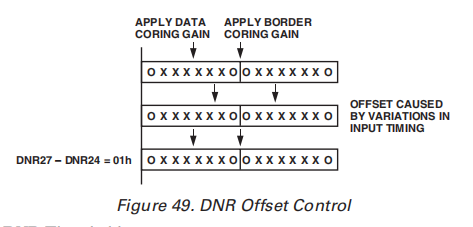

还可以使用[DNR块偏移量]补偿可变块定位或YCrCb像素定时中的差异。

数字降噪寄存器是三个8位寄存器。它们用于控制DNR处理。

取心增益边界[地址63h,位3–0]

这四位被分配给应用于边界区域的增益因子。

在DNR模式下,增益值的范围为0到1,增量为1/8。此因子应用于DNR筛选器输出,该输出低于设置的阈值范围。然后从原始信号中减去结果。

在DNR锐度模式下,增益值的范围为0到0.5,增量为1/16。此因子应用于DNR滤波器输出,该输出高于阈值范围。

结果将添加到原始信号中。

取心增益数据[地址63h,位7–4]

这四位被分配给应用于MPEG像素块内的luma数据的增益因子。

在DNR模式下,增益值的范围为0到1,增量为1/8。此因子应用于DNR筛选器输出,该输出低于设置的阈值范围。然后从原始信号中减去结果。

在DNR锐度模式下,增益值的范围为0到0.5,增量为1/16。此因子应用于DNR滤波器输出,该输出高于阈值范围。

结果将添加到原始信号中。

DNR阈值[地址64h,位5–0]

这6位用于定义0到63范围内的阈值。范围是绝对值。

边境地区[地址64h,位6]

当该位被设置为逻辑1时,块转换区域可以被定义为由四个像素组成。如果该位被设置为逻辑0,则边界转换区域由两个像素组成,其中一个像素表示27mhz下的两个时钟周期。

块大小控件[地址64h,位7]

此位用于选择要处理的数据块的大小。将块大小控制功能设置为逻辑1定义16像素×16像素数据块,逻辑0定义8像素×8像素数据块,其中一个像素表示27mhz下的两个时钟周期。

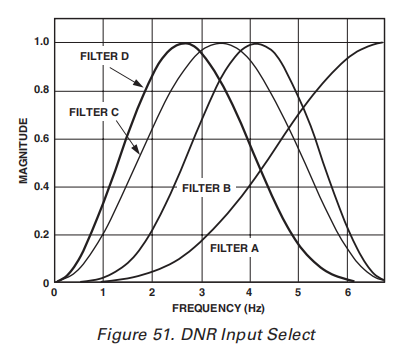

DNR输入选择控制[地址65h,位2–0]

分配三个位来选择过滤器,该过滤器应用于输入的Y数据。位于所选滤波器通频带中的信号是将被DNR处理的信号。图51显示了使用此控件可选择的过滤器响应。

DNR模式控制[地址65h,位4]

该位控制所选的DNR模式。逻辑0选择DNR模式;逻辑1选择DNR锐度模式。

DNR的工作原理是将低振幅、高频信号定义为可能噪声,并从原始信号中减去该噪声。

在DNR模式下,可以从原始信号中减去低于设定阈值(假设为噪声)的信号的一部分。阈值在DNR寄存器1中设置。

当启用DNR锐度模式时,可以将高于设置阈值的信号的一部分添加到原始信号,因为该数据被假定为有效数据而不是噪声。整体效果是信号将被增强(类似于使用扩展的SSAF滤波器)。

块偏移控制[地址65h,位7–4]

四位被分配给该控制,这允许最大15个像素的数据块的移位。考虑取心增益位置固定。块偏移以一个像素的步进移动数据,使得可以在相同位置应用边界取心增益因子,而不管数据的输入定时的变化。

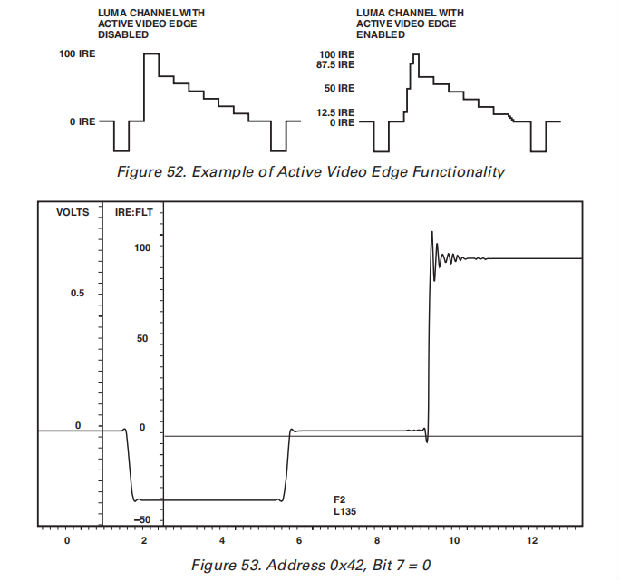

SD活动视频边缘[子地址42h,位7]

当激活视频边缘时,在LUMA信道上的活动视频的前三个像素和最后三个像素以这样的方式缩放,这些像素上的最大过渡是不可能的。标度因子为×1/8、×1/2和×7/8。

所有其他活动视频都未经处理。

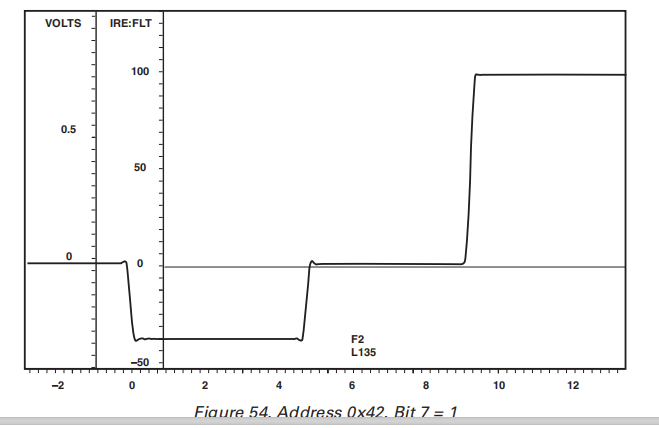

SAV/EAV步进边缘控制

ADV7310/ADV7311能够控制活动视频开始和结束时的快速上升和下降信号,以最小化振铃。

一种算法监视SAV和EAV,并在边缘速度过快时进行控制。其结果将是减少活动视频开始和结束时的铃声,以实现快速过渡。子地址0x42,位7=1启用此功能。

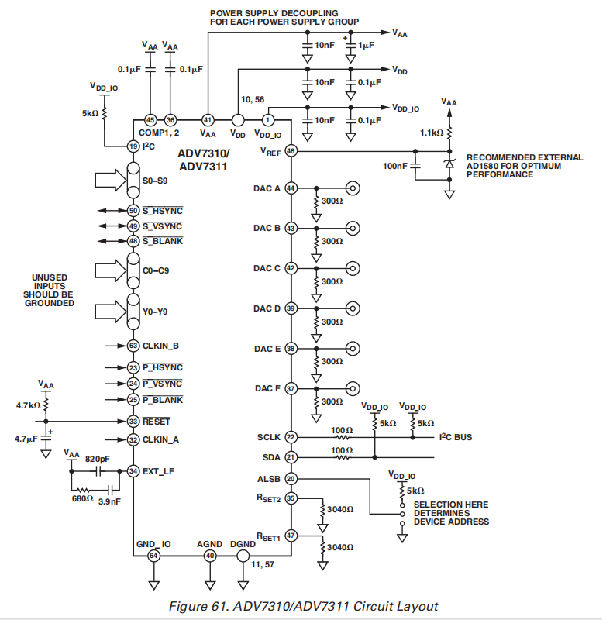

电路板设计和布局注意事项

DAC终端和布局注意事项

ADV7310/ADV7311包含车载参考电压。ADV7310/ADV7311可与外部VREF(AD1580)一起使用。

RSET电阻器连接在RSET引脚和AGND之间,用于控制满标度输出电流,从而控制DAC电压输出电平。对于满标度输出,RSET的值必须为3040Ω。不应更改RSET值。RLOAD的满标度输出值为300Ω。

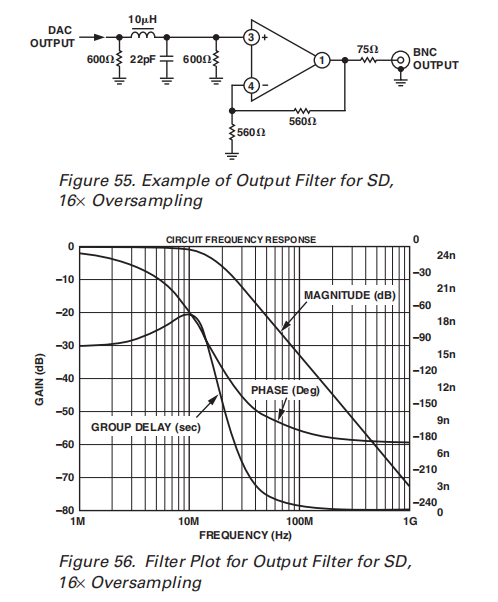

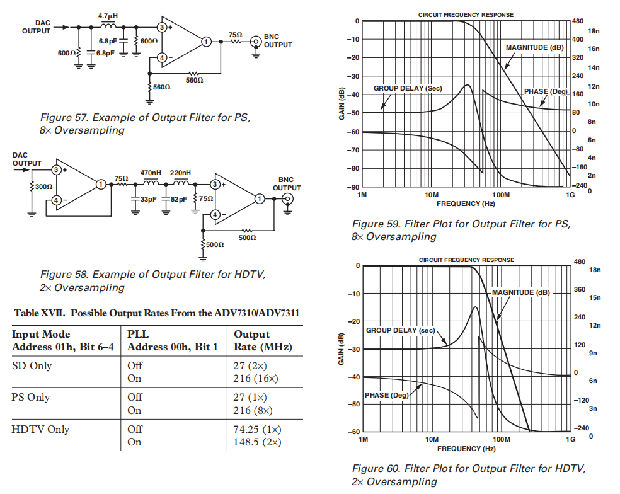

视频输出缓冲器和可选输出滤波器为了驱动输出设备,如SD或HD监视器,所有六个dac上的输出缓冲是必要的。模拟设备产生一系列适用于此应用的运算放大器,例如AD8061。有关线路驱动器缓冲电路的更多信息,请参见相关运算放大器的数据表。

如果ADV7310/ADV7311连接到需要该滤波的设备,则可能需要可选的模拟重建低通滤波器(LPF)作为反成像滤波器。

过滤器规格随应用而变化。

PCB板布局注意事项

ADV7310/ADV7311经过优化设计,在辐射和传导噪声方面均具有最低的噪声性能。为了补充ADV7310/ADV7311出色的噪声性能,必须非常注意PC板的布局。

应优化布局,使ADV7310/ADV7311电源线和地线的噪声最低。这可以通过屏蔽数字输入和提供良好的解耦来实现。VAA和AGND、VDD和DGND、VDD-IO和GND-IO引脚组之间的引线长度应尽可能短,以尽量减少感应振铃。

建议使用4层印刷电路板,电源和接地平面将信号传输层与元件和焊料侧层分开。为了分离噪声电路,如晶体时钟、高速逻辑电路和模拟电路,应仔细考虑元件的放置。应有一个单独的模拟接地平面和一个单独的数字接地平面。

电源平面应包括数字电源平面和模拟电源平面。模拟电源平面应包含DAC和所有相关电路、VREF电路。数字电源平面应包含所有逻辑电路。

模拟和数字电源平面应通过适当的滤波装置(如铁氧体磁珠)在单个点单独连接到公共电源平面。

PCB上的DAC输出轨迹应视为传输线。建议将DAC放置在尽可能靠近输出连接器的位置,模拟输出记录道尽可能短(小于3英寸)。DAC终端电阻应尽可能靠近DAC输出,并应覆盖PCB的接地平面。除了尽量减少反射,短模拟输出轨迹将减少由于相邻数字电路引起的噪声拾取。

为了避免DAC输出之间的串扰,建议在各个DAC输出管脚的磁道之间留出尽可能多的空间。还建议在输出之间增加地面轨迹。

电源去耦

使用去耦电容器可以进一步降低模拟电源平面上的噪声。

通过使用10nF和0.1 陶瓷电容器。每组VAA、VDD或VDD-IO引脚应单独与接地分离。这应通过将电容器放置在尽可能靠近装置的位置,使电容器引线尽可能短,从而使引线电感最小化来实现。除了10nF陶瓷外,建议在VAA电源中使用1μF钽电容器。

参见图61中的电路布局。

数字信号互连

数字信号线应尽可能与模拟输出和其他模拟电路隔离。数字信号线不应覆盖模拟电源平面。

由于使用的时钟频率很高,应避免到ADV7310/ADV7311的长时钟线,以将噪声拾取降至最低。

任何用于数字输入的有源上拉终端电阻器应连接到数字电源平面,而不是模拟电源平面。

模拟信号互连

ADV7310/ADV7311应尽可能靠近输出连接器,从而最大限度地减少由于阻抗失配而引起的噪声拾取和反射。

为了获得最佳性能,模拟输出应分别为源端和负载端,如图61所示。终端电阻应尽可能靠近ADV7310/ADV7311,以尽量减少反射。

为了获得最佳性能,建议与ADV7310/ADV7311相关的所有去耦和外部组件都位于PCB的同一侧,并尽可能靠近ADV7310/ADV7311。任何未使用的输入都应接地。

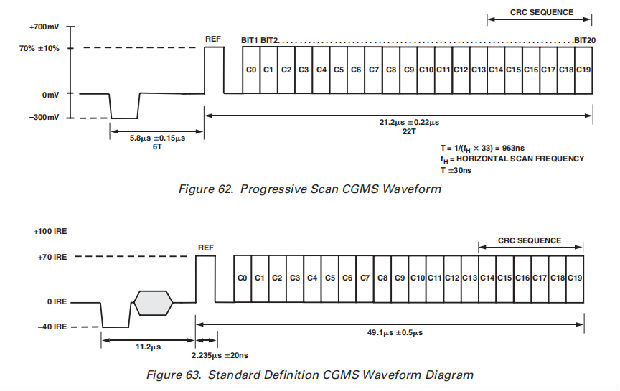

附录1-复制生成管理系统PS CGMS数据寄存器2–0[子地址21h、22h、23h]

PS CGMS可在525p模式下使用,符合CGMS-A EIA-J CPR1204-1,使用垂直消隐间隔(525p系统)传输视频ID信息的方法,1998年3月,和IEC61880,1998,视频系统(525/60)-使用垂直消隐间隔模拟接口的视频和伴随数据。

当PS CGMS被启用时[子地址12h,位6=1],CGMS数据被插入到第41行。PS CGMS数据寄存器位于地址21h、22h和23h。

SD CGMS数据寄存器2–0[子地址59h,5Ah,5Bh]

ADV7310/ADV7311支持符合标准的副本生成管理系统(CGMS)。CGMS数据在奇数域的第20行和偶数域的第283行上传输。位C/W05和C/W06控制CGMS数据是否在奇偶字段上输出。只有当ADV7310/ADV7311配置为NTSC模式时,才能传输CGMS数据。CGMS数据长20位,每个位的功能如下表所示。CGMS数据前面有一个与CGMS位振幅和持续时间相同的参考脉冲;见图63。

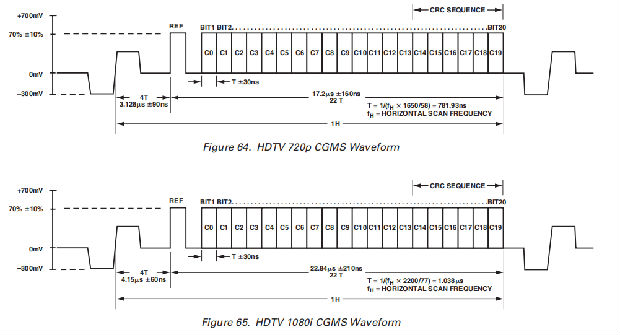

HD/PS CGMS[地址12h,位6]

根据EIAJ CPR-1204-2,ADV7310/ADV7311支持HDTV模式(720p和1080i)下的副本生成管理系统(CGMS)。

HD CGMS数据寄存器位于地址021h、22h、23h。

CGMS位的功能

字0–6位;字1–4位;字2–6位;CRC 6位CRC多项式=x6+x+1(预设为111111)。

720p系统

将CGMS数据应用于亮度垂直消隐间隔的第24行。

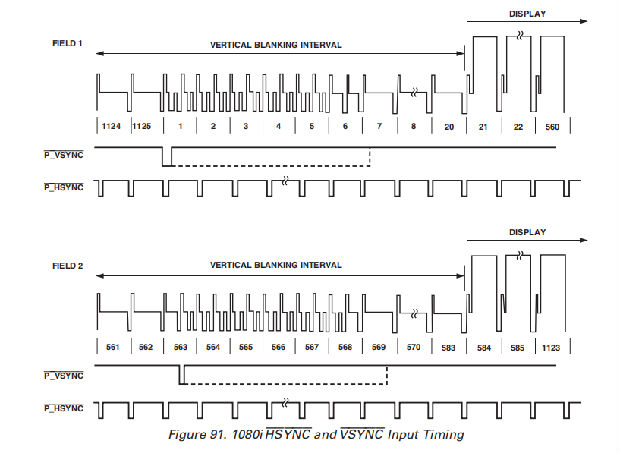

1080i系统

CGMS数据应用于亮度垂直消隐间隔的第19行和第582行。

CGMS功能

如果SD CGMS CRC[地址59h,位4]或PS/HD CGMS CRC[子地址12h,位7]设置为逻辑1,最后6位C19–C14(构成6位CRC校验序列)基于数据寄存器中数据的较低14位(C0–C13)在ADV7310/ADV7311上自动计算,并与剩余14位一起输出,以形成CGMS数据的完整20位。CRC序列的计算基于预设值为111111的多项式x6+x+1。如果SD CGMS CRC[地址59h,位4]和PS/HD CGMS、CRC[地址12h,位7]设置为逻辑0,所有20位(C0–C19)直接从CGMS寄存器输出(不计算CRC,必须由用户计算)。

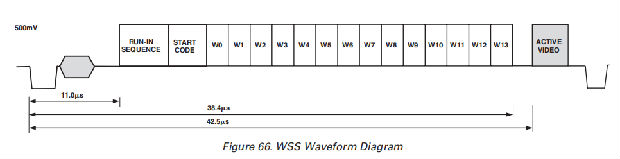

附录2-SD宽屏信号[子地址59h,5Ah,5Bh]

ADV7310/ADV7311支持符合标准的宽屏信令(WSS)。WSS数据在23号线传输。只有当设备配置为PAL模式时,才能传输WSS数据。WSS数据长14位,每个位的功能如表XIX所示。WSS数据前面是一个运行序列和一个开始代码;参见图66。如果将SD WSS[地址59h,位7]设置为逻辑1,则启用要在23号线传输的WSS数据。线23的后一部分(距HSYNC的下降边缘42.5μs)可用于插入视频。

第23行的WSS部分可以用子地址61h的第7位留空。

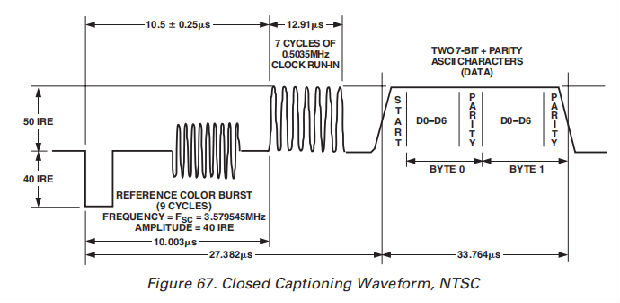

附录3-SD闭路字幕[子地址51h–54h]

ADV7310/ADV7311支持符合用于彩色传输的标准电视同步波形的闭路字幕。在偶数场的奇数场和线284的线21的消隐有效线时间期间,传输封闭字幕。

闭路字幕由一个7周期的正弦脉冲组成,频率和相位锁定到字幕数据。在时钟运行信号之后,保持两个数据位的消隐电平,接着是逻辑1起始位。16位数据跟随起始位。它们由两个8位字节、七个数据位和一个奇偶校验位组成。这些字节的数据存储在SD闭路字幕寄存器[地址53h–54h]中。

ADV7310/ADV7311还支持扩展的闭路字幕操作,该操作在偶数字段期间激活,并在扫描行284上编码。此操作的数据存储在SD闭路字幕寄存器[地址51h–52h]中。

ADV7310/ADV7311自动生成所有支持第21和284行闭路字幕显示的时钟运行信号和定时。如果启用了闭路字幕,则在第21行和第284行期间忽略所有像素输入。

FCC联邦法规(CFR)47第15.119节和EIA608描述了第21和284行的闭路字幕信息。

ADV7310/ADV7311使用单一缓冲方法。这意味着闭路字幕缓冲区只有1字节深;因此与其他2字节深缓冲系统不同,在输出闭路字幕数据时不会有帧延迟。数据必须在(第20行或第283行)输出到第21行和第284行之前加载一行。这种方法的一个典型实现是使用VSYNC来中断微处理器,微处理器将依次加载每个字段中的新数据(两个字节)。如果传输不需要新数据,则必须在两个数据寄存器中插入0;这称为空。加载控制代码也很重要,所有这些代码都是第21行的双字节,否则电视将无法识别它们。如果有“Hello World”这样的消息包含奇数个字符,则必须将其填充为偶数,以便使“结束字幕”的2字节控制代码落在同一字段中。

附录4-测试模式

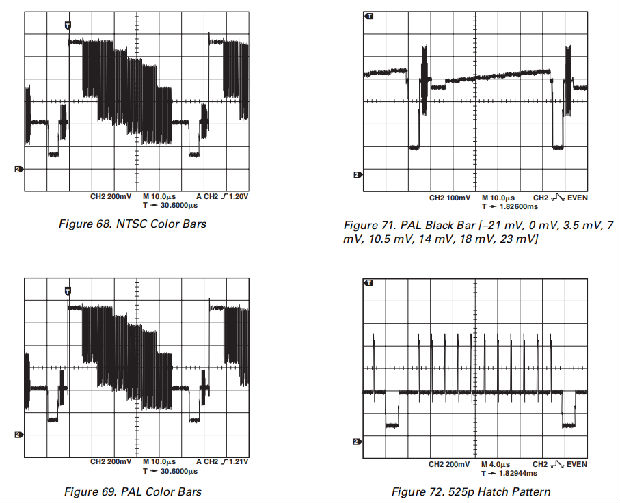

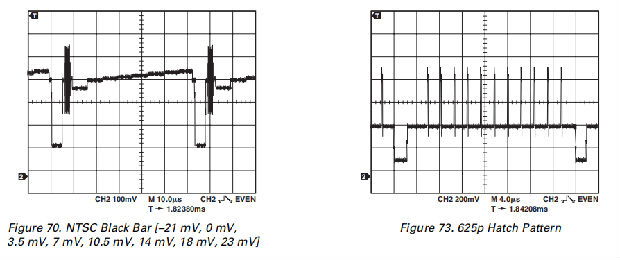

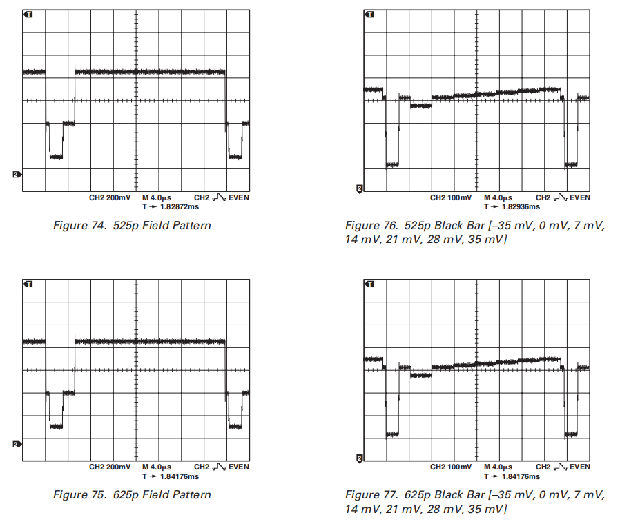

ADV7310/ADV7311可以生成SD和HD测试模式。

附录5-SD计时模式

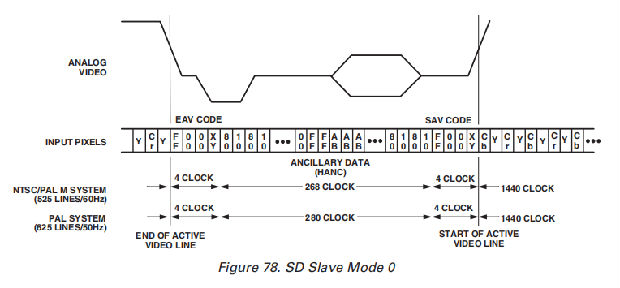

[子地址4Ah]模式0(CCIR-656)-从选项(定时寄存器0 TR0=X X X X 0 0 0)ADV7310/ADV7311由像素数据中的SAV(开始活动视频)和EAV(结束活动视频)时间代码控制。使用4字节同步模式发送所有定时信息。在活动画面和回溯期间,在每行前后立即发送同步模式。在此模式下,应将S掼VSYNC、S掼HSYNC和S掼BLANK(如果未使用)管脚系紧。空白输出可用。

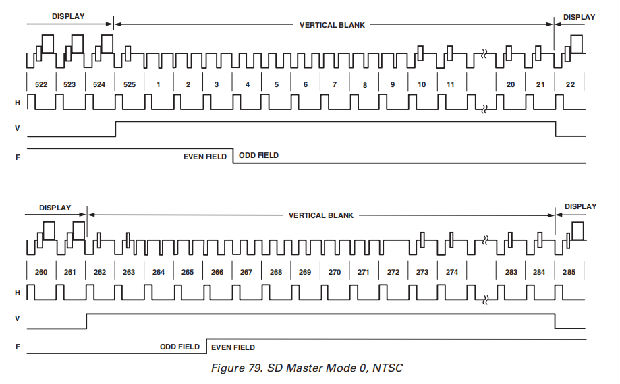

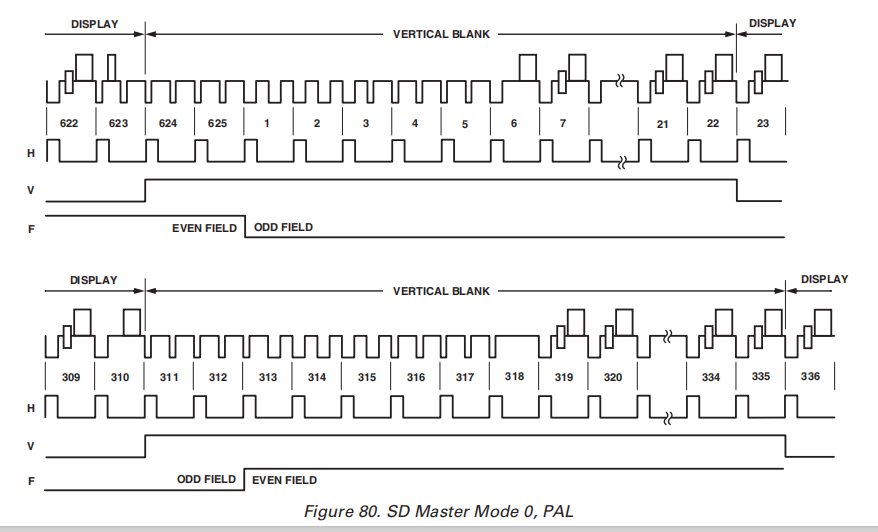

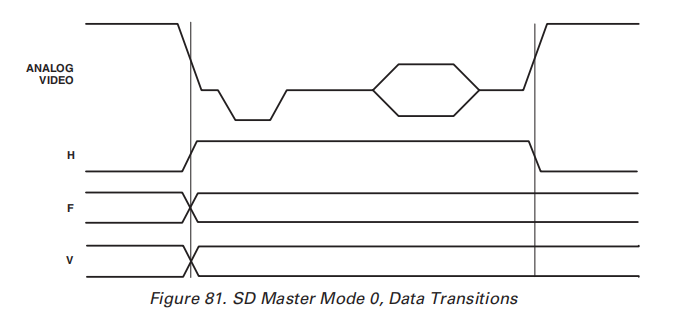

模式0(CCIR-656)-主选项(定时寄存器0 TR0=X X X X 0 1)

ADV7310/ADV7311生成CCIR656标准中SAV(开始活动视频)和EAV(结束活动视频)时间代码所需的H、V和F信号。H位在S_HSYNC上输出,V位在S_BLANK上输出,F位在S_VSYNC上输出。

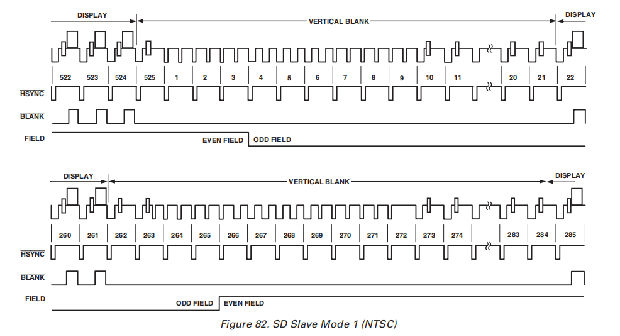

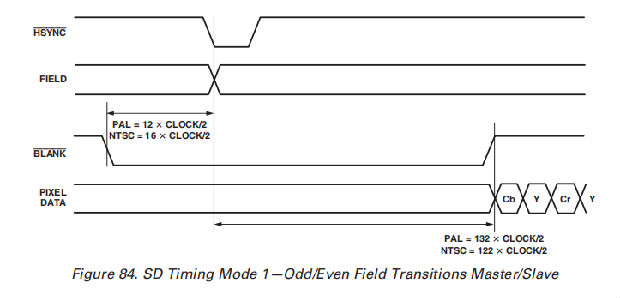

模式1-从机选项(定时寄存器0 TR0=X X X X X 0)

在此模式下,ADV7310/ADV7311接受水平同步和奇偶场信号。当HSYNC低时,字段输入的转换表示新帧,即垂直回溯。空白信号是可选的。当空白输入被禁用时,ADV7310/ADV7311根据CCIR-624自动空白所有正常空白行。HSYNC在S_HSYNC上输入,在S_BLANK上输入空白,在S_VSYNC上输入字段。

模式1-主选项(定时寄存器0 TR0=X X X X 0 1 1)

在这种模式下,ADV7310/ADV7311可以产生水平同步和奇偶场信号。当HSYNC低时,字段输入的转换表示新帧,即垂直回溯。空白信号是可选的。当空白输入被禁用时,ADV7310/ADV7311根据CCIR-624自动空白所有正常空白行。像素数据锁定在上升时钟上

定时信号转换后的边缘。HSYNC在S_HSYNC上输出,在S_BLANK上输出空白,在S_VSYNC上输出字段。

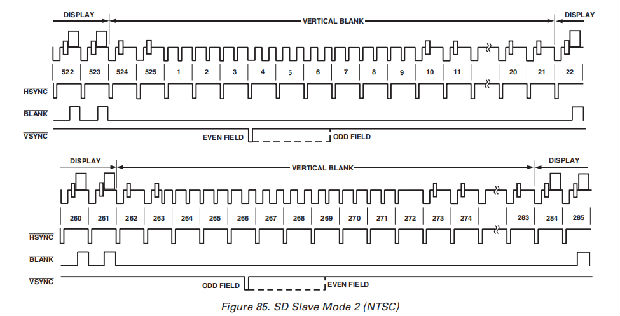

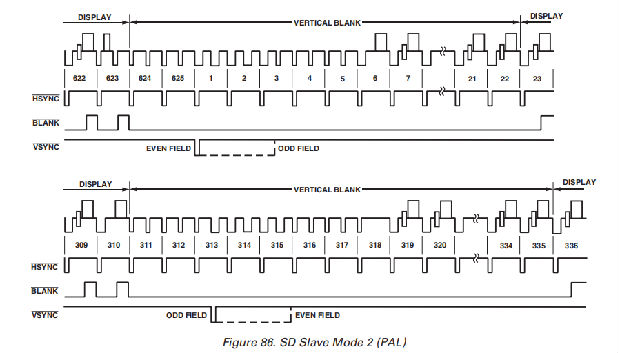

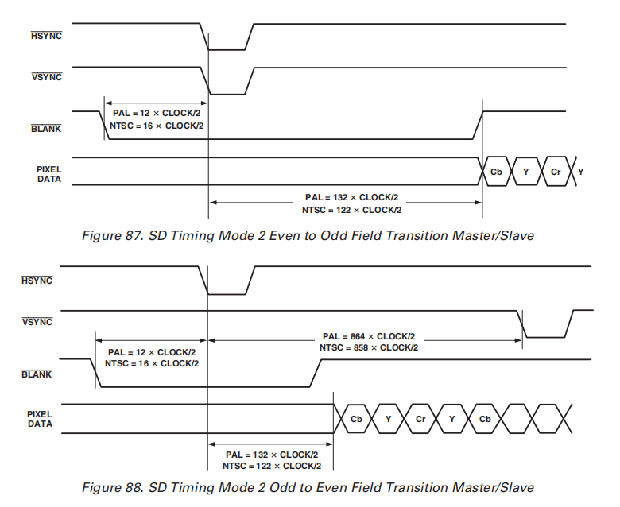

模式2-从机选项(定时寄存器0 TR0=X X X X 1 0 0)

在此模式下,ADV7310/ADV7311接受水平和垂直同步信号。HSYNC和VSYNC输入同时低转换表示奇数场的开始。当HSYNC为high时,VSYNC low转换表示偶数字段的开始。空白信号是可选的。当空白输入被禁用时,ADV7310/ADV7311根据CCIR-624自动空白所有正常空白行。HSYNC是输入S_HSYNC,S_BLANK上为BLANK,S_VSYNC上为VSYNC。

模式2-主选项(定时寄存器0 TR0=X X X X 1 0 1)

在此模式下,ADV7310/ADV7311可以生成水平和垂直同步信号。HSYNC和VSYNC输入同时低转换表示奇数场的开始。当HSYNC为high时,VSYNC low转换表示偶数字段的开始。空白信号是可选的。当空白输入被禁用时,ADV7310/ADV7311根据CCIR-624自动空白所有正常空白行。HSYNC在S_HSYNC上输出,在S_BLANK上输出BLANK,在S_VSYNC上输出VSYNC。

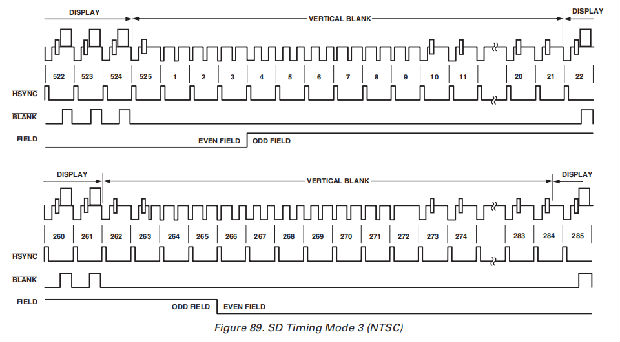

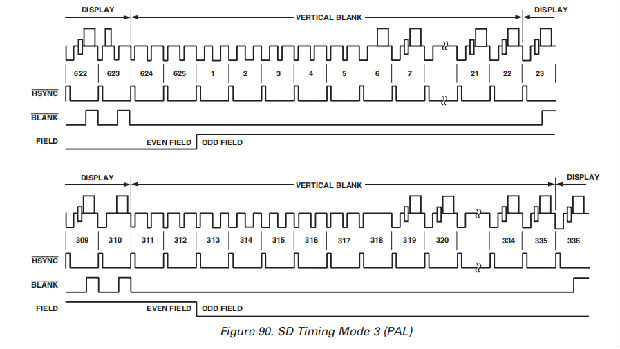

模式3-主/从选项

(定时寄存器0 TR0=X X X X X 11 0或X X X X 1 1 1 1)在此模式下,ADV7310/ADV7311接受或生成水平同步和奇偶场信号。当HSYNC高时,字段输入的转换表示一个新帧,即垂直回溯。空白信号是可选的。当空白输入被禁用时,ADV7310/ADV7311根据CCIR-624自动空白所有正常空白行。HSYNC在主模式下输出,在S_VSYNC上输入,在S_BLANK上输入,在S_VSYNC上输入。

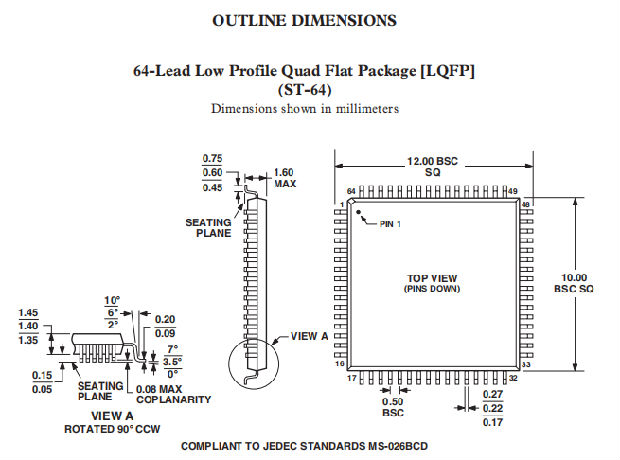

外形尺寸