特征

行业最小的22位序列化器/反序列化器对低功耗,对电池寿命的影响最小–多种断电模式待机模式下为100nA,典型运行5mA条件高度轧制的LVCMOS边缘速率选项法规要求电缆缩减率:25:4或更大差分信号:–在实验室条件下使用CTL时为90dBm EMI–最小化屏蔽–最小化EMI滤波器–对外部干扰的最小敏感性任意方向最多22位电压从1.65V转换为3.6V高ESD保护:>15kV HBM并行I/O电源(VDDP)范围,1.65V-3.6V可支持微控制器或RGB像素接口

应用

图像传感器

小型显示器–液晶显示器、手机、数码相机、便携式游戏机,打印机、PDA、摄像机、汽车

FIN224AC与FIN24AC比较最大功率降低20%FIN224AC模式3上的双宽CKP脉冲反序列化器输出的卷边率FIN224AC,用于单显示器应用相同电压范围相同的引脚和封装

注:

1.DSO/DSI串行端口引脚的排列方式,使得如果一个设备相对于其他设备,串行连接正确对齐,无需任何痕迹或电缆信号交叉。其他布局方向可能需要轨迹或电缆交叉。

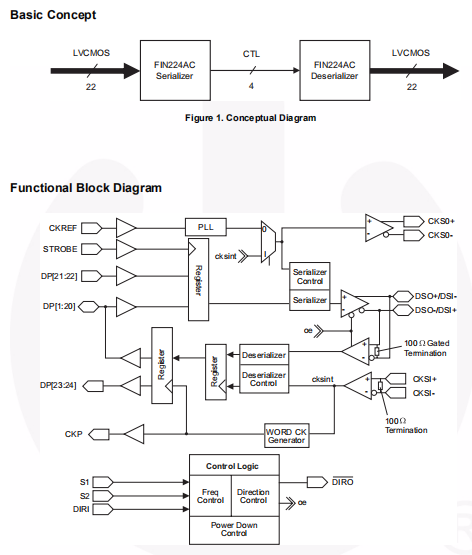

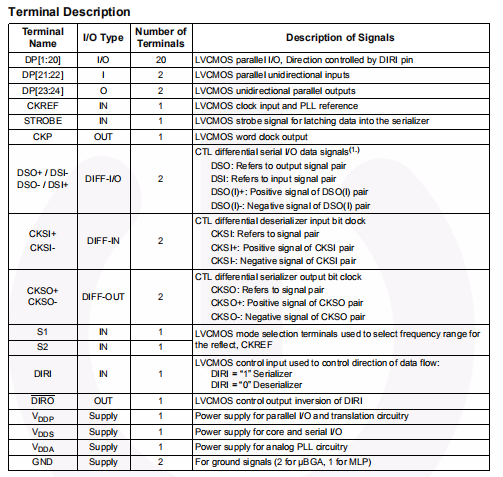

控制逻辑电路

FIN224AC能够用作22位序列化程序或22位反序列化程序。插脚S1和S2必须设置为适应时钟参考输入频率序列化程序的范围。表1显示了基于S1和S2控件的这些选项的pin编程别针。DIRI pin控制设备是序列化程序还是反序列化程序。当DIRI被断言为低时设备配置为反序列化程序。当大头针如果断言为高,则设备配置为序列化程序。改变DIRI信号的状态会使I/O信号的方向并产生相反的DIRO上的状态信号。对于单向操作DIRI引脚应硬接线至高或低状态迪罗大头针应该是浮动的。对于双向操作,驱动主设备的方向系统使用主机的DIRO信号驱动从设备的目录。具有专用I/O变体的序列化程序/反序列化程序序列化和反序列化电路是为24位。由于专用的输入和输出,只有22位数据被序列化或反序列化。DP[21:22]发送到序列化程序的输入到反序列化程序上的DP[23:24]输出。

掉头功能

设备通过并反转DIRI信号设备与DIRO信号异步。关心必须由系统设计器执行,以确保反序列化程序输出与这个端口上的其他设备。优化外围设备驱动序列化器的设备应在断言DIRI信号之前进入高阻抗状态。当具有专用数据输出的设备从反序列化程序到序列化程序,专用输出将保留在断言的最后一个逻辑值处。仅此值如果设备再次变成反序列化程序和值将被覆盖。关机模式:(模式0)模式0用于关闭电源并重置装置。当两个模式信号都被驱动到低状态,PLL和参考被禁用,差分输入缓冲器被关闭,差分输出缓冲器被置于高阻抗状态,LVCMOS输出被置于高阻抗状态,并且LVCMOS输入在内部被驱动到有效水平。此外,所有内部电路都复位。失去CKREF状态也被启用,以确保仅PLL如果存在有效的CKREF信号,则通电。在典型的应用模式中,设备的信号不改变期望频率以外的状态范围和断电模式。这允许实现系统级断电功能通过一根线连接到一对SerDes。S1和S2选择信号,其工作模式被驱动到“逻辑0”应硬接线至GND。S1和S2将其工作模式驱动为“逻辑”的信号1“应连接至系统级电源关闭或复位信号。

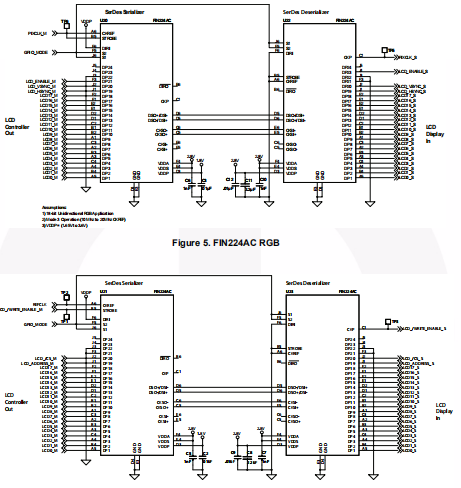

表1.控制逻辑电路

序列化程序操作模式

序列化程序配置将在以下各节中介绍。基本的串行电路工作在这些模式中基本相同,但实际数据时钟流的不同取决于CKREF是否是是否与选通信号相同。当它被陈述CKREF不等于频闪,每个信号都是不同的,CKREF必须以高频率运行足以避免任何数据丢失的情况。CKREF必须永远不要低于频闪。序列化程序操作:模式1或模式2,DIRI=1,CKREF=STROBEPLL必须接收稳定的CKREF信号才能实现在发送任何有效数据之前锁定。CKREF信号可用作提供的数据选通信号在锁相环锁定阶段可以忽略这些数据。一旦锁相环稳定并锁定,设备就可以启动捕获和序列化数据。数据在选通信号的上升沿捕获并序列化。什么时候?在序列化器模式下运行时,内部反序列化器电路被禁用;包括串行时钟、串行数据输入缓冲区、双向并行输出和CKP文字时钟。CKP字时钟被驱动得很高。序列化程序操作:DIRI=1,CKREF不=选通如果CKREF和STROBE没有使用相同的信号,CKREF信号必须以更高的频率运行比正确序列化数据的频闪率高。这个实际串行传输速率保持在CKREF频率。

当串行位流中不存在有效数据。否则序列化程序的操作将保持不变。基准时钟需要的准确频率运行取决于CKREF的稳定性和频闪信号。如果CKREF信号源实现扩频技术应使用扩频时钟的频率在计算选通频率与CKREF频率。同样,如果选通信号显著的周期-周期变化,最大循环周期时间需要考虑到选择。CKREF频率。序列化程序操作:模式3(S1=S2=1),迪里=1。CKREF除以2模式。在模式3下工作时,有效串行速度为除以二。此模式已实现为适用于参考时钟频率与实际选通频率相比较高的情况。实际选通频率必须小于或等于此模式工作的频率为CKREF频率的50%是的。这种模式,在所有其他方面,操作与CKREF中所述相同不等于频闪。序列化程序操作:DIRI=1,无CKREF第三种串行化方法可以通过在CKSI信号上提供自由运行的位时钟来实现。这个模式通过接地CKREF信号和把DIRI信号调高。通电时,设备配置为接受来自CKSI的序列化时钟。如果接收到CKREF时,此设备将启用CKREF序列化模式。即使在CKREF已停止。要重新启用此模式,设备必须关闭电源,然后使用CKREF上的“逻辑0”

反序列化程序操作模式

反序列化程序的操作依赖于在DSI数据信号对和CKSI上接收的数据时钟信号对。以下各节介绍反序列化程序在不同序列化程序下的操作源条件。引用CKREF和频闪信号是指与生成串行数据和时钟信号的串行化器设备,这些数据和时钟信号是反串行化器的输入。操作时在反序列化程序模式下,内部序列化程序电路被禁用,包括并行数据输入缓冲区。如果有的话提供了CKREF信号,CKSO串行时钟继续发送位时钟。通电时(S1或S2=1),反序列化程序输出数据管脚在有效之前一直处于低位数据通过反序列化器传递。反序列化程序操作:DIRI=0(序列化程序当DIRI信号被断言为低时,设备配置为反序列化程序。数据在串行端口并通过使用位时钟反序列化与数据一起发送。反序列化程序操作:DIRI=0(序列化程序反序列化程序的逻辑操作仍然是如果CKREF的频率与选通相同或者频率高于选通。实际的呈现给反序列化程序的串行数据流不同,因为它在话。CKP的占空比根据比率而变化至选通电路的CKREF信号频率信号。CKP信号的频率等于频闪频率。在模式1和2中,CKP低时间等于序列化程序的CKREF周期的一半。在模式3,CKP LOW等于CKREF周期。CKP高时间近似等于频闪周期,减去CKP低时间。

LVCMOS数据I/O

LVCMOS输入缓冲器具有标称阈值值等于一半VDD。只有当设备作为序列化程序运行时,输入缓冲区才可操作。当设备作为反序列化程序运行时,输入被关闭以节省电力。LVCMOS三态输出缓冲器的额定值为1.8V的源/汇电流约为0.5Ma。当DIRI信号和S1或S2被断言为高。当DIRI信号和S1或S2被断言为低,双向LVCMOS I/o处于高Z状态。纯电容下负载条件下,输出在GND和VDDP公司。当S1或S2最初转换为高时反序列化程序LVCMOS输出的状态为零。未使用的LVCMOS输入缓冲区必须绑定到有效逻辑低电平或有效逻辑高电平以防止由浮动输入引起的静态电流消耗。未使用的LVCMOS输出应保持浮动。未使用的双向引脚应通过高值连接到GND电阻器。如果将FIN224AC设备配置为单向序列化程序,则未使用的数据I/O可以被视为未使用的输入。如果FIN224AC被硬连线为反序列化器,则未使用的数据I/O可以被视为未使用的输出。

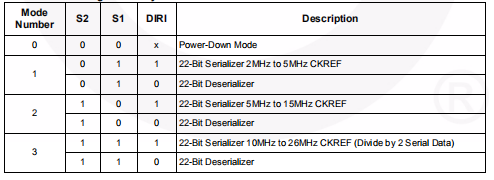

应用程序模式图

挠性电路设计指南串行I/O信息以高串行速率传输。必须注意实现这个串行I/O flex有线电视。在开发flex布线或flex PCB时,应使用以下最佳实践:保持所有四根差动导线的长度相同。不允许在差分串行线上方或附近出现噪声信号。示例:差分导线上没有LVCMOS痕迹。仅使用一个接地平面或差动串行线。不要从上到下跑地面。不要将测试点放在差动串行线上。使用差分串行线,距离天线至少2厘米

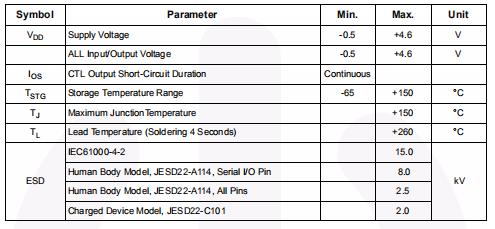

绝对最大比率

压力超出绝对最大比率可能损坏设备。The device may not function or be operatible above the recommended operating conditions and stressing the parts to these levels is not recommended.In addition,extended exposure to stresses above the recommended operating conditions may affect device reliability.茶绝对最大比率仅为应力比

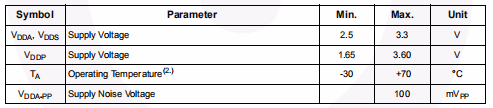

推荐操作条件

推荐操作条件表定义了实际设备操作的条件。推荐规定了操作条件,以确保达到数据表规范的最佳性能。费尔柴尔德没有推荐超过或设计到绝对最大额定值。

注:

2.绝对最大额定值是DC值,超过该值,设备可能损坏或其使用寿命受到损害。应毫无例外地满足数据表规范,以确保系统设计在其电源、温度和输出/输入负载变量。Fairchild不建议在外部操作数据表规范

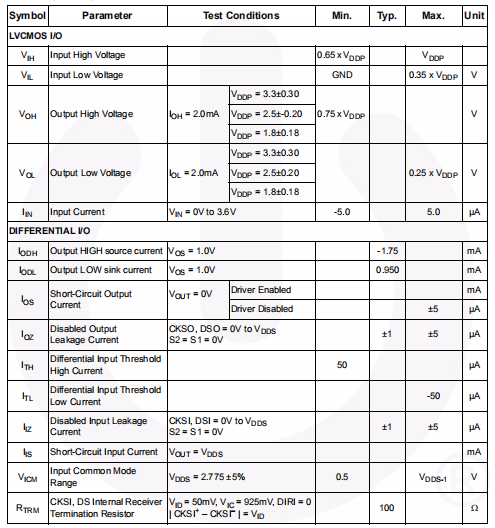

直流电特性

除非另有规定,否则该值适用于过电压和工作温度范围。典型值为给出的VDD=2.775V和TA=25°C。正电流值是指流入设备的电流和负电流数值是指从管脚流出的电流。除非另有规定,电压参考接地(除了ΔVOD和VOD)。

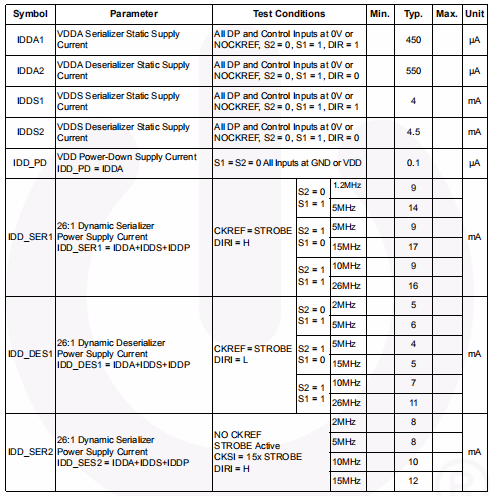

电源电流

给出了VDD=2.775V和TA=25°C的典型值。正电流值是指流入器件和负值是指从管脚流出的电流。电压参考接地,除非另有规定(ΔVOD和VOD除外)。

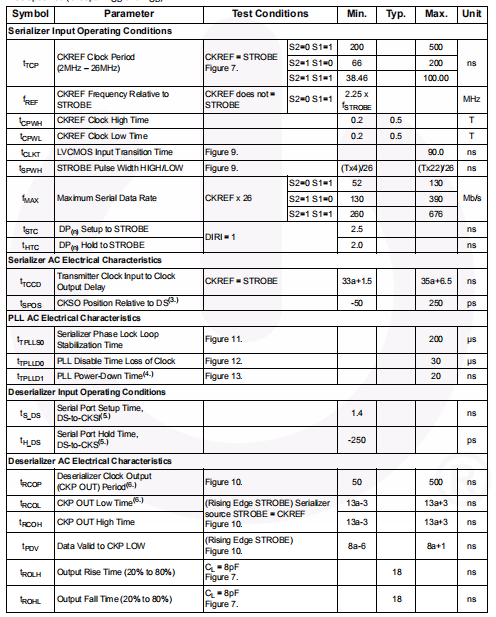

交流电气特性

推荐过电压和工作温度范围下的特性,除非另有规定。给出了VDD=2.775V和TA=25°C的典型值。正电流值是指流入器件和负值表示电流从管脚流出。除非另有规定,否则电压参考接地(除了ΔVOD和VOD)。

笔记:

3.偏差是从CKSO时钟的上升沿或下降沿到数据的上升沿或下降沿(DSO)测量的。信号边缘对齐。两个输出应具有相同的负载条件,此测试才有效。

4.断电时间是CKREF高或低停止前CKREF频率的函数,并且S1/S2模式管脚的状态。PLL被禁用所需的特定时钟周期数是不同的取决于设备的工作模式。

5.信号从序列化程序源同步传输。注意,在某些情况下,当时钟仍处于高位。只有当数据和时钟同时转换时,才应测量偏差时间。总的测量输入偏差是来自序列化程序的输出偏差、负载变化和ISI的组合以及抖动效应。

6.在CKP输出下降沿之后,CKP的上升沿出现约13比特的CKP上升沿。坠落CKP的边缘在数据转换之后或在下降沿之后的六比特时间发生大约八比特的时间。克索。数据相对于CKP信号的变化是由于不同数据管脚上的数据和CKP路径及传播延迟差异。注意,如果CKREF不等于对于串行器的选通,CKP信号不保持50%的占空比。CKP的低时间保持13比特时间