150点击型号即可查看芯片规格书

340点击型号即可查看芯片规格书

说明

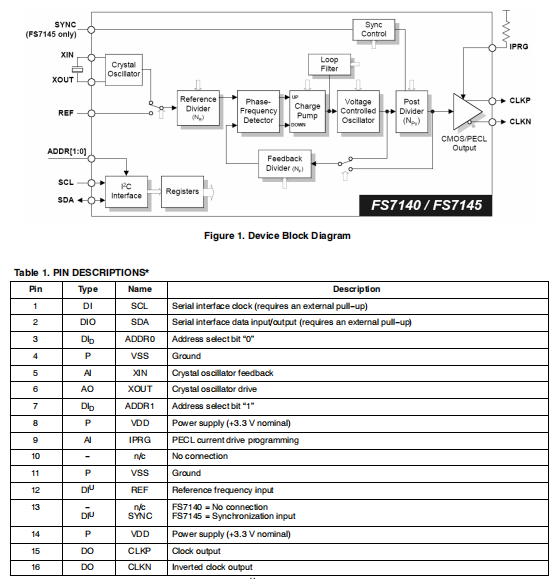

FS7140或FS7145是单片CMOS时钟发生器/再生器集成电路的设计使成本和元件数量最小化各种电子系统。通过I2C总线接口FS7140/45可以适应许多时钟生成要求。参考和反馈分配器的长度粒度和后分频器的灵活性使FS7140/45最灵活的立场-单独PLL时钟发生器可用。

特征

极灵活、低抖动的锁相环(PLL)频率合成无需外部回路过滤器组件150 MHz CMOS或340 MHz PECL输出通过I2C总线完全可配置单个I2C总线上最多可使用四个FS714x3.3 V操作独立片上晶体振荡器和外部基准输入非常低的“累积”抖动提供无铅包装

应用

精确频率合成

低频时钟倍增

视频线路锁定时钟生成

激光束打印机(FS7145)

键:AI:模拟输入;AO=模拟输出;DI=数字输入;DIU=带内上拉的输入;DID=带内下拉的输入;DIO=数字输入/输出;DI-3=三电平数字输入;DO=数字输出;P=电源/接地;#=有效低引脚

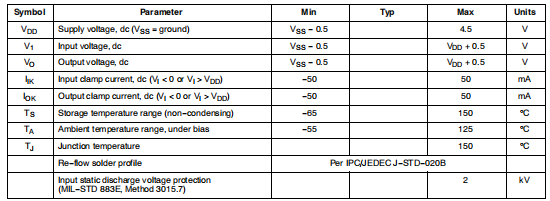

表2.绝对最大额定值

超过最大额定值的应力可能损坏设备。最大额定值仅为应力等级。功能操作高于建议的操作条件不是隐含的。长时间暴露在高于推荐操作条件的应力下可能会影响设备可靠性。警告:静电敏感装置如果该设备受到高能静电放电。

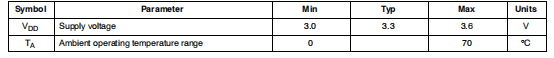

表3.操作条件

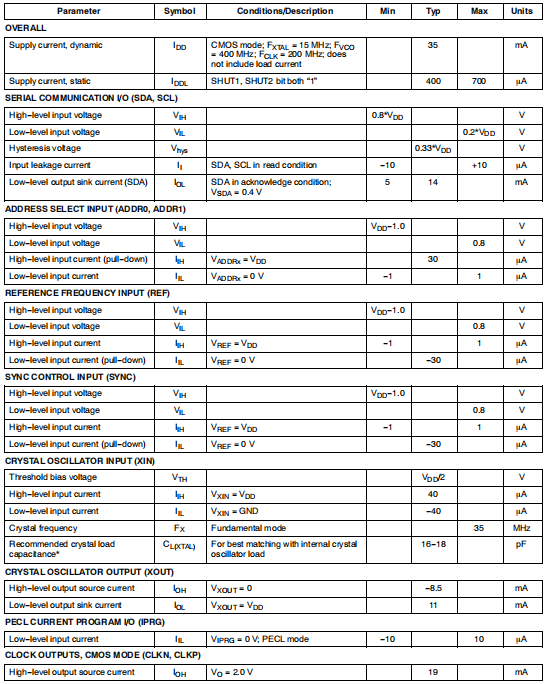

表4.直流电气规范(注1)

1.除非另有说明,VDD=3.3V%10%,任何输出无负载,环境温度范围TA带星号(*)表示标称特性数据,不会产生任何特定限制的实体。最小和最大特征数据来自典型。负电流表示流出装置。

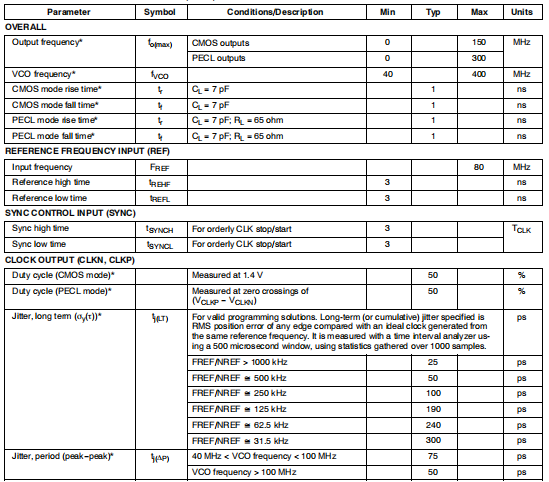

表5.交流定时规范(注2)

2.除非另有说明,VDD=3.3V%10%,任何输出无负载,环境温度范围TA带星号(*)表示标称特性数据,不会产生任何特定限制的实体。最小和最大特征数据来自典型。

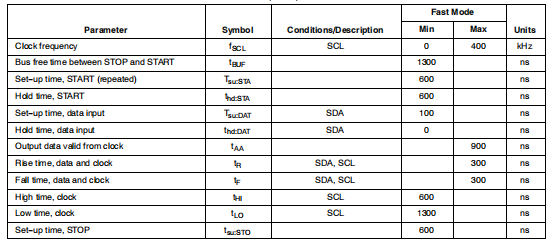

表6.串行接口定时规范(注3)

3.除非另有说明,VDD=3.3V%10%,任何输出无负载,环境温度范围TA带星号(*)表示标称特性数据,不会产生任何特定限制的实体。最小和最大特征数据来自典型。

锁相环

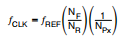

锁相环是一个标准的相位和频率锁定环建筑。锁相环由一个参考分压器、一个相位频率检测器(PFD)、电荷泵、内部环路滤波器,一个电压控制振荡器(VCO),一个反馈分频器和后分频器。参考频率(由板上晶体振荡器或外部频率源,首先由参考分压器减小。整数值频率除以被称为模表示为参考分压器的NR。这个分裂了然后将参考输入PFD。VCO频率通过反馈分频器(模数用NF表示)。PFD将驱动VCO频率上升或下降,直到分参考频率和分压控振荡器出现在PFD输入端的频率是相等的。这个参考频率之间的输入/输出关系VCO频率为: 这个基本的PLL方程可以重写为

这个基本的PLL方程可以重写为

标杆分隔器(实际上是三个标杆的一系列组合分频器)遵循PLL和设备的最终方程输出频率为:

参考分压器

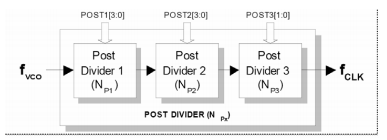

参考分压器是为低相位抖动而设计的。这个分频器接收任一晶体振荡器的输出电路或外部参考频率。参考文献除法器是一个12位除法器,可以为任何模数从1到4095(除以1,日期不可用0108之前的代码)。反馈分配器反馈分频器基于双模分频器(也称为双模预分频器)技术。它允许除以12到16383之间的任何整数值。简单地用二进制等价物对FBKDIV寄存器进行编程所需的模量。12以下的选定模块被允许。也允许4、5、8、9和10的模(4在0108年之前的日期代码中没有5)。立柱分隔器分柱器由三个单独的可编程分割器,如图所示。

各个分压器的模表示为NP1、NP2和NP3,它们一起构成了阵列模净现值。NPX=NP1 x NP2 x NP3后除法器执行几个有用的功能。第一,它允许VCO在与输出时钟速度的变化相比设备需要生成。第二,额外的整数分母允许更多的灵活性。许多应用程序的循环编程频率必须准确地达到。注意,标称50/50占空比始终保持不变(对于具有奇数模的选择,为偶数)。更多信息见表12。晶体振荡器FS7140配备有穿孔型晶体振荡器。晶体以并联谐振模式工作。为晶体提供内部负载电容。当规定了晶体的推荐负载电容,其他标准负载电容的晶体可用于参考频率的高精度(100 ppm或更低)不是必需的。参考分压源MUX参考分频器的频率源可以是选择作为设备晶体振荡器或参考管脚REFDSRC位。不使用晶体振荡器时,最好将XIN连接到VSS。不要连接到XOUT。当不使用REF输入时,最好保留它浮动或连接到VDD。反馈分频源多路复用器反馈分频器的频率源可以是选择为后除法器的输出或通过FBKDSRC位输出VCO。

通常,对于频率合成,VCO的输出使用。仅当输出时钟之间的确定相位关系需要参考时钟(线路锁定模式,用于示例)。设备关闭提供两个位,以便在以下情况下关闭设备:需要,当它不活动时。SHUT1禁用大多数外部可观察的设备功能。关闭2减少设备静态电流至绝对最小值。通常,这两个位应该一起设置或清除。串行通信功能未被禁用关闭1或关闭2。差动输出级差分输出级同时支持CMOS和伪ECL(PECL)信号。所需的输出接口通过编程寄存器选择。如果使用PECL接口,传输线通常是用塞维宁终止。输出级只能在PECL模式下接收电流,并且接收器电流由锁定/IPRG引脚。输出漏电流与IPRG之比电流是13:1。提供CLKx引脚的源电流通过作为Thévenin一部分的上拉电阻终止。

例子

假设需要连接PECL型扇形分叉就在FS7140旁边。进一步假设:VDD=3.3伏期望的VHI=2.4 V期望VLO=1.6 V等效负载=75欧姆

然后:R1(从CLKP和CLKN输出到VDD)=负载*VDD/VHI=75*3.3/2.4倍=103欧姆R2(从CLKP和CLKN输出到GND)=负载*VDD/(VDD-VHI)=75*3.3/(3.3-2.4)=275欧姆Rprgm(从VDD到IPRG引脚)=26*(VDD*R负载)/(VHI-VLO)/3=26*(3.3*75)/(2.4-1.6)/3个=2.68千欧

同步电路

FS7145支持几乎即时调整同步输入的输出时钟相位。两边同步方向(正向或负向)为支持。示例(选择正向同步):在同步输入的负边缘,序列开始停止CLK输出。在正边缘,CLK恢复操作,同步到同步输入的阶段(加上确定的延迟)。这是由设备立柱分隔器。相位分辨率等于VCO周期可以实现(大约下降到2纳秒)。I2C-总线控制接口这个设备是一个读/写从设备,可以满足所有飞利浦I2C-总线规格,除了“一般呼叫”。总线由产生串行数据的主设备控制时钟SCL,控制总线访问并生成启动当设备作为从属设备工作时的停止条件。两者主从机可以作为发射机或接收机工作,但是主设备决定激活哪种模式。一个将数据发送到总线的设备定义为发送器,以及作为接收器接收数据的装置。I2C-此处所述总线逻辑电平基于电源(VDD)的百分比。逻辑一对应于VDD的标称电压,而逻辑为零对应于接地(VSS)。公共汽车状况总线上的数据传输只能在总线不忙。在数据传输期间,数据线(SDA)每当时钟线(SCL)高时必须保持稳定。当时钟线高时,数据线的变化将是由设备解释为启动或停止条件。以下总线条件由I2C总线定义协议。数据线(SDA)和时钟线(SCL)都保持在表示总线不忙。开始数据传输SCL时SDA线的高低转换输入高表示启动条件。所有命令设备前面必须有一个启动条件。停止数据传输SCL输入时SDA线从低到高的转换高表示停止状态。所有命令设备必须遵循停止条件。数据有效如果SDA在SCL的高周期内线路是稳定的开始条件发生后的行。SDA上的数据只能在SCL处于低水平期间更改线路信号。每个数据位有一个时钟脉冲。

每次数据传输都是由启动条件和以停止条件终止。数据字节数在启动和停止条件之间传输由主设备决定,并可以继续无限期。但是,覆盖到设备的数据在前8个字节溢出到第一个寄存器之后,然后第二个,依此类推,在第一个,第一个覆盖时尚。承认当寻址时,接收设备需要在接收到每个字节后生成确认。这个主设备必须产生额外的时钟脉冲以一致带确认位。确认设备必须在主机处于高位期间,将SDA线拉低确认时钟脉冲。设置和保持时间必须为考虑在内。主设备必须通过生成并确认最后一个字节上的位从奴隶身上读出(计时)。在这种情况下,奴隶必须保持SDA行高,使主机能够生成停止条件。I2C-总线操作所有可编程寄存器可随机访问或通过此双向双线数字接口。晶体振荡器不必运行沟通发生。设备接受以下I2C总线命令:从机地址生成启动条件后,总线主机广播一个7位从机地址,后跟一个R/W位。设备的地址是:

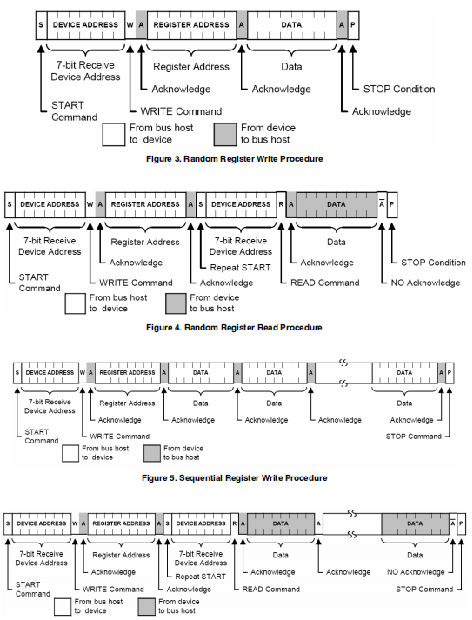

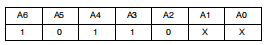

其中X由ADDR引脚的逻辑电平控制。可选的ADDR位允许四种不同的FS7140设备存在于同一总线上。请注意,上的每个设备I2C总线必须具有唯一地址,以避免可能的总线冲突。随机寄存器写入过程随机写入操作允许主机直接写入任何寄存器。要启动写过程,R/W在七位设备地址为逻辑-低。这向寻址从设备指示从设备后面会跟着一个寄存器地址确认其设备地址。注册地址是写入从机的地址指针。跟随从机确认,允许主机写入地址寄存器中的八位数据。决赛设备返回确认,主机生成停止条件。如果发生停止或重复启动条件在寄存器写入过程中,传输的数据是忽略。

随机寄存器读取过程随机读取操作允许主机直接读取从任何登记处。要执行读取过程,R/W位在七位地址为逻辑低位后传输,在寄存器写入过程中。这表明寄存器地址将跟随的寻址从设备从设备确认其设备地址后。这个然后寄存器地址被写入从机地址指针。在确认下生成重复的启动条件。重复的START终止写过程,但在设置了从机的地址指针。从机地址是重新发送,此时R/W位设置为逻辑高位,指示从机读取数据。奴隶会确认设备地址,然后发送八位字。主人不承认传输但确实生成停止条件。顺序寄存器写入过程顺序写入操作允许主机写入每个寄存器按顺序排列。寄存器指针是自动的每次写入后递增。这个过程比随机寄存器高效如果有多个寄存器必须是书面的。要启动写过程,R/W位是在七位设备地址之后传输的是逻辑低。这向寻址从设备指示从设备确认其设备地址。注册地址写在从机地址指针。在收到从机,主机可以写入8字节的数据在寄存器地址指针之前进入地址寄存器溢出回起始地址。设备在每个数据字节之间的确认必须在发送下一个数据字节之前发生。每次设备发送向主人致意。

寄存器更新不等待使停止条件发生。因此,寄存器在顺序寄存器写入期间的不同时间更新。顺序寄存器读取程序顺序读取操作允许主机从每个寄存器按顺序排列。寄存器指针是自动的每次读取后递增一。这个过程比随机寄存器更有效必须阅读。要执行读取过程,R/W位是在七位地址之后传输的是逻辑低,如寄存器写入过程。这表示地址从设备,在从设备之后跟随一个寄存器地址设备确认其设备地址。登记册然后将地址写入从机的地址指针中。在确认下生成重复的启动条件。重复的START终止写过程,但在设置了从机的地址指针。从机地址是重新发送,此时R/W位设置为逻辑高位,指示从机读取数据。奴隶会确认设备地址,然后发送所有8个从初始地址寄存器开始的数据字节。这个如果初始寄存器地址大于零。在数据的最后一个字节之后主服务器不确认传输,但确实生成停止状态。