一般说明

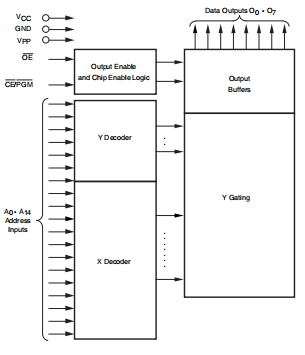

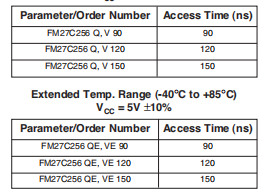

FM27C256是一个256K电可编程只读记忆。它是用Fairchild最新的CMOS分瓣门制造的EPROM技术,使其能够以同样快的速度运行整个工作范围内的90 ns访问时间。FM27C256为大部分操作系统和应用软件。其90 ns的访问时间提供高速使用高性能CPU运行。FM27C256提供单片机解决方案对代码存储要求100%基于固件的设备。常用软件程序从EPROM存储器中快速执行,大大增强了系统实用程序。FM27C256在标准EPROM引脚中配置它为目前正在使用标准EPROM。方块图2001年5月FM27C256是高密度EPROM系列的一个成员其密度范围可达4MB。

特征

高性能CMOS-90、120、150 ns访问时间JEDEC标准引脚配置-32针PLCC封装-28针CERDIP封装替换27C256或27256

包装类型:FM27C256 Q,V XXXQ=石英窗陶瓷浸渍V=表面贴装PLCC所有包装符合JEDEC标准。保证所有版本都能以较低速度运行

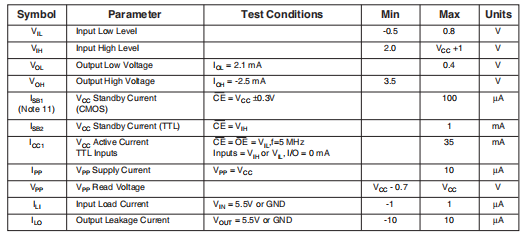

绝对最大额定值(注释1)储存温度-65°C至+150°C除A9外的所有输入电压相对于地面-0.6V至+7V关于VPP和A9接地-0.7V至+14V

VCC电源电压相对于地面-0.6V至+7V静电放电保护>2000V所有输出电压相对于地VCC+1.0V至地-0.6V

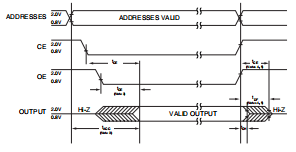

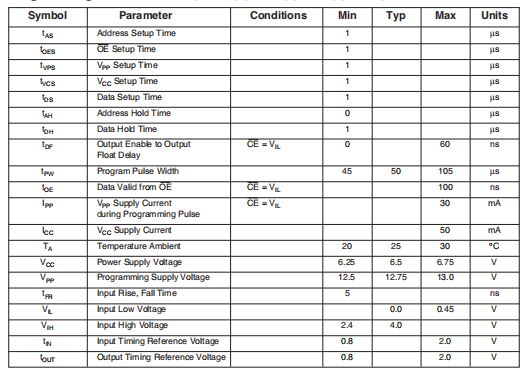

交流试验条件输出负载1 TTL门和CL=100 pF(注8)输入升降时间≤5ns输入脉冲电平0.45至2.4V定时测量参考电平(注10)输入0.8V和2.0V输出0.8V和2.0V

注1:在“绝对最大额定值”下列出的应力可能对设备造成永久性损坏。这只是压力等级和功能操作在本规范操作章节中所述的上述条件或任何其他条件下的装置并不隐含。暴露于绝对最大额定值条件下延长时间可能会影响设备的可靠性。

注2:该参数仅取样,未经100%测试。

注3:在CE下降边缘后,在不影响tACC的情况下,OE可延迟至tACC-tOE。

注4:tDF和tCF比较水平确定如下:高至三态,测量VOH1(DC)-0.10V;低至三态,测量VOL1(DC)+0.10V。

注5:三态可使用OE或CE实现。

注6:EPROM的电源开关特性需要小心的设备去耦。建议在每个装置上至少使用0.1μF陶瓷电容器在VCC和GND之间。

注7:输出必须限制在VCC+1.0V,以避免锁存和设备损坏。

注8:TTL栅极:IOL=1.6毫安,IOH=-400微安。CL=100pF包括夹具电容。

注9:VPP可以连接到VCC,编程期间除外。

注10:输入和输出可能低于-2.0V,最大20 ns。

注11:CMOS输入:VIL=GND±0.3V,VIH=VCC±0.3V。

注12:Fairchild的标准产品保修适用于根据本文所述规范编程的设备。

注13:VCC必须同时使用或在VPP之前使用,同时或在VPP之后移除。不得将EPROM插入或从带有施加在VPP或VCC上的电压。

注14:最大绝对允许电压,可应用于编程期间的VPP引脚是14V。防止超过14V最大规格的过冲。VPP、VCC和GND之间至少需要一个0.1μF的电容器,以抑制杂散电压瞬变可能会损坏设备。

注15:通电过程中,必须使PGM引脚处于高电平(≥VIH),要么与VPP同时通电,要么在向VPP通电之前

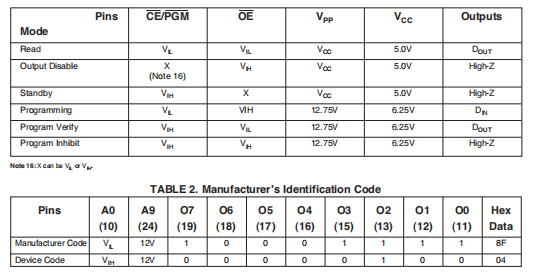

功能描述设备操作:表1列出了EPROM的六种工作模式。它应注意的是,六种模式的所有输入都处于TTL水平。所需电源为VCC和VPP。VPP电源在三种编程模式下,电源电压必须为12.75伏,在其他三种模式下必须是5V。VCC电源在三种编程模式下必须为6.5V,并且为5V在其他三种模式下。读取模式EPROM有两个控制功能,它们都必须是逻辑上是活动的,以便在输出端获得数据。芯片启用(CE/PGM)是电源控制,应用于设备选择。输出启用(OE)是输出控制,应该是用于将数据传送到输出管脚,与设备无关选择。假设地址是稳定的,地址访问时间(tACC)等于从CE到输出(tCE)的延迟。数据是在输出前束处,在OE下降沿后可用,假设CE/PGM一直很低,地址稳定至少是tACC-tOE。待机模式EPROM有一个备用模式,可以降低有功功率损耗超过99%,从385兆瓦到0.55兆瓦。EPROM通过将CMOS高信号应用于CE/PGM输入。当处于待机模式时,输出处于高阻抗状态,独立于OE输入。输出禁用通过应用TTL high,EPROM处于输出禁用状态发送到OE输入的信号。当输入输出禁用时,所有电路已启用,但输出处于高阻抗状态(三态)。输出或键入因为EPROM通常用于较大的内存阵列,Fairchild提供了一个二线控制功能,可容纳多个内存连接的使用。二线控制

功能允许:

1.尽可能低的内存功耗,以及

2.完全保证输出总线争用不会发生。为了最有效地使用这两条控制线,建议CE/PGM被解码并用作主要的设备选择功能,而OE则与所有的阵列中的设备,并连接到系统控制总线。这确保所有取消选择的内存设备处于低功耗待机模式,并且仅当需要特定存储器中的数据时,管脚才处于活动状态装置。

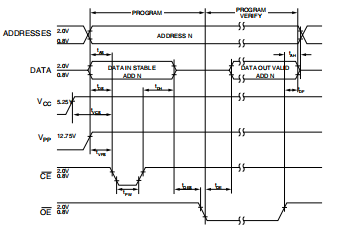

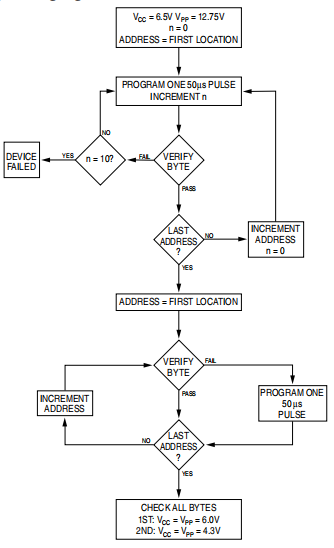

程序设计注意:引脚1(VPP)上超过14V会损坏EPROM。最初,在每次擦除之后,EPROM的所有位都在“1”状态。通过选择性编程“0”引入数据进入所需的位位置。虽然只有“0”将被编程,但“1”和“0”都可以在数据字中显示。将“0”改为“1”的唯一方法是紫外线擦除。当VPP通电时,EPROM处于编程模式电源电压为12.75V,运行经验为VIH。要求至少将0.1μF电容器放置在VPP、VCC和接地之间,以抑制可能损坏设备的杂散电压瞬变。这个要编程的数据与数据并行应用8位输出引脚。地址和数据输入所需的级别是TTL。当地址和数据稳定时,一个活跃的低TTL程序脉冲应用于CE/PGM输入。程序脉冲必须是应用于要编程的每个地址位置。EPROM使用涡轮编程算法编程,如图。每个地址用一系列50微秒进行编程脉冲,直到验证良好,最多达10个脉冲。大多数存储单元将使用单个50微秒脉冲进行编程。(标准国家半导体算法也可以使用,但它将编程时间更长。)EPROM不得使用应用于CE/PGM输入。用同一数据并行编程多个EPROM由于编程简单,容易实现要求。并联EPROM的类似输入可以被连接当使用相同的数据对它们进行编程时。低谷应用于CE/PGM输入程序的电平TTL脉冲并行EPROM。

程序禁止用不同的数据并行编程多个eprom是也容易做到。除了CE/PGM,所有的输入都一样并行eprom的(包括OE)可能是常见的。一个TTL应用于EPROM的CE/PGM输入的低电平程序脉冲当VPP为12.75V时,将对EPROM进行编程。TTL高水平CE/PGM输入禁止对其他EPROM进行编程。程序验证应在编程位上进行验证,以确定是否正确编程。验证可能是在12.75V下用VPP执行。VPP必须在VCC上,除非在编程和程序验证。编程后不透明标签应贴在EPROM窗口上防止无意擦除。遮住窗户也会防止由于生成照片而导致的临时功能故障海流。制造商识别码EPROM有一个制造商的识别码来帮助编程。当设备插入EPROM编程器插座时,编程器读取代码,然后自动调用部分。这种自动编程控制只有在有读代码能力的程序员。制造商的识别码,如表所示,专门用于识别制造商和设备类型。的代码FM27C256是“8F04”,其中“8F”表示它是由飞兆半导体,“04”表示256K部件。通过对地址引脚A9施加12V±0.5V电压来访问该代码。地址A1-A8、A10-A16和所有控制销均位于VIL。地址pin A0保留在VIL中,用于制造商代码,并保留在VIH获取设备代码。在8个数据管脚上读取代码,O0–O7。只有在25°C到±5°C的温度下才能保证正确的代码访问。

功能说明(续)擦除特性设备的擦除特性是这样的当暴露在波长较短的光下时开始发生大于约4000埃。应该指出的是日光灯和某些类型的荧光灯有波长在3000至4000奥内。EPROM建议的擦除程序是暴露在波长为2537奥。综合剂量(即紫外线强度x暴露时间)擦除应至少为15W sec/cm~2。EPROM应放置在灯管的1英寸范围内在擦除过程中。有些灯的灯管上有一个过滤器应在擦除前删除擦除系统应定期校准。距离从灯到装置的距离应保持在1英寸。抹去时间随着距离灯距离的平方而增加(如果距离加倍擦除时间增加4倍)。灯随着年龄的增长而减弱。当一盏灯被更换时距离改变或灯老化,系统应检查以确定正在进行完全擦除。

不完整擦除会导致可能误导的症状。当不完全擦除是问题时,程序员、组件甚至系统设计都被错误地怀疑。系统考虑EPROMs的功率开关特性需要注意设备的去耦。电源电流ICC有三个系统设计器感兴趣的段:备用电流水平、有功电流水平和暂态电流由输入引脚上的电压跃迁产生的峰值。这个这些瞬态电流峰值的大小取决于装置输出电容负载。相关VCC通过适当的选择可以抑制瞬态电压峰值去耦电容器。建议至少为0.1μF在VCC和地面。这应该是一个低固有频率的高频电容器电感。此外,至少有一个4.7μF的块状电解电容器应在VCC和GND之间为每八个设备使用。这个大容量电容器应位于电源附近连接到阵列。大容量电容器的用途是克服PC板痕迹。

模式选择表1列出了FM27C256的工作模式。读取模式下需要一个5V电源。所有输入均为TTL电平除了VPP和A9用于设备。