特征

8Mbit铁电非易失性存储器

组织为512Kx16

使用/UB,/LB配置为1Mx8

高耐久性100万亿(1014)读/写

NoDelay8482;写入

页面模式操作至33MHz

先进的高可靠性铁电工艺SRAM兼容

JEDEC 512Kx16 SRAM引脚

60 ns访问时间,115 ns周期时间

高级功能

低VDD显示器保护内存免受

意外写入

优于电池支持的SRAM模块

无电池问题

整体可靠性

真正的表面贴装解决方案,无返工步骤

防潮、防震、防震性能卓越

低功率运行

2.7V–3.6V电源

14毫安有功电流

行业标准配置

工业温度-40°C至+85°C

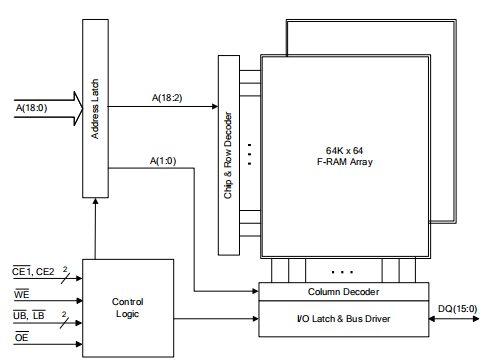

8针“绿色”RoHS FBGA封装

说明

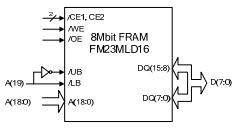

非易失性记忆体阅读和写作像一个标准的SRAM。到铁电随机存取存储器非挥发性的,这意味着数据在输入后被重新输入。电源已清除。IT provides data retention for over10年来,消除了可靠性问题,功能缺陷与系统设计电池后备SRAM(“BBSRAM”)的复杂性快速写作时间和极高的写作耐力使F-RAM高级到其它类型的存储器。在系统操作中类似于其它随机存储器设备,可以用作Drop-in replacement for standard SRAM.读与读文字循环可以被芯片触发简单地改变地址。F-RAM记忆体由于其独特的铁电而非挥发性记忆过程这些特征使得非易失性存储器理想应用程序要求频繁或快速写入Form of an SRAM.包括一个低电压监视器当VDD时,该块存取到存储器阵列在临界阈值下下降记忆是防止不适当的存取和数据在这种情况下腐败The FM23MLD16 F-RAM is available in a 48-ball表面安装包设备规格在工业温度范围内有保障吗从-40°C到+85°C。

笔记:

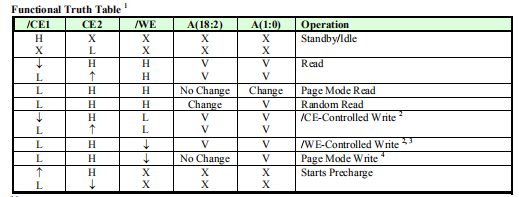

1)H=逻辑高,L=逻辑低,V=有效数据,X=无所谓。

2)对于写入周期,数据输入锁定在/CE1的上升沿或CE2下降沿的/WE上,以先到者为准。

3)/我们控制的写入周期从读取周期开始,然后锁存(18:3)。

4)在页面模式操作期间,地址A(2:0)必须保持至少15 ns的稳定。

概述

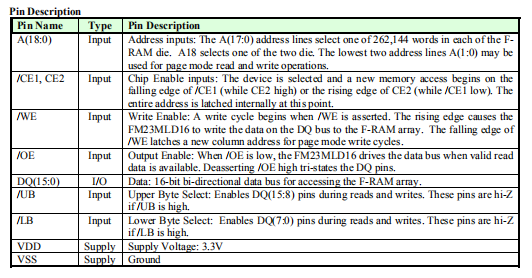

FM23MLD16是一个全字F-RAM存储器逻辑组织为524288 x 16并访问使用工业标准并行接口。所有数据写在零件上是立即不易挥发的,没有延迟。设备提供页面模式操作提供对页(行)。将触发对其他页的访问通过切换芯片使能管脚或简单地通过改变上层地址A(18:2)。存储器操作用户访问524288个内存位置,每个位置都有通过并行接口的16个数据位。F-RAM内存组织为两个die,每个die有64K行。每行有4个列位置,允许快速页面模式下的访问操作。首字母一次地址已被/CE1的下降沿锁定(当CE2高)或CE2上升沿(当/CE1低),随后的列位置可能是无需切换芯片启用即可访问。当任一芯片使能管脚被拔出时预充电操作开始。发生写入在访问结束时立即访问。每次写入时必须切换/WE pin操作。写入数据存储在非易失性中立即存储阵列,这是一个独特的功能到名为NoDelayTM的F-RAM写入。

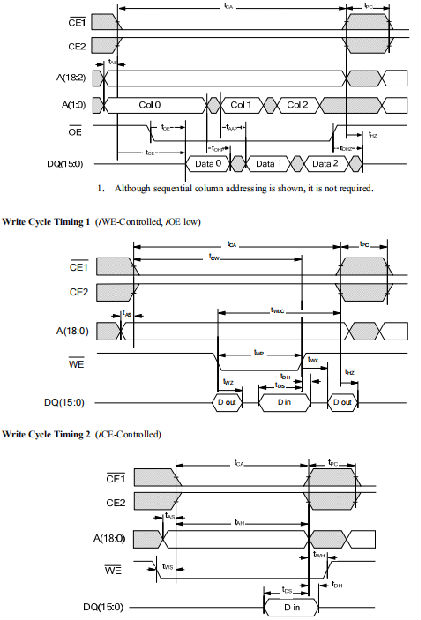

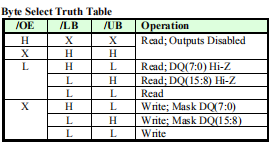

读取操作读取操作从/CE1的下降沿开始(当CE2高)或CE2上升沿(当/CE1低)。/CE启动的访问导致要锁定的地址并开始内存读取循环如果我们很兴奋。数据在总线上可用在访问时间满足后。一旦地址已锁定,访问已完成,a对随机位置(不同行)的新访问可能在两个芯片启用仍处于活动状态时开始。这个随机地址的最小循环时间是tRC。注意,与sram不同的是,FM23MLD16的/初始化访问时间比地址周期快时间。当/OE时,FM23MLD16将驱动数据总线至少有一个字节使能(/UB,/LB)是断言低。当/UB低,当/LB为低。如果在内存访问时间之后断言/OE已满足,数据总线将使用有效数据。如果/OE在完成之前被断言内存访问,数据总线将不被驱动直到有效数据可用。此功能将最小化通过消除瞬变在系统中提供电流由驱动到总线上的无效数据引起。当/OE被解除高配置时,数据总线将保持高Z状态。

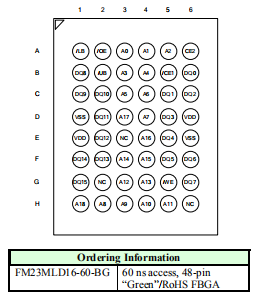

写操作

写入同时发生在FM23MLD16中间隔为读取。FM23MLD16同时支持/CE-和/我们控制写入周期。在这两种情况下,地址A(18:2)锁定在/CE1(CE2高)或CE2上升沿(当/CE1低时)。在a/CE控制写入中,断言/WE信号在开始内存循环之前。就是说,/我们是低当设备被芯片激活时。在这种情况下,设备以写。FM23MLD16不会驱动数据总线不管/OE的状态,只要/WE是低的。当设备为通过芯片启用取消选择。在a/我们控制写入,当设备通过芯片启用激活。我们的信号下降了一段时间后。因此,存储周期开始作为阅读。如果/OE低,数据总线将被驱动,然而,一旦/我们被断言为低,它将是hi-Z。这个/CE-和/我们控制的写入定时情况是如电气规范章节所示。在写周期计时2图,显示数据总线当芯片被写入时,作为一个hi-Z条件在规定的安装时间之前。尽管这是它看起来像一个中等电压建议所有DQ引脚符合最低VIH/VIL操作水平。对数组的写访问从/我们在记忆周期开始后。写作访问在/WE、/CE1或CE2,以先到者为准。有效的写操作要求用户满足访问时间规范在解除资产/WE、/CE1或CE2之前。数据设置时间表示数据不能在写入访问结束之前更改(上升用/CE1或CE2)。与其他真正的非易失性存储技术不同,F-RAM没有写入延迟。从阅读开始底层内存的写访问时间是同样的,用户通过公共汽车。整个内存操作在一个公车循环。数据轮询,一种用于用于确定写入是否完成的eeprom没必要。

页面模式操作

FM23MLD16提供用户快速访问行元素中的任何数据。每行有4个列地址位置。地址输入A(1:0)定义要访问的列地址。通路可以从任何列地址和其他列开始无需切换即可访问位置CE管脚。对于快速访问读取,一旦第一个数据字节被驱动到总线上,列地址输入可以将(1:0)更改为新值。新数据字节不迟于tAAP被驱动到DQ引脚,不到初始读取访问时间的一半。对于快速访问写入,第一个写入脉冲定义第一次写入访问。选择设备时(两个芯片使能断言),随后的写入脉冲使用新的列地址提供页面模式写访问。预充电操作预充电操作是记忆的状态正在为新通道。预充电是用户通过在至少一个芯片使能信号国家。它必须至少保持在最低点预充电时间tPC。

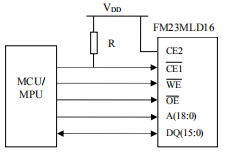

SRAM插入替换FM23MLD16被设计成标准异步sram的替代品。这个设备不需要为每个设备切换CE管脚新地址。两个CE引脚都可能保持激活状态无限期。当两个CE引脚都激活时设备自动检测地址更改和新的通道已经开始。此功能允许芯片使能引脚被激活(/CE1接地,CE2与VDD连接)就像SRAM一样。它也允许页面模式操作的速度高达33MHz。典型的应用程序如图2所示。它显示了上拉电阻器/CE1,保持引脚高在电源循环期间,假设MCU/MPU引脚在复位条件下三态。上拉电阻器应选择值以确保/CE1销轨VDD仍然是一个足够高的值当/CE1低时不是问题。尽管没有需要时,建议将CE2连接到VDD如果控制器提供有效的低芯片启用。

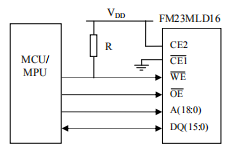

对于需要最低功耗的应用程序消耗,/CE1信号应仅激活在内存访问期间。FM23MLD16绘制当/CE1低时,即使地址控制信号是静态的。当/CE1为高时设备不超过最大待机时间当前ISB。注意,如果/CE1接地,CE2连接到VDD,用户必须确定/我们没有低功率或断电事件。如果芯片已启用并且/我们低功率循环期间,会发生数据损坏。图显示了一个上拉电阻在功率循环期间保持引脚高复位条件下MCU/MPU引脚三态。应选择上拉电阻值以确保/WE pin跟踪VDD,但值足够高当/我们处于低位时所消耗的电流不是问题。一个当/WE低时,10Kohm电阻消耗330uAVDD=3.3伏。

/UB和/LB字节选择管脚对这两个都有效读写循环。它们可以用来允许作为1Mx8内存连接的设备。上层较低的数据字节可以绑定在一起由字节选择控制。单个字节使能或下一个更高的地址行A(19)可以是可从系统处理器获得。

PCB布局建议应将0.1uF去耦电容器放置在附近每个电源/接地对(焊球1D/1E和6D/6E)。电容器的接地侧应为接地平面或低阻抗返回到VSS pins的路径。最好用芯片低ESR高性能电容器频率特性。如果控制器驱动地址和芯片启用从相同的时间边缘,最好保持地址路由短且长度相等。简单的RC电路可插入芯片使能路径为FM23MLD16的地址设置时间tAS。作为一般规则,布局设计器可能需要在控制器输出端增加串联终端电阻具有快速过渡或路径的长度。只有当边缘速率较低时,这才是必要的大于或等于往返跟踪延迟。信号过冲和回环可能大到足以引起不稳定的设备行为。最好加一个50欧姆输出驱动器附近的电阻器(30–60欧姆)(控制器)减少这种传输线效应。

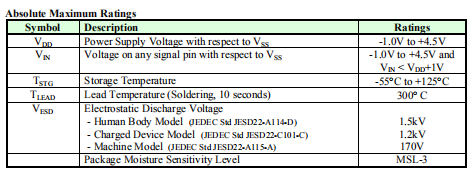

在绝对最大额定值以上列出的应力可能对设备造成永久性损坏。这是一个压力等级仅,以及设备在这些或任何其他条件下的功能操作规范不是隐含的。长时间暴露于绝对最大额定值条件可能影响器件可靠性。

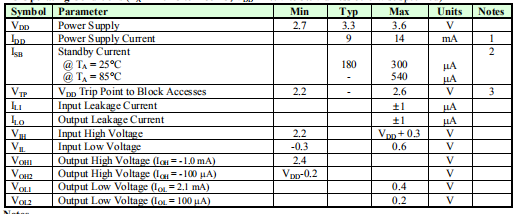

笔记

1.VDD=3.6V,CE引脚在最小循环时间循环。所有输入在CMOS电平(0.2V或VDD-0.2V)切换,所有DQ引脚卸下。

2.VDD=3.6V,/CE1(在VDD下)或CE2(在VSS下),所有其他引脚都是静态的,并且处于CMOS电平(0.2V或VDD-0.2V)。

3.如果VDD<VTP,则不管输入pin条件如何,所有内存访问都被阻塞。