128点击型号即可查看芯片规格书

说明

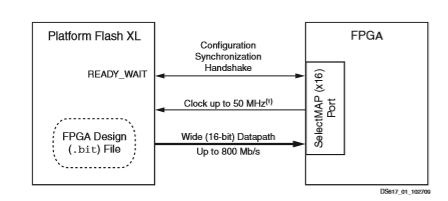

一个可靠的紧凑型高性能配置比特流存储和传输解决方案是高密度FPGAs必不可少的。平台Flash XL是业界性能最高的配置和存储设备,专门针对高性能FPGA配置进行优化。Platform Flash XL集成了128 Mb的系统内可编程闪存存储和性能功能,可在一个占地面积小的FT64包中进行配置。上电突发读取模式和专用I/O电源使平台Flash XL能够与本机SelectMAP配置接口无缝配合。宽的16位数据总线以高达800mb/s的速度传输FPGA配置位流,无需等待状态。

平台Flash XL仅支持与Virtex-5或Virtex-6 FPGAs一起使用。不支持与旧的Virtex系列、Spartan®系列或AES加密比特流一起使用。

平台Flash XL是一种非易失性闪存存储解决方案,针对FPGA配置进行了优化。该设备提供一个就绪等待信号,同步启动的FPGA配置过程,提高了系统的可靠性和简化了电路板的设计。Platform Flash XL可以在不到100毫秒的时间内下载XC5VLX330位流(79704832位),使Platform Flash XL的配置性能成为PCI Express端点和其他高性能应用程序的理想选择。

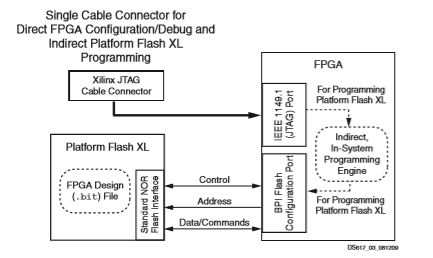

平台Flash XL是一个具有附加系统级功能的单芯片配置解决方案。标准NOR闪存接口(图2)和对公共闪存接口(CFI)查询的支持提供了对设备内存空间的行业标准访问。平台Flash XL的128mb容量通常可以容纳一个或多个FPGA比特流。任何不用于位流存储的内存空间都可以用来保存通用数据或嵌入式处理器代码。

笔记:

一。系统考虑可以降低配置时钟频率低于设备的最大时钟频率。为了确定最大配置时钟频率,检查所选择的I/O电压范围(V)、时钟高输出有效时间(T)和FPGA选择映射设置时间的最小时钟周期(T)。克赫滴滴涕KHQV公司

平台Flash XL提供可靠、高性能的FPGA配置

平台Flash XL支持与Xilinx X-Ref目标集成-

设计和调试工具套件。iMPACT应用程序包括在ISE软件中,支持通过用于原型编程的FPGA上的IEEE标准1149.1(JTAG)端口对平台Flash XL进行间接的系统内编程

闪存架构概述

平台闪存XL是一个128 Mb(8 Mb×16)非易失性闪存。该装置采用1.8V核心(V)电源进行系统编程。单独的I/O(V)电源可使I/O在3.3V或2.5V下运行。可选的9V电源可加速工厂编程。尽职调查滴滴涕聚丙烯

公共闪存接口(CFI)提供对设备存储器的访问。此外,平台Flash XL支持多种读取模式。23位地址总线提供对每个16位字的随机读取访问。四个字占据每一页的加速页模式阅读。设备在同步突发读取模式下通电,能够连续读取高达54mhz的速率。

平台Flash XL具有多银行体系结构。一个由131个单独可擦除块组成的阵列被划分为168mb的组。15个主块包含64 Kwords的统一块,1个参数块包含7个64 Kwords的主块,外加4个16 Kwords的参数块。

注:该装置可在块级进行电子擦除,并可逐字编程。

多银行架构允许双重操作-读操作可以发生在一个银行,而程序或擦除操作发生在另一个银行。但是,一次只允许一个银行处于程序或擦除模式。允许突发读取跨越银行边界。

地址输入(A22-A0)

地址输入选择在总线读取操作期间要访问的内存数组中的字。在总线写入操作期间,它们控制发送到程序/擦除控制器的命令接口的命令。

数据输入/输出(DQ15-DQ0)

数据I/O输出存储在选定地址的数据

在总线读取操作期间,或在总线写入操作期间输入命令或要编程的数据。

芯片启用(E)

芯片使能输入激活存储器控制逻辑、输入缓冲器、解码器和感测放大器。当芯片使能为V且复位为V时,设备处于激活模式。当芯片使能为V时,存储器被取消选择,输出为高阻抗,功耗降低到待机水平。伊利诺伊州IH公司IH公司

输出启用(G)

在存储器的总线读取操作期间,输出使能输入控制数据输出。在第一个地址锁存序列(FALS)开始之前,在时钟开始切换之前,输出使能输入必须保持在低位。

写入启用(W)

Write Enable输入控制内存命令接口的总线写入操作。数据和地址输入锁定在芯片使能或写使能的上升沿,以先发生者为准。

笔记:

一。有关详细信息,请参阅“直流和交流参数”部分中的波形。

时钟(K)

时钟输入在同步读取操作期间将存储器同步到FPGA。当锁存启用为V时,地址被锁存在时钟边缘(根据配置设置上升或下降)。在异步读写操作期间,时钟被忽略。伊利诺伊州

就绪/等待(就绪/等待)

注意安全就绪等待需要一个到VDDQ的外部上拉电阻器。外部上拉电阻必须足够强,以确保在就绪等待引脚释放到高阻抗状态时,在不到一微秒(TRWRT)的时间内实现干净、低到高的转换。

就绪等待可以执行两个功能之一。默认情况下,READY_WAIT是一个输入/开漏就绪信号,用于协调设备同步读取操作的启动和FPGA配置序列的启动。可选地,READY_WAIT可以动态配置为输出等待信号,指示同步读取操作期间的等待条件。

在上电复位(POR)或RP pin复位事件发生时,设备驱动器READY_等待V,直到设备准备好启动同步读取或接收命令。当设备从复位状态达到内部就绪状态时,就绪等待被释放到高阻抗状态(需要外部上拉电阻至V,以将就绪等待信号外部拉至有效输入高)。在允许同步读取或接受命令之前,设备将等待就绪等待输入变为有效的高输入。将READY_WAIT连接到有线和电路中的FPGA INIT_B管脚,创建一个握手,协调设备同步读取的启动和FPGA配置序列的启动。伊利诺伊州滴滴涕

当READY_WAIT是一个输入/开漏就绪信号时,系统可以将READY_WAIT驱动到V以重新启动同步读取操作。必须为重新初始化的同步读取操作向设备提供有效地址。伊利诺伊州

可选地,READY_WAIT可以配置为在同步读取操作期间发送等待条件信号的输出。等待条件表示输出数据无效的时钟周期。当配置为输出等待信号时,当芯片使能为V或输出使能为V时,就绪等待为高阻抗。只有当配置为等待信号时,就绪等待才能配置为在等待周期或提前一个时钟周期激活,并且可以配置就绪等待极性。IH公司IH公司

VDD电源电压

V为内存设备的内部核心提供电源,是所有操作(读取、编程和擦除)的主电源。尽职调查

VDDQ电源电压

V为I/O引脚提供电源,并使所有输出独立于V供电。滴滴涕尽职调查

VPP程序电源电压

V是控制输入或电源引脚,由施加到引脚的电压范围选择。聚丙烯

如果V保持在低电压范围(0V到V),则V被视为控制输入。在这种情况下,低于V的电压对程序或擦除提供绝对保护,而V范围内的V启用这些功能。V仅在程序或擦除的开始处采样-操作开始后其值的更改不会产生任何影响,并且所有程序或擦除操作都将继续。聚丙烯滴滴涕聚丙烯PPLK公司聚丙烯第1页聚丙烯

如果V在V的范围内,则该信号充当电源引脚。在这种情况下,V必须稳定,直到程序/擦除算法完成。聚丙烯PPH公司聚丙烯

VSS接地

V接地是核心电源的参考,必须连接到系统接地。党卫军

VSSQ接地

V接地是由V驱动的输入/输出电路的参考。V必须连接到V。SSQ公司滴滴涕SSQ公司党卫军

注:系统中的每一个设备都应该有VDD、VDDQ和VPP与靠近管脚的0.1μF陶瓷电容器分离(高频、固有低电感电容器应尽可能靠近封装)。PCB的磁道宽度应足以承载所需的VPP程序和擦除电流。

现场可编程门阵列配置概述

平台Flash XL支持丰富的FPGA配置特性,而无需额外的粘合逻辑。设备在通电时通过16位数据总线以高达800mb/s的数据速率传送FPGA比特流。还可以从存储在设备中的许多设计/修改比特流之一配置FPGA。这些修订比特流是通过使用平台Flash XL在特定系统配置中提供的FPGA的多引导寻址和回退功能来访问的。有关FPGA配置特性和配置过程的详细说明,请参阅相应的《FPGA配置用户指南》。

在高层次上,平台Flash XL的FPGA配置的一般过程如下:

1. 系统事件(如通电)启动FPGA配置过程。在清除配置内存的同时,FPGA将其INIT_B pin驱动到低位。平台闪存XL在重置期间将其就绪等待引脚调低。

2. 准备就绪后,FPGA和平台Flash XL释放各自的INIT_B和ready_等待管脚。外部电阻将

从低到高的INIT_B-READY_等待信号,同步启动FPGA配置过程。

3. 在配置过程开始时,FPGA采样其模式管脚以确定其配置模式。对于主BPI向上模式,FPGA输出一个地址从flash读取。对于Slave SelectMAP模式,板载电阻器设置初始闪存读取地址。

4. 平台Flash XL将来自FPGA或板载电阻器设置的初始地址锁存到其内部地址计数器中,平台Flash XL输出第一个16位字。

5. 位流从平台Flash XL同步传输到FPGA。在每个连续的FPGA CCLK周期中,平台Flash XL递增其内部地址计数器,并输出位流的下一个16位字供FPGA使用。

6. 在配置过程结束时,FPGA开始对加载的比特流进行操作,并将驱动器执行高电平或释放到高电平,指示配置过程完成。

笔记:

1. 800mb/s的速率是使用Virtex-5fpga和外部50mhz配置时钟源实现的。Virtex-6fpga的特定速度等级或系统级考虑可以将配置性能限制在800mb/s以下。

2. 带宽基于一个示例Virtex-5fpga,考虑F和BitGen配置率=31mhz(标称频率)。麦考托

3. 带宽基于一个示例Virtex-5fpga,考虑F和BitGen配置率=17mhz(标称频率)、bpi_page_size=4和bpi_1st_read_cycle=4。第一个字访问时间=110 ns;页字访问时间=25 ns。麦考托

4. 参见XAPP973,使用Virtex-5 FPGAs间接编程BPI PROMs。

平台Flash XL可以配置Slave SelectMAP(X16)中的FPGA(推荐用于最大性能)、Master SelectMAP(X16)或主BPI UP(X16)配置模式。不同配置模式和存储器的属性摘要见表4。

从SelectMAP配置模式

当FPGA处于Slave SelectMAP配置模式时,平台Flash XL实现了最大配置性能。在Slave SelectMAP模式下,稳定的外部时钟源可以驱动从设备到FPGA的同步比特流传输到最大突发读取频率(t)。参见各自的FPGA中的SelectMAP配置接口部分CLK公司

备用配置模式

Platform Flash XL针对Slave SelectMAP配置模式进行了优化。或者,平台Flash XL可以通过主选择映射或主BPI向上模式配置FPGA,尽管在配置速度上有所妥协。有关主SelectMAP模式或主BPI Up模式的详细信息,请参阅相应的《FPGA配置用户指南》。

见UG438,平台闪存XL配置和存储

设备用户指南,以获取有关在主选择映射或主BPI向上模式下使用平台Flash XL和FPGA的更多信息。

配置用户指南,以获取从属SelectMAP模式的详细信息。

注:在Slave SelectMAP模式下禁用了FPGA回退功能。

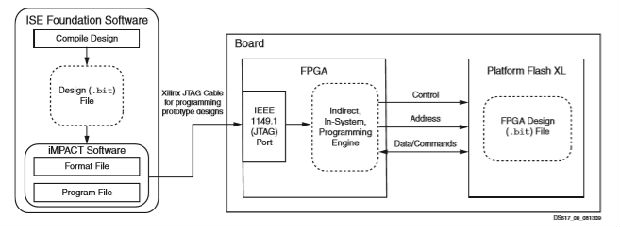

编程概述

平台Flash XL提供满足每个产品阶段要求的编程解决方案。ISE软件为原型环境下的现场可编程门阵列设计工程师提供集成编程支持。第三方编程支持也可用于制造环境的需求。

面向原型FPGA设计的冲击编程解决方案

Xilinx-ISE软件对系统内编程提供了完整的支持,能够为原型FPGA设计快速开发程序和测试周期。软件可以将FPGA设计编译成配置位流,并通过Xilinx JTAG电缆将位流编程成系统中的平台Flash XL。

ISE软件套件中的iMPACT软件工具将FPGA用户设计位流格式化为闪存图像文件,并通过Xilinx JTAG电缆连接到FPGA的JTAG端口对设备进行编程。对于编程过程,iMPACT软件首先将包含系统内编程引擎的预构建比特流下载到FPGA中。然后,iMPACT软件通过在FPGA中下载的系统内编程引擎,将FPGA用户设计的比特流间接编程到平台Flash XL中。

注:为了在系统编程中间接支持iMPACT软件,需要在FPGA和平台Flash XL之间建立一组特定的连接。见UG438,平台闪光灯XL

配置和存储设备用户指南,推荐

连接。iMPACT只支持读取和写入主内存数组。iMPACT不支持读取或写入特殊数据寄存器,例如电子签名码、保护寄存器或OTP寄存器。

生产计划解决方案

针对制造环境的要求,针对flash编程平台存在多种解决方案。通用生产编程平台提供编程支持。

Flash XL平台的集成FPGA设计及系统内编程解决方案

设备程序员要求阵列数据以标准PROM格式的数据文件的形式存在,例如MCS。位文件不是第三方设备程序员的有效数据输入格式。有关准备编程文件的说明,请参阅。平台Flash XL配置和存储设备用户指南

公共汽车运行

控制设备的标准总线操作有六种:总线读取、总线写入、地址锁存、输出禁用、待机和复位。

总线读取

总线读取操作用于输出

存储阵列、电子签名、状态寄存器和通用闪存接口。为了执行读取操作,芯片启用和输出启用都必须为V。应使用芯片启用输入启用设备。应使用“输出启用”将数据选通到输出。读取的数据取决于之前写入内存的命令(见第14页的“命令界面”)。伊利诺伊州

总线写入

总线写入操作将命令写入要编程的存储器或锁存器输入数据。当芯片使能和写入使能在V时启动总线写入操作,输出使能在V时启动。命令、输入数据和地址锁定在写入使能或芯片使能的上升沿上,以先发生的为准。通过切换锁存启用(当芯片启用为V时),可以在写入操作之前锁存地址。伊利诺伊州IH公司伊利诺伊州

系统也可以将锁存启用信号保持在V,但是系统必须保证地址线至少在T内保持稳定。伊利诺伊州码头

注:通常,小于5ns片上启用或写启用的故障会被内存忽略,不会影响总线写入操作。

地址锁存器

地址锁存操作输入有效地址。在地址锁存操作期间,芯片启用和锁存启用都必须为V。地址锁定在锁存启用的上升沿上。伊利诺伊州

输出禁用

当输出使能为V时,输出保持在高阻抗。

备用物品

待机使大多数内部电路失效,从而大大降低了电流消耗。当芯片使能和复位为V时,存储器处于待机状态。功耗降低到待机水平I,输出设置为高阻抗,独立于输出使能或写入使能。如果芯片启用在程序或擦除操作期间切换到V,则设备在完成程序或擦除操作时进入待机模式。

读取数组命令

Read Array命令返回地址行到Read Array模式。发出Read Array命令需要一个总线写入周期。在一个库处于读数组模式之后,后续的读操作从内存数组输出数据。

在另一个库中编程或擦除时,可以向任何库发出读取数组命令。如果向当前执行程序或擦除操作的银行发出读取阵列命令,银行将返回读取阵列模式,但程序或擦除操作将继续;但是,在程序或擦除操作完成之前,银行的数据输出将无法得到保证。其他银行的读取模式不受影响。

读取状态寄存器命令

设备包含一个状态寄存器,用于监视程序或擦除操作。

读取状态寄存器命令用于读取地址银行的状态寄存器的内容。发出读取状态寄存器命令需要一个总线写入周期。在银行处于读取状态寄存器模式后,后续的读取操作将输出状态寄存器的内容。

状态寄存器数据锁定在

芯片启用或输出启用。必须切换芯片启用或输出启用以更新状态寄存器数据。

读取状态寄存器命令可以随时发出,即使在程序或擦除操作期间。Read Status Register命令只改变地址银行的读取模式。其他银行的读取模式不受影响。只能使用异步读取和单同步读取操作来读取状态寄存器。

需要一个Read Array命令才能使银行返回到Read Array模式。

读取电子签名命令

读取电子签名命令用于读取制造商和设备代码、地址银行的锁定状态、保护寄存器和配置寄存器。需要一个总线写入周期来发出读取

电子签名命令。在银行处于读取电子签名模式后,同一银行的后续读取操作将输出制造商代码、设备代码、寻址银行的锁定状态、保护寄存器或配置寄存器(见第22页表10)。

读取电子签名命令可以在任何时候发出,即使在程序或擦除操作期间,除了在保护寄存器程序操作期间。不允许参数组和电子签名位置之间的双重操作(详见第36页表17)。

如果向执行程序或擦除操作的银行发出读取电子签名命令,则银行进入读取电子签名模式。随后的总线读取周期输出电子签名数据,并且程序/擦除控制器继续在后台编程或擦除。

Read Electronic Signature命令只改变地址银行的读取模式。其他银行的读取模式不受影响。只能使用异步读取和单同步读取操作来读取电子签名。需要一个Read Array命令才能使银行返回到Read Array模式。

读取CFI查询命令

Read CFI Query命令用于从公共闪存接口(CFI)读取数据。发出Read CFI查询命令需要一个总线写入周期。当一个银行处于Read CFI查询模式后,同一银行的后续总线读取操作从公共闪存接口读取。Read CFI Query命令可以在任何时候发出,即使是在程序或擦除操作期间。

如果向执行程序或擦除操作的银行发出Read CFI查询命令,银行将进入Read CFI查询模式。随后的总线读取周期输出CFI数据,并且程序/擦除控制器继续在后台编程或擦除。

Read CFI Query命令只改变地址银行的读取模式。其他银行的读取模式不受影响。只能使用异步读取和单同步读取操作来读取CFI。需要一个Read Array命令才能使银行返回到Read Array模式。不允许在参数组和CFI内存空间之间进行双重操作。

清除状态寄存器命令

清除状态寄存器命令可用于重置

(设置为“0”)状态中的所有错误位(SR1、3、4和5)

登记。发出清除状态寄存器命令需要一个总线写入周期。清除状态寄存器命令不影响银行的读取模式。

发出新命令时,状态寄存器中的错误位不会自动返回到“0”。在尝试新程序或擦除命令之前,应清除状态寄存器中的错误位。

块擦除命令

块擦除命令用于擦除块。它将选定块中的所有位设置为“1”。块中以前的所有数据都将丢失。

如果块受到保护,则擦除操作中止,块中的数据不会更改,状态寄存器输出错误。

发出该命令需要两个总线写入周期。

第一个总线周期设置块擦除命令。

第二个锁存块地址并启动程序/擦除控制器。

如果第二个总线周期不是块擦除确认码,则设置状态寄存器位SR4和SR5,并中止该命令。

发出命令后,银行进入读取状态寄存器模式,地址银行内的任何读取操作都输出状态寄存器的内容。需要一个Read Array命令才能使银行返回到Read Array模式。

在块擦除操作期间,包含要擦除的块的库只接受读取数组、读取状态寄存器、读取电子签名、读取CFI查询和程序/擦除挂起命令;所有其他命令都将被忽略。

如果重置(RP)变为V,则块擦除操作中止。由于块擦除操作中止时无法保证数据完整性,因此必须再次擦除块。伊利诺伊州

空白检查命令

Blank Check命令用于检查块是否已完全擦除。一次只能检查一个街区。要使用空白检查命令,V必须等于V。如果V不等于V,设备将忽略该命令,并且状态寄存器中不会显示错误。聚丙烯PPH公司聚丙烯PPH公司

发出空白检查命令需要两个总线周期:

第一个总线周期将空白检查命令(BCh)写入要检查的块中的任何地址。第二个总线周期将空白检查确认命令(CBh)写入要检查的块中的任何地址,并启动空白检查操作。

如果第二个总线周期不是空白检查确认,则状态寄存器位SR4和SR5被设置为“1”,命令中止。

发出命令后,地址银行自动进入状态登记模式,并在银行内进一步读取状态登记内容。

空白检查期间允许的唯一操作是读取

状态寄存器。进行空检查操作时不支持双重操作。当设备处于程序/擦除挂起状态时,不能挂起和不允许空白检查操作。

SR7状态寄存器位表示正在进行的空白检查操作的状态:

SR7='0'表示空白检查操作仍在进行中。

SR7='1'表示操作已完成。

SR5状态寄存器位变高(SR5='1'),表示空白检查操作失败。

在操作结束时,存储组保持在读取状态寄存器模式,直到另一个命令写入命令接口。

程序命令

program命令用于将单个单词编程到内存数组。如果正在编程的块受到保护,则程序操作中止,块中的数据不改变,状态寄存器输出错误。

发出程序需要两个总线写入周期

命令。

第一个总线周期设置程序命令。第二个锁存要编程的地址和数据,并启动程序/擦除控制器。

编程开始后,被编程银行的读取操作输出状态寄存器内容。

在程序操作期间,包含被编程单词的库只接受读数组、读状态寄存器、读电子签名、读CFI查询和程序/擦除暂停命令;所有其他命令都被忽略。需要一个Read Array命令才能使银行返回到Read Array模式。

如果复位(RP)变为V,则程序操作中止。由于程序操作中止时无法保证数据完整性,因此必须重新编程。伊利诺伊州

缓冲程序命令

Buffer Program命令使用设备的32字写缓冲区来加快编程速度。最多可以将32个字加载到写缓冲区中。与标准的非缓冲程序命令相比,缓冲程序命令大大缩短了系统编程时间。

发出缓冲程序命令需要四个连续步骤:

1. 第一个总线写入周期设置缓冲区程序命令。设置代码可以寻址到目标块中的任何位置。

在第一个总线写入周期之后,读取操作将输出状态寄存器的内容。应读取状态寄存器位SR7,以检查缓冲区是否可用(SR7=1)。如果缓冲区不可用(SR7=0),则必须重新发出缓冲区程序命令以更新状态寄存器内容。

2. 第二个总线写入周期设置要编程的字数。值n写入相同的块地址,其中n+1是要编程的字数。

3. 总共n+1个总线写入周期用于将每个字的地址和数据加载到写入缓冲区中。地址必须在起始地址到起始地址+n的范围内,起始地址是要编程的第一个数据的位置。当起始地址对应于32个字的边界时,可获得最佳性能。

4. 最后的总线写入周期确认缓冲区程序命令并启动程序操作。

缓冲区程序操作中使用的所有地址必须位于同一块中。无效的地址组合或未能遵循正确的总线写入周期顺序将在状态寄存器中设置错误并在不影响内存数组中的数据的情况下中止操作。

如果正在编程的块受到保护,则在状态寄存器中设置一个错误,并且在不影响存储器阵列中的数据的情况下中止操作。

在缓冲程序操作期间,被编程的银行只接受读取数组、读取状态寄存器、读取电子签名、读取CFI查询和程序/擦除挂起命令;所有其他命令均被忽略。

缓冲区增强的工厂程序命令

缓冲区增强型工厂程序命令是专门开发的,用于在编程时间非常关键的制造环境中加速编程。该命令用于对块编程一个或多个32字的写缓冲区。在设备进入缓冲区增强的工厂程序模式后,只要地址保持在同一块内,写缓冲区就可以重新加载任意次数。一次只能编程一个块。

如果正在编程的块受到保护,则程序操作中止,块中的数据不改变,状态寄存器输出错误。

使用Buffer Enhanced Factory Program命令需要特定的操作条件:

V必须设置为V。聚丙烯PPH公司

V必须在工作范围内。尽职调查

环境温度T必须为30°C±10°C。一个

目标块必须解锁。

起始地址必须与32字缓冲区边界的起始地址对齐。•在整个编程过程中,地址必须保持为起始地址。

在缓冲区增强的工厂程序操作期间不支持双重操作,并且无法挂起该命令。

缓冲区增强的工厂程序命令包括三个阶段:设置、程序和验证,以及退出。

安装阶段

Buffer Enhanced Factory Program命令需要两个总线写入周期来启动该命令:第一个总线写入周期设置Buffer Enhanced Factory Program命令。

第二个总线写入周期确认该命令。

发出confirm命令后,读取操作输出状态寄存器的内容。

注意安全不能发出读取状态寄存器命令,因为它被解释为要编程的数据。

状态寄存器程序/擦除控制器(P/E.C)。应读取SR7位,以检查P/E.C.是否准备好进入下一阶段。

如果检测到错误,SR4将变高(设置为“1”),并且

程序和验证阶段

程序和验证阶段需要32个周期将32个字编程到写缓冲区。数据按顺序存储,从写缓冲区的第一个地址开始,直到写缓冲区满为止(32个字)。若要编程少于32个字,则应使用FFFFh编程剩余的字。

发出和执行程序以及验证命令阶段需要四个连续步骤。

1. 一个总线写入操作用于锁定起始地址和要编程的第一个字。应读取状态寄存器Bank Write Status位SR0,以检查P/E.C.是否准备好进入下一个字。

2. 随后要编程的每个字都用一个新的总线写入操作锁定。当P/E.C.递增地址位置时,地址必须保持起始地址。如果给定的地址与起始地址不在同一块中,则程序和验证阶段终止。应在每个总线写入周期之间读取状态寄存器位SR0,以检查P/E.C.是否为下一个字做好准备。

3. 写入缓冲区满后,数据按顺序编程到内存阵列。程序运行后,设备自动验证数据,必要时重新编程。

只要地址保持在同一块中,程序和验证阶段就可以重复,而无需重新发出命令来编程额外的32个字的位置。

4. 最后,在对所有字或整个块进行编程之后,必须将一个总线写操作写入包含起始地址的块之外的任何地址,以终止程序并验证阶段。

必须检查状态寄存器位SR0,以确定程序操作是否完成。状态寄存器可以随时检查错误,但必须在整个程序块编程后检查。

退出阶段

状态寄存器P/E.C位SR7设置为“1”,当设备退出缓冲器增强的工厂程序操作并返回到读状态寄存器模式时。应进行完整状态寄存器检查,以确保块已成功编程。详见第23页的“状态寄存器”。

为了获得最佳性能,缓冲增强型工厂

程序命令应该限制在每个块最多100个程序/擦除周期。如果超过此限制,内部算法将继续正常工作,但可能会导致性能下降。典型程序时间见第44页表21。

有关使用Buffer Enhanced Factory程序命令的建议流程图,请参见第79页图45。

程序/擦除挂起命令

Program/Erase Suspend命令用于暂停程序或块擦除操作。这个命令可以发到任何银行。

重新启动挂起的操作需要“程序/擦除恢复”命令。发出“程序/擦除挂起”命令需要一个总线写入周期。程序/擦除控制器暂停后,状态寄存器的位SR7、SR6和/或SR2被设置为“1”。

在程序/擦除挂起期间接受以下命令:

程序/擦除恢复

读取数组(来自擦除挂起块或程序挂起字的数据无效)

读取状态寄存器

此外,如果挂起的操作是块擦除,则也接受以下命令:

清除状态寄存器

程序(擦除挂起块除外)

缓冲程序(擦除挂起块除外)

封锁解锁

设置配置寄存器

在擦除挂起期间,可以通过发出块锁定或块锁定命令来保护要擦除的块。当发出程序/擦除恢复命令时,操作完成。

可以累积多个挂起操作。例如,挂起擦除操作,启动程序操作,挂起程序操作,然后读取数组。

如果在块擦除挂起期间发出程序命令,则在程序操作完成之前,无法恢复擦除操作。

Program/Erase Suspend命令不会更改列组的读取模式。如果挂起的银行处于读取状态寄存器、读取电子签名或读取CFI查询模式,则该银行将保持该模式并输出相应的数据。

有关程序/擦除挂起期间允许同时操作的详细信息,请参阅第35页的“双操作和多银行体系结构”。

在程序/擦除挂起期间,通过将芯片启用设置为V,可以将设备置于待机模式。IH公司

如果复位(RP)转到V,则程序/擦除中止。伊利诺伊州

程序/擦除恢复命令

Program/Erase Resume命令用于重新启动由Program/Erase Suspend命令挂起的程序或擦除操作。发出命令需要一个总线写入周期,可以发送到任何地址。

Program/Erase Resume(程序/擦除恢复)命令不会更改列组的读取模式。如果挂起的银行处于读取状态寄存器、读取电子签名或读取CFI查询模式,则该银行将保持该模式并输出相应的数据。

如果在块擦除挂起期间发出程序命令,则在程序操作完成之前无法恢复擦除。

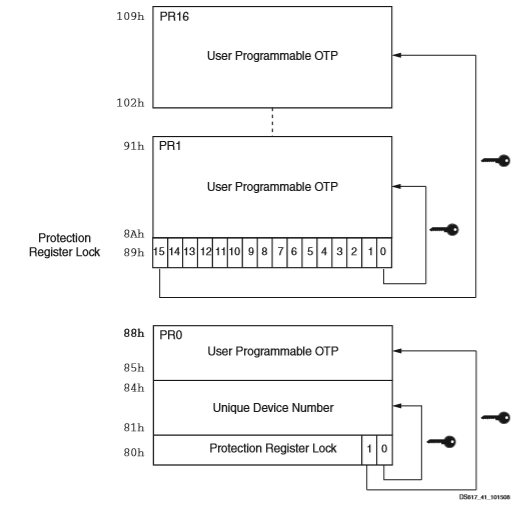

保护寄存器程序命令

保护寄存器程序命令用于对保护寄存器和两个保护寄存器锁的用户一次性可编程(OTP)段进行编程。

该设备具有16个128位的OTP段和一个64位的OTP段。这些片段一次编程一个单词。发送时,段中的所有位都设置为“1”。用户只能将位编程为“0”。

发出保护寄存器程序命令需要两个总线写入周期:

第一个总线周期设置保护寄存器程序命令。

第二个锁存要编程到保护寄存器的地址和数据,并启动程序/擦除控制器。

对正在编程的银行的读取操作在程序操作开始后输出状态寄存器内容。试图对以前受保护的保护寄存器进行编程会导致状态寄存器错误。

无法挂起保护寄存器程序。不允许在参数组和保护寄存器内存空间之间进行双重操作。

设置配置寄存器命令

Set Configuration Register命令用于将新值写入配置寄存器。发出Set配置寄存器命令需要两个总线写入周期:

第一个循环设置设置配置寄存器命令和与配置寄存器内容相对应的地址。第二个循环写入配置寄存器数据和确认命令。

在总线写入周期中,配置寄存器数据必须作为地址写入,即A0=CR0,A1=CR1,…,A15=CR15。地址A16–A22是

忽略。读取操作在发出Set Configuration Register命令后输出数组内容。

读取电子签名命令用于读取配置寄存器的更新内容。

块锁定命令

Block Lock命令用于锁定块并防止程序或擦除操作更改内容。通电或重置后,所有块都被锁定。

发出块锁定命令需要两个总线写入周期:

第一个总线周期设置块锁定命令。

第二个总线写入周期锁定块地址并锁定块。

可以使用Read Electronic Signature命令监视每个块的锁状态。第38页表18显示了发出Block Lock命令后的锁定状态。

设置后,块锁定位即使在硬件复位或断电/通电后仍保持设置。它们由块解锁命令清除。

块解锁命令

块解锁命令用于解锁块,允许对块进行编程或擦除。

发出块解锁命令需要两个总线写入周期:

第一个总线周期设置块解锁命令。

第二个总线写入周期锁定块地址并解锁块。

可以使用Read Electronic Signature命令监视每个块的锁状态。第38页表18显示了发出块解锁命令后的保护状态。

有关详细说明,请参阅第37页的“块锁定”,有关使用块解锁命令的流程图,请参阅第77页的图43。

块锁定命令

块锁定命令用于锁定已锁定或未锁定的块。

锁定块无法编程或擦除。锁定块的锁定状态在以下情况下无法更改

WP低(在V下)。当WP为高(V)时,锁定功能被禁用,锁定的块可以通过块解锁命令单独解锁。伊利诺伊州IH公司

发出块锁定命令需要两个总线写入周期:

第一个总线周期设置块锁定命令。

第二个总线写入周期锁定块地址并锁定块。

可以使用Read Electronic Signature命令监视每个块的锁状态。

当设备在断电时重置时,锁定块将恢复为锁定(而不是锁定)状态。表18显示了发出块锁定命令后的锁定状态。

笔记:

一。iMPACT软件不支持读取或写入保护寄存器锁、OTP字段或唯一设备号。

保护寄存器内存映射

状态寄存器

状态寄存器提供当前或以前程序或擦除操作的信息。发出读取状态寄存器命令以读取状态寄存器的内容,有关详细信息,请参阅第14页的“读取状态寄存器命令”。为了输出内容,状态寄存器被锁存并在芯片使能或输出使能信号的下降沿上更新,并且可以被读取,直到芯片使能或输出使能返回到V。IH公司

只能使用单个异步或同步读取来读取状态寄存器。从银行内任何地址的总线读取操作始终在程序期间读取状态寄存器,如果未发出读取阵列命令,则执行擦除操作。

状态寄存器位

各种位传送关于操作的状态和任何错误的信息。位SR7、SR6、SR2和SR0提供有关设备状态的信息,并由设备设置和重置。位SR5、SR4、SR3和SR1给出错误信息,由设备设置,但必须通过发出清除状态寄存器命令或硬件重置来重置。

如果错误位设置为“1”,则应在发出另一个命令之前重置状态寄存器。

程序/擦除控制器状态位(SR7)程序/擦除控制器在任何气缸组中处于活动或非活动状态。当该位低(设置为“0”)时,程序/擦除程序/擦除控制器状态位指示

结了状态寄存器中的位。

控制器处于活动状态;当位高(设置为“1”)时,控制器处于非活动状态,设备准备好处理新命令。

发出程序/擦除挂起命令后,程序/擦除控制器状态位立即变低,直到控制器暂停。程序/擦除控制器暂停后,位为高位。

擦除挂起状态位(SR6)

擦除挂起状态位表示擦除操作已挂起。当该位为高位(设置为“1”)时,发出程序/擦除挂起命令,内存正在等待程序/擦除恢复命令。

擦除挂起状态位应仅在程序/擦除控制器状态位高(程序/擦除控制器不活动)时才被视为有效。SR6设置在

正在发出的程序/擦除挂起命令的擦除挂起延迟时间;因此,内存仍然可以完成操作,而不是进入挂起模式。

当发出程序/擦除恢复命令时,擦除暂停状态位返回低位。

擦除/空白检查状态位(SR5)

擦除/空白检查状态位用于识别块擦除操作期间是否发生错误。当该位为高(设置为‘1’)时,程序/擦除控制器将最大脉冲数应用于块,仍然未能验证它是否正确擦除。

应在程序/擦除控制器状态位高(程序/擦除控制器未激活)后读取擦除/空白检查状态位。

擦除/空白检查状态位还用于指示空白检查操作期间是否发生错误。如果发出空白检查命令的块中一个或多个位置的数据与FFFFh不同,则SR5设置为“1”。

设置为高后,在发出新的擦除命令之前,必须通过清除状态寄存器命令或硬件重置将擦除/空白检查状态位设置为低;否则,新命令将失败。

程序状态位(SR4)

程序状态位用于识别程序操作期间是否有错误。该位应在程序/擦除控制器状态位高(程序/擦除控制器未激活)后读取。

当程序状态位高(设置为‘1’)时,程序/擦除控制器将最大脉冲数应用到Word,仍然无法验证它是否正确编程。

试图将“1”编程为已经编程的位,同时V=V也将程序状态位设置为高。如果V与V不同,则SR4保持低位(设置为“0”),并且不显示尝试。聚丙烯PPH公司聚丙烯PPH公司

设置高后,在发出新程序命令之前,必须通过清除状态寄存器命令或硬件重置将程序状态位设置低;否则,新命令将失败。

VPP状态位(SR3)

V状态位用于在编程和擦除操作期间识别V引脚上的无效电压。V引脚仅在程序或擦除操作开始时采样。如果在操作过程中V变为无效,则不保证程序和擦除操作。聚丙烯聚丙烯聚丙烯聚丙烯

当V状态位为低(设置为“0”)时,在有效电压下对V引脚上的电压进行采样。聚丙烯聚丙烯

当V状态位为高(设置为“1”)时,V引脚的电压低于V锁定电压(V)。内存受到保护,无法执行程序和擦除操作。聚丙烯聚丙烯聚丙烯PPLK公司

设置高后,在发出新程序或擦除命令之前,必须通过清除状态寄存器命令或硬件重置将V状态位设置低;否则,新命令将失败。聚丙烯

程序挂起状态位(SR2)

程序挂起状态位表示程序操作挂起。只有当程序/擦除控制器状态位高(程序/擦除控制器不活动)时,才应认为该位有效。

当程序挂起状态位为高(设置为“1”)时,发出程序/擦除挂起命令,内存正在等待程序/擦除恢复命令。

SR2是在发出Program/Erase Suspend命令的Program Suspend延迟时间内设置的;因此,内存仍然可以完成操作,而不是进入Suspend模式。

当发出程序/擦除恢复命令时,程序挂起状态位返回低位。

块保护状态位(SR1)

块保护状态位用于识别程序或块擦除操作是否试图修改锁定或锁定块的内容。当此位为高(设置为“1”)时,试图对锁定或锁定的块执行程序或擦除操作。

设置为高后,在发出新程序或擦除命令之前,必须通过清除状态寄存器命令或硬件重置将块保护状态位设置为低;否则,新命令似乎失败。

银行写入/多字程序状态位(SR0)

Bank Write Status位指示地址银行是正忙于执行写操作,还是准备接受新的写命令(程序或擦除命令)。在缓冲增强工厂程序模式下,多字程序位显示设备是否准备好接受要编程到存储器阵列的新字。

只有当程序/擦除控制器状态SR7低时,才应认为银行写入状态位有效(设置为“0”)。

当程序/擦除控制器状态位和列组写入状态位都低(设置为“0”)时,寻址列组正在执行程序或擦除操作。当程序/擦除控制器状态位为低(设置为“0”)且列组写入状态位为高(设置为“1”)时,程序或擦除操作正在被寻址的列组中执行。

在缓冲区增强的工厂程序模式下,如果多字程序状态位低(设置为“0”),则设备已准备好下一个字;如果多字程序状态位高(设置为“1”),则设备未准备好下一个字。

有关如何使用状态寄存器的更多详细信息,请参阅第71页“附录C:流程图和伪代码”中提供的流程图和伪代码。

配置寄存器

配置寄存器用于配置内存执行的总线访问类型。有关读取操作的详细信息,请参阅第34页的“读取模式”。

使用set Configuration Register命令通过命令接口设置配置寄存器。复位或通电后,设备配置为同步读取(CR15=0)。配置寄存器位指定突发长度、突发类型、突发X延迟和读取操作的选择。