840点击型号即可查看芯片规格书

VirtexII功能概述,业界第一平台的FPGA解决方案,IP Immersion体系结构-密度从40K到8M系统门-420 MHz内部时钟速度(高级数据)-840+Mb/s I/O(高级数据)SelectRAM™内存层次结构-3 Mb真正的双端口™RAM在18 KB块SelectRAM资源-高达1.5 Mb分布式SelectRAM资源-高性能接口到外部存储器DDR-SLDM接口·FCRAM接口QDR∑- SRAM接口Sigma RAM接口算术功能专用18位X 18位乘法器块快速前瞻进位逻辑链灵活的逻辑资源-高达93184个内部寄存器/锁存器,时钟启用-高达93,184查找表(LUT)或16位移位寄存器-宽的多路复用器和广泛的输入功能支持-水平级联链和产品支持-内部三态的高性能时钟管理电路-高达12 DCM(数字时钟管理器)模块*精确时钟歪斜*灵活的频率合成。·高分辨率相移-16个全局时钟多路复用器缓冲区,主动互联技术-第四代分段路由结构-可预测、快速路由延迟,独立于扇出,SelectI/O-Ultra技术-最多1,108个用户I/O-19个单端标准和6个差分标准-每个I/O的可编程接收器电流(2毫安到24毫安)

-数字控制阻抗(DCI)I/O:单端I/O标准的片上终端电阻器-PCI-X@133 MHz,PCI@66 MHz和33 MHz,和CardBus兼容-差分信号·840 Mb/s低电压差分信号输入/输出(LVDS),带电流模式驱动器·总线LVDS I/O·闪电数据传输(LDT)I/O电流驱动器缓冲区·低压正射极耦合逻辑(LVPECL)I/O·内置DDR输入和输出寄存器-专有高性能SelectLink技术·高带宽数据路径·双数据速率(DDR)链路·基于Web的HDL生成方法学•由Xilinx Foundation和Alliance™系列支持开发系统-集成VHDL和Verilog设计流程-汇编10M系统门设计-Internet团队设计(ITD)工具,基于系统配置的SRAM-Fast SelectMAP™配置-三重数据加密标准(DES)安全选项(位流加密)-IEEE1532支持-部分重配置-无限制可编程性-读写能力:0.15μm的8层金属工艺,具有0.12μm高速晶体管:1.5 V(VCCNT)核心电源,专用3.3伏VCUAX辅助和VCCO I/O电源:IEEE 1149.1兼容边界扫描逻辑支持:倒装芯片和引线键合球栅阵列(BGA)封装三标准精节距(0.80毫米、1.00毫米和1.27毫米)100%工厂测试

概述Virtex II系列是一种基于IP核和定制模块的高性能平台FPGA,从低密度设计到高密度设计。该系列为电信、无线、网络、视频和数字信号处理器应用提供了完整的解决方案,包括PCI、LVDS和DDR接口。领先的0.15μm/0.12μm CMOS 8层金属工艺和Virtex II结构经过优化,可实现高速、低功耗。结合各种灵活的特征和大范围的密度多达1000万个系统门,ViTEX II系列增强了可编程逻辑设计能力,并且是掩模编程门阵列的有力替代。如表1所示,Virtex II系列由12个成员组成,范围从40K到10M不等。包装产品包括0.80毫米、1.00毫米和1.27毫米间距的球栅阵列(BGA)包装。除了传统的线键互连,倒装芯片互连也被用于一些BGA产品中。倒装芯片互连的使用提供了比类似封装的线键版本更多的I/O。倒装芯片结构提供了高引脚数和高热容量的结合

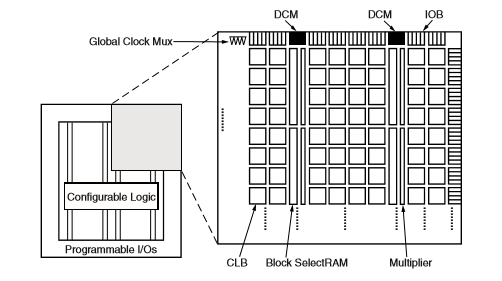

架构Virtex II阵列概述Virtex II设备是具有各种可配置元素的用户可编程门阵列。Virtex II架构针对高密度和高性能逻辑设计进行了优化。可编程设备由输入/输出块(IOB)和内部可配置逻辑块(CLB)组成。

可编程I/O块提供封装引脚和内部可配置逻辑之间的接口。最流行和最前沿的I/O标准由可编程的IOB支持。内部可配置逻辑包括四个主要元素,它们组织在一个规则数组中。可配置逻辑块(CLB)为组合逻辑和同步逻辑提供功能元件,包括基本存储元件。与每个CLB元素关联的BUFTs(3状态缓冲区)驱动专用的可分段水平路由资源。块选择RAM内存模块提供真正双端口RAM的18 Kbit大存储单元。乘法器块是18位x 18位专用乘法器。DCM(数字时钟管理器)模块为时钟分布延迟补偿、时钟乘法和除法、粗粒度和细粒度时钟相移提供自校准、全数字解决方案。新一代的可编程路由资源称为主动互连技术,它将所有这些元素互连起来。通用路由矩阵(GRM)是一组路由交换机。每个可编程元件都绑定到一个交换机矩阵,允许多个连接到通用路由矩阵。整个可编程互连是分层的,设计用于支持高速设计。

所有可编程元件,包括路由资源,都由存储在静态存储单元中的值控制。这些值在配置期间加载到存储单元中,并且可以重新加载以更改可编程元件的功能。Virtex II特性本节简要介绍Virtex II特性。输入/输出块(IOB)IOB是可编程的,可分为以下几类:具有可选的单数据速率或双数据速率(DDR)寄存器的输入块具有可选的单数据速率或DDR寄存器的输出块,以及可选的3状态缓冲器,要直接或通过单个或DDR寄存器驱动双向块(输入和输出配置的任意组合),这些寄存器要么是边缘触发D型触发器,要么是电平敏感锁存器。IOB支持以下单端I/O标准:LVTTL、LVCMOS(3.3 V、2.5 V、1.8 V和1.5 V)133 MHz下的PCI-X、PCI(33 MHz和66 MHz下的3.3 V)GTL和GTLP,HSTL(I、II、III和IV级)

SSTL(3.3 V和2.5 V,I级和II级)AGP-2X数字控制阻抗(DCI)I/O功能自动为每个I/O元件提供芯片端接。IOB元件还支持以下差分信号输入/输出标准:LVDS•BLVDS(总线LVDS)ULVDS,LDT,LVPECL每个差分对使用两个相邻的焊盘。两个或四个IOB块连接到一个交换机矩阵以访问路由资源。可配置逻辑块(CLB)CLB资源包括四个片和两个3状态缓冲区。每个部分都是等效的,包含:两个函数生成器(F&G)两个存储元件,算术逻辑门,大型多路复用器,广泛的功能能力,快速进位前瞻链,水平级联链(或门)函数生成器F&G可配置为4输入查找表(LUT),作为16位移位寄存器,或作为16位分布式SelectRAM存储器。此外,这两个存储元件要么是边缘触发D型触发器,要么是电平敏感锁存器。每个CLB都有内部快速互连,并连接到交换机矩阵以访问常规路由资源。Block SelectRAM内存Block SelectRAM内存资源是18kb的真正双端口RAM,可编程范围从16kx1位到512x 36位,具有不同的深度和宽度配置。每个端口都是完全同步和独立的,提供三种“读写”模式。块选择内存是可级联的,可以实现大型的嵌入式存储块。双端口和单端口模式支持的内存配置如表3所示。

乘法器块与每个SelectRAM内存块相关联。乘法器块是一个专用的18 x 18位乘法器,并根据一个端口上的块SelectRAM内容为操作优化。18x 18乘法器可以独立于块SelectRAM资源使用。读/乘/累加操作和DSP滤波器结构非常有效。SelectRAM存储器和乘法器资源都连接到四个交换矩阵以访问常规路由资源。全局时钟DCM和全局时钟复用器缓冲区为设计高速时钟方案提供了一个完整的解决方案。最多可提供12个DCM块。为了产生反歪斜的内部或外部时钟,每个DCM可用于消除时钟分布延迟。DCM还提供90度、180度和270度相移版本的输出时钟。细粒度相移以时钟周期的1/256为增量提供高分辨率相位调整。非常灵活的频率合成提供了一个等于输入时钟频率的任何M/D比的时钟输出频率,其中M和D是两个整数。有关精确的计时参数,请参阅Virtex-II电气特性。Virtex II设备有16个全局时钟MUX缓冲区,每个象限最多有8个时钟网络。每个全局时钟MUX缓冲器可以选择两个时钟输入中的一个,并在一个时钟到另一个时钟之间无故障切换。每个DCM块最多可以驱动16个全局时钟MUX缓冲区中的4个。路由资源IOB、CLB、block SelectRAM、multiplier和DCM元素都使用相同的互连方案和对全局路由矩阵的相同访问。共享时序模型,大大提高了高速设计性能的可预测性。总共有16条全球时钟线,每个象限有8条此外,每行或每列24条垂直和水平长线以及大量的辅助和本地路由资源提供了快速互连。Virtex II缓冲互连相对不受网络扇出的影响,互连布局的设计是为了最小化串扰。每行或每列的水平和垂直布线资源包括:24条长线,120条六角线,40条双线,16条直接连接线(共四个方向)

边界扫描边界扫描指令和相关的数据寄存器支持访问和配置符合IEEE标准1149.1-1993和1532的Virtex II设备的标准方法。实现了系统模式和测试模式。在系统模式下,Virtex II设备即使在执行非测试边界扫描指令时也执行其预期任务。在测试模式下,边界扫描测试指令控制I/O引脚进行测试。Virtex II测试访问端口(TAP)支持BYPASS、PRELOAD、SAMPLE、IDCODE和USERCODE非测试指令。也支持EXTEST、INTEST和HIGHZ测试指令。配置Virtex II设备是通过将数据加载到内部配置内存中来配置的,使用以下五种模式:从串行模式,主串行模式,从选择映射模式,主选择映射模式,边界扫描模式(IEEE1532)芯片上有一个数据加密标准(DES)解密器,用于保护比特流。可以使用一个或两个三重DES密钥集选择性地加密配置信息。

回读和集成逻辑分析仪配置数据存储在Virtex II配置内存中,可回读验证。除了配置数据之外,还可以读取所有触发器/锁存器、分布式SelectRAM和块SelectRAM内存资源的内容。此功能对于实时调试非常有用。集成逻辑分析仪(ILA)核心和软件为访问和验证Virtex II设备提供了完整的解决方案。VIETEX II器件/封装组合和最大的I/O线键合和倒装芯片封装是可用的。表4和表5分别显示了引线键合和倒装芯片封装中最大可能的用户I/OS数量。表6显示了所有设备/包组合的可用用户I/O数。CS表示线键芯片级球栅阵列(BGA)(0.80 mm间距)。FG表示线键细间距BGA(1.00 mm间距)。FF表示倒装芯片细间距BGA(1.00 mm间距)。BG表示标准BGA(1.27 mm节距)。BF表示倒装芯片BGA(1.27 mm间距)。每个包的I/O数包括所有用户I/O,但15个控制管脚(CCLK、DONE、M0、M1、M2、PROG B、PWRDWN B、TCK、TDI、TDO、TMS、HSWAP EN、DXN、DXP和RSVD)和VBATT除外。