特征

在所有引脚上的7.5 ns针对引脚逻辑延迟.F CNT到125 MHz 72个宏单元,具有1600个可用门。最多72个用户I/O引脚。系统可编程(ISP)中的5伏。10000个程序/擦除周期的耐久性。在整个商用电压和温度范围上编程/擦除:增强的PIN锁定结构。灵活36V18功能块-90产品术语驱动功能块内18个宏单元的任意或全部-全局和产品术语时钟,输出启用,设置和重置信号,广泛的IEEE Std 1149.1边界扫描(JTAG)支持

每个宏单元中的可编程功率降低模式,单个输出的旋转速率控制,用户可编程接地引脚功能,用于设计保护的扩展模式安全功能,高驱动24毫安输出,3.3伏或5伏输入/输出功能,先进的CMOS 5V快速闪存技术,同时支持多个XC9500的并行编程,提供44针PLCC、84针PLCC、100针PQFP和100针TQFP封装

说明

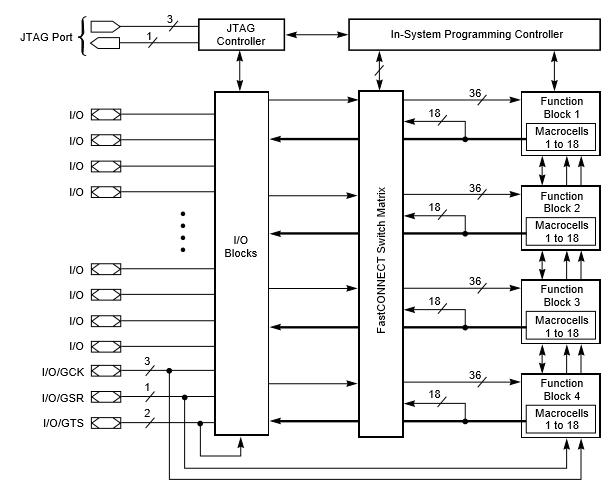

XC9572是一种高性能的CPLD,为通用逻辑集成提供了先进的系统编程和测试能力。它由四个36V18功能块组成,提供1600个可用的门,传播延迟为7.5ns。

电源管理

通过将宏单元配置为标准或低功耗操作模式,可以降低XC9572的功耗。关闭未使用的宏单元以最小化功耗。

每种设计的工作电流可以用以下方程近似于特定的工作条件:ICC(MA)=MCHP(1.7)+MCLP(0.9)+MC(0.006毫安/兆赫)f:

MCHP=高性能模式下的宏单元MCLP=低功耗模式下的宏单元MC=使用的宏单元总数

f=时钟频率(MHz)

显示了XC9572设备的典型计算。

XC9572体系结构

注:功能块输出(黑线表示)直接驱动I/O块