W9825G6EH点击型号即可查看芯片规格书

W9825G6EH是一种高速同步动态随机存取存储器(SDRAM),结构为4M字×4排×16位。W9825G6EH提供每秒166M字的数据带宽(-6)。为了完全符合个人计算机工业标准,W9825G6EH被分为以下速度等级:-6/-6C和-75。-6符合166MHz/CL3或133MHz/CL2规范。-6C符合166MHz/CL3规范。-75符合133MHz/CL3规范。对SDRAM的访问是面向突发的。当使用活动命令选择行和行时,可以以1、2、4、8或整页的突发长度访问一页中的连续内存位置。在突发操作中,SDRAM内部计数器自动生成列地址。随机列也可以通过在每个时钟周期提供其地址来读取。多银行性质使得内部银行之间的交错隐藏了预充时间。通过具有可编程模式寄存器,系统可以改变突发长度、延迟周期、交织或顺序突发以最大化其性能。W9825G6EH是高性能应用中主存储器的理想选择。

特点

3.3V±0.3V电源,高达166mhz时钟频率,4194304字×4排×16位组织,自刷新模式:标准和低功耗,CAS延迟:2和3,突发长度:1、2、4、8和整页,突发读、单写模式,由LDQM控制字节数据,UDQM,断电模式•自动预充电和受控预充电,8K刷新周期/64 mS,接口:LVTTL,封装在TSOP II 54针中,400 mil-0.80,使用符合RoHS的无铅材料

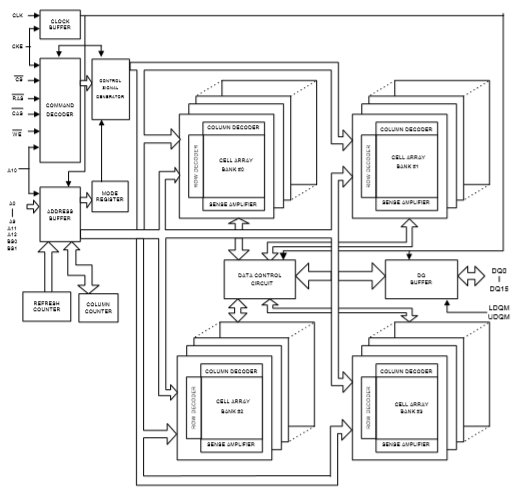

方块图

功能说明

通电和初始化模式寄存器的默认通电状态未指定。需要遵循以下的通电和初始化顺序,以确保设备满足每个特定用户的需求。通电期间,当输入信号保持在“NOP”状态时,所有Vcc和VccQ管脚必须同时上升到指定电压。在任何输入引脚或Vcc电源上,通电电压不得超过Vcc+0.3V。通电后,需要先暂停200秒,然后使用预充电命令对所有气缸组进行预充电。为了防止在通电期间DQ总线上的数据争用,要求在初始暂停期间将DQM和CKE管脚保持在高位。一旦所有的组都被预充电,就必须发出模式寄存器设置命令来初始化模式寄存器。在编程模式寄存器之前或之后,还需要额外的八个自动刷新周期(CBR),以确保正确的后续操作。

编程模式寄存器初始通电后,必须发出模式寄存器设置命令,以便正确操作设备。在发出模式寄存器设置命令之前,所有组必须处于预充电状态,并且CKE必须高至少一个周期。模式寄存器设置命令由处于时钟正边缘的RAS、CAS、CS和WE的低信号激活。此周期内的地址输入数据定义了要设置的参数,如模式寄存器操作表所示。一旦超过等于tRSC的延迟,可以在模式寄存器设置命令之后发出新命令。模式寄存器设置周期及操作表见下页。

银行激活命令在执行任何读或写操作之前,必须应用银行激活命令。该操作类似于EDO DRAM中的RAS activate。从应用Bank Activate命令到第一个读或写操作可以开始的延迟不得小于RAS到CAS的延迟时间(tRCD)。一旦一个银行被激活,它必须在另一个银行激活命令可以发布到同一个银行之前预充电。对同一组的连续组激活命令之间的最小时间间隔由设备的RAS周期时间(tRC)决定。交错银行激活命令(银行A至银行B,反之亦然)之间的最小时间间隔是银行间延迟时间(tRRD)。每个银行可以保持活动状态的最长时间指定为tRAS(max)。

读写访问模式激活银行后,可以遵循读写循环。这是通过在tRCD延迟最小后在时钟上升沿设置RAS高和CAS低来实现的。We pin电压电平定义访问周期是读操作(We高)还是写操作(We低)。地址输入决定起始列地址。读取或写入激活的银行中的其他行需要对银行进行预充电并发出新的银行激活命令。当激活多个银行时,可以进行交叉银行读写操作。利用编程的突发长度,在多个银行之间交替进行存取和预充电操作,可以实现多个不同页面之间的无缝数据存取操作。读或写命令也可以在每个时钟周期向同一组或活动组之间发出。

突发读取命令在时钟上升沿保持RAS和WE高的同时,通过对CS和CAS应用逻辑低电平来启动突发读取命令。地址输入决定突发的起始列地址。模式寄存器在模式寄存器设置周期内设置突发类型(顺序或交织)和突发长度(1、2、4、8和整页)。下一页的表2和表3解释了交织模式和顺序模式的地址序列。

突发写入命令在时钟上升沿保持RAS高电平的同时,通过对CS、CAS和WE应用逻辑低电平来启动突发写入命令。地址输入决定起始列地址。第一个突发写入周期的数据必须应用在发出写入命令的同一时钟周期的DQ管脚上。剩余的数据输入必须在每个后续的上升时钟边缘上提供,直到完成突发长度。在突发结束后提供给DQ管脚的数据将被忽略。7.7读被读中断一个突发读可以被另一个读命令中断。当前一个突发被中断时,剩余的地址将被具有完整突发长度的新读取地址覆盖。来自第一个读取命令的数据继续出现在输出上,直到满足来自中断读取命令的CAS延迟。

读被写中断用写命令中断突发读,可能需要DQM将DQs(输出驱动器)置于高阻抗状态,以避免DQ总线上的数据竞争。如果读命令将在写操作的第一和第二个时钟周期上发出数据,则需要DQM来确保DQs是三态的。之后,Write命令将控制DQ总线,不再需要DQM掩蔽。

由写入中断的写入在由另一个写入命令完成突发写入之前,突发写入可以被中断。当上一个突发被中断时,剩余的地址将被新地址覆盖,数据将写入设备,直到满足编程的突发长度。

由读中断的写-读命令将在读命令激活的同一时钟周期中断突发写操作。在新的读取数据出现在输出上之前,dq必须至少处于高阻抗状态一个周期,以避免数据争用。当Read命令被激活时,来自突发写入周期的任何剩余数据都将被忽略。

突发停止命令可以使用突发停止命令来终止现有的突发操作,但将该库留给将来的读写命令到活动银行的同一页。突发停止命令的定义是:RAS和CAS高,CS低,WE低,位于时钟的上升沿。数据dq在延迟等于由突发停止中断的突发读取周期中的CAS延迟之后进入高阻抗状态。

顺序模式的寻址顺序通过增加输入到设备的列地址来执行列访问。如表2所示,干扰地址随突发长度而变化。

自动预充电命令如果在发出读或写命令时A10设置为高,则进入自动预充电功能。在自动预充电过程中,读取命令将正常执行,但激活的组将在所有突发读取周期完成之前开始自动预充电。无论突发长度如何,它都将在预定突发周期结束之前开始一定数量的时钟。时钟的数量由CAS延迟决定。在整个突发操作完成之前,不能中断具有自动预充电功能的读或写命令。因此,在自动预充电的读或写循环期间,禁止使用读、写或预充电命令。一旦预充电操作开始,在满足预充电时间(tRP)之前,不能重新激活蓄电池组。如果将突发设置为整页长度,则发出Auto pecharge命令是非法的。如果在发出写入命令时A10为高,则启动带自动充电功能的写入。SDRAM从上一个突发写入周期起自动进入预充电操作两个时钟延迟。这种延迟被称为写tWR。在tWR和tRP满足之前,正在进行自动预充电的银行不能重新激活。这被称为tDAL,数据进入活动延迟(tDAL=tWR+tRP)。使用自动预充电命令时,气缸组激活命令和内部预充电操作开始之间的间隔必须满足tRAS(最小值)。

预充电命令预充电命令用于预充电或关闭已激活的蓄电池组。当CS、RAS和WE在时钟上升沿处处于低位和CAS在高位时,进入预充电命令。预充电命令可用于分别或同时对每个气缸组预充电。三个地址位A10、BS0和BS1用于定义发出命令时要预充电的组。发出预充电命令后,必须重新激活预充电的银行,然后才能执行新的读或写访问。预充电命令和激活命令之间的延迟必须大于或等于预充电时间(tRP)。

自刷新命令自刷新命令的定义是:在时钟上升沿,将CS、RAS、CA和CKE保持在低位,WE保持在高位。在发出自刷新命令之前,所有银行都必须处于空闲状态。命令注册后,必须将CKE保持在低位,以使设备保持在自刷新模式。当SDRAM进入自刷新模式时,除CKE外,所有外部控制信号都被禁用。在自刷新操作期间,时钟在内部被禁用以节省电源。在返回高电平后,设备将退出自刷新操作。当设备退出自刷新操作和下一个命令发出之前,需要最小延迟时间。此延迟等于TAC周期时间加上自刷新退出时间。如果在正常操作期间,自动刷新周期在突发(而不是均匀分布)中发出,则8192个自动刷新周期的突发应在进入之前和刚刚退出自刷新模式之后完成。自动刷新命令和下一个命令之间的时间段由tRC指定。

掉电模式保持CKE低启动掉电模式。除CKE外的所有接收器电路都被关闭以降低功率。关机模式不执行任何刷新操作,因此设备在关机模式下的时间不能超过设备的刷新周期(tREF)。通过使CKE高,退出掉电模式。当CKE变高时,根据tCK,下一个上升时钟边缘需要无操作命令。输入缓冲区需要在CKE保持高电平的情况下启用,时间段等于tCK(min)+tCK(min)。

禁止操作命令当SDRAM处于空闲或等待状态时,应使用禁止操作命令,以防止SDRAM在操作之间注册任何不需要的命令。当CS在RAS、CAS中处于低位,并且我们在时钟的上升沿处保持高位时,会注册一个No Operation命令。不操作命令不会终止仍在执行的前一个操作,例如突发读或写循环。

取消选择命令取消选择命令执行与无操作命令相同的功能。取消选择命令发生在CS被调高,RAS,CA和WE信号变得不重要的时候。

时钟暂停模式在正常访问模式下,必须将CKE保持在高位启用时钟。当至少一个银行处于活动状态时,CKE登记为低时,进入时钟暂停模式。时钟挂起模式停用内部时钟,并挂起当前正在执行的任何已计时操作。在注册CKE low和SDRAM操作暂停之间有一个时钟延迟。在时钟暂停模式下,SDRAM会忽略发出的任何新命令。时钟挂起模式通过引入CKE高而退出。有一个时钟周期延迟时,当CKE返回到时钟暂停模式退出。