AD1376点击型号即可查看芯片规格书

585点击型号即可查看芯片规格书

特征

带基准和时钟的完整16位转换器;60.003%最大非线性;温度超过14位时无漏码;快速转换;17毫秒到16位(AD1376);10毫秒到16位(AD1377);短周期能力;可调时钟速率;并行和串行输出;低功率:典型645兆瓦(AD1376);典型585兆瓦(AD1377);行业标准引脚。

产品描述

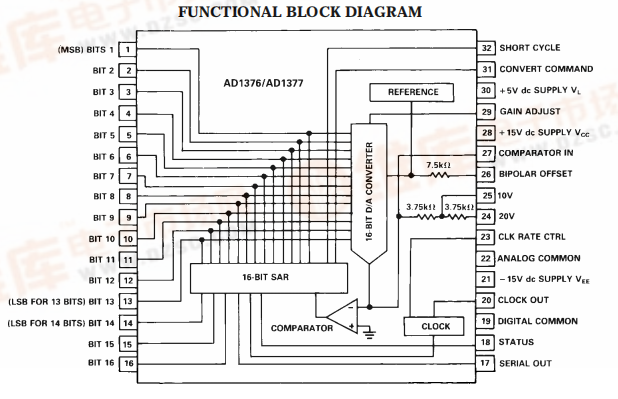

AD1376/AD1377是高分辨率的16位模拟-数字转换器,带有内部参考、时钟和激光修整的薄膜应用电阻器。它们被包装在紧凑型32针,陶瓷骗局密封(密封)双列直插式包装(DIP)。薄膜缩放电阻器提供双极性输入范围为±2.5 V,±5 V,±10 V和单极输入范围0 V至+5 V、0 V至+10 V和0 V至+20 V。数字输出数据以并行和串行形式提供相应的时钟和状态输出。所有数字输入和输出与TTL兼容。

应用

AD1376/AD1377非常适合用于高分辨率要求中等速度和高精度的应用商业(0°C至+70°C)温度范围内的稳定性(对于扩展的温度范围,引脚兼容AD1378推荐使用。)典型应用包括医疗和工业用精密测量分析仪器机器人、自动测试设备(ATE)和多通道数据采集系统、伺服控制系统或任何地方需要宽动态范围的专用单片DAC并且激光修整薄膜电阻器保证最大值。非线性度为±0 003%(1/2 LSB14)。转换器可以是短周期实现更快的转换时间–15微秒到14位对于AD1376,或对于AD1377,为8微秒到14位。

产品亮点

1、AD1376/AD1377在±25°C处提供16位分辨率,最大线性误差±0.003%(1/2 LSB14)。

2、AD1376转换时间为14微秒(典型值),短周期为14位,以及16微秒到16位。

3、AD1377转换时间为8微秒(典型值),短周期为14位,以及9微秒到16位。

4、数字输出上有两个二进制代码。他们是单极输入的互补直二进制电压范围和COB(互补偏移二进制)双极输入范围。互补二补(CTC)编码可通过反转管脚1(MSB)获得。

5、AD1376和AD1377包括内部参考和时钟,带有外部时钟速率调整管脚,以及串行和并行数字输出。

操作说明

在接收到转换启动命令时,AD1376/AD1377将其模拟输入端的电压转换为等效的16位二进制数。该转换完成如下:16位逐次逼近寄存器(SAR)具有其16位输出,既连接到设备位输出引脚,又连接到反馈DAC的相应位输入。模拟输入与反馈DAC输出连续比较,一次一次(MSB优先,LSB最后)。然后,根据比较器当时的状态,在每个比特比较周期结束时作出保留或拒绝每个比特的决定。

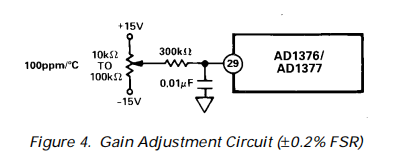

增益调整

增益调整电路由一个100 ppm/℃的电位计组成,该电位计通过一个300 kΩ电阻连接到增益调整引脚29上,其滑块连接在±VS上,如图4所示。

如果不需要外部微调,则引脚27(偏置调整)和引脚29(增益调整)可能保持打开状态。

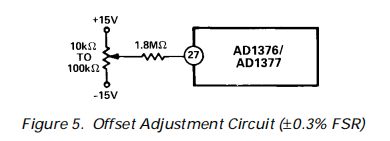

偏移调整

调零电路由一个100 ppm/℃的电位器组成,该电位器通过一个1.8 MΩ电阻连接到所有量程的比较器输入引脚27上,其滑块通过一个±VS连接。如图5所示,该固定电阻器的公差并不重要,碳成分类型通常是足够的。使用碳组成电阻器,温度为–1200 ppm/℃,最坏情况下偏移温度为32 LSB14 361 ppm/LSB14 3 1200 ppm/℃=FSR的2.3 ppm/℃,如果偏置调整电位计设置在其调整范围的任一端。由于所需的最大偏移调整通常不大于±16 LSB14,使用碳成分偏移求和电阻器通常贡献不超过1 ppm /°C的FSR偏移TEMPCO。

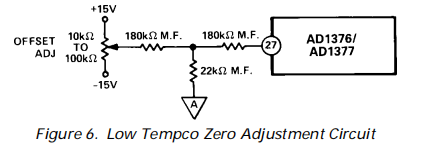

如图6所示,如果使用金属膜电阻器(tempco<100ppm/℃),则可忽略偏置tempco的替代偏置调整电路。

在任一调节电路中,连接到引脚27的固定电阻器应靠近该引脚,以保持引脚连接短路。比较器输入引脚27对外部噪声传感器相当敏感,应使用模拟公共线保护。

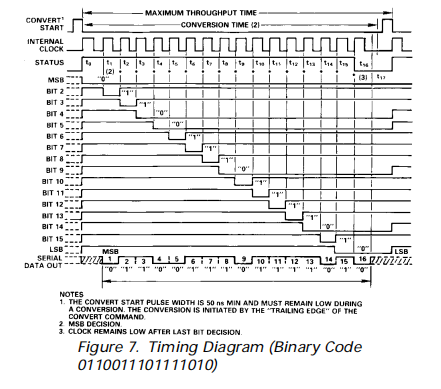

时机

时序图如图7所示。接收到转换开始信号将设置状态标志,指示正在进行转换。这反过来又消除了应用于门控时钟的抑制,允许其运行17个周期。所有SAR并行位、状态触发器和门控时钟抑制信号都在转换开始信号的后缘初始化。在时间t0,B1被重置,B2–B16被无条件设置。在t1时,位1决定(保持),位2无条件复位。此序列继续,直到在t16处作出位16(LSB)决定(keep)。状态标志被重置,表示转换完成并且并行输出数据有效。重置状态标志将恢复门控时钟抑制信号,强制时钟输出到低逻辑“0”状态。请注意,在下一次转换之前,时钟一直处于低位。相应的并行数据位在同一正向时钟边缘上变为有效。

数字输出数据

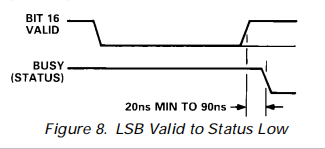

来自TTL存储寄存器的并行和串行数据均为负真形式(逻辑“1”=0 V,逻辑“0”=2.4 V)。并行数据输出编码对于单极性范围是互补二进制,对于双极性范围是互补偏移二进制。并行数据在状态标志返回逻辑“0”前至少20 ns生效,允许并行数据传输在状态标志的“1”到“0”转换上计时(见图8)。

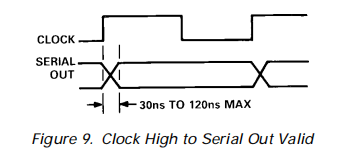

串行数据编码是单极输入范围的互补二进制编码,双极输入范围的互补偏移二进制编码。串行输出以NRZ(不归零)格式按位(先是1M4SB,后是LSB)输出。串行和并行数据输出在正向时钟边缘上改变状态。串行数据保证在上升时钟边缘后120 ns有效,允许串行数据直接进入负向时钟边缘上的接收寄存器,如图9所示。在整个16位转换周期中有17个负时钟边。第一个负边缘将一个无效位移入寄存器,寄存器在最后一个负时钟边缘上移出。

所有串行数据位都将被正确传输,并在转换周期结束时显示在接收移位寄存器位置。

短周期输入

短周期输入Pin 32允许图7所示的定时周期在任意数量的所需比特被转换后终止,允许在不需要完全16位分辨率的应用中稍微缩短转换时间。当需要10位分辨率时,插脚32连接到第11位输出插脚11。然后,转换周期终止,状态标志在第10位决定后重置(图7的时序图)。表I总结了1.6MHz时钟(AD1377)或933kHz(AD1376)的短周期连接和相关的8、10、12、13、14和15位转换时间。

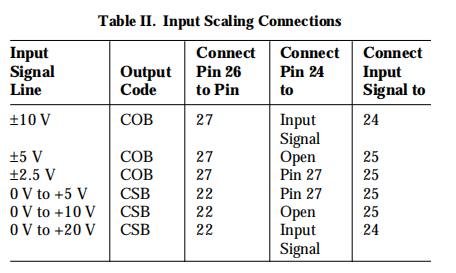

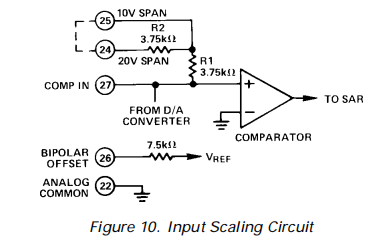

输入缩放

为了利用A/D转换器的最大信号分辨率,ADC(ADC)输入应尽可能接近最大输入信号范围。按表二所示连接输入信号。电路详情见图10。

注意:引脚27对噪音非常敏感,应该由模拟公共线保护。

校准(14位分辨率示例)

外部调零和增益调节电位计,如图4和5所示连接,用于设备校准。为了防止这两个调整之间的相互作用,总是先调整零点,然后再调整增益。零点通过模拟输入在模拟范围最负端附近进行调整(0表示单极输入范围,–FS表示双极输入范围)。增益通过接近模拟范围最正端的模拟输入进行调整。

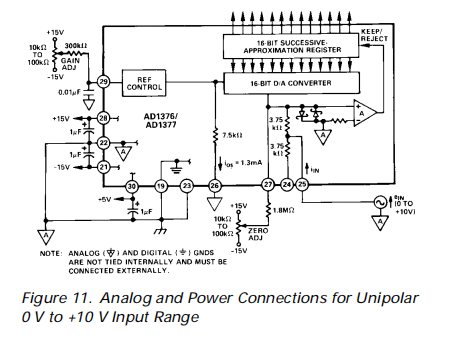

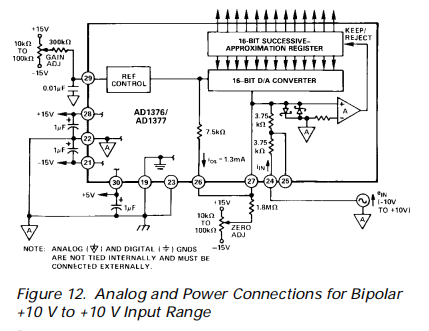

0 V至+10 V范围将模拟输入设为+1 LSB14=0.00061 V。将数字输出调零为11111111110。

零点现在已校准。将模拟输入设置为+FSR–2 LSB=+9.99878 V。调整00000000000001数字输出代码的增益;现在校准满标度(增益)。半刻度校准检查:将模拟输入设置为+5.00000V;数字输出代码应为011111111111。

–10 V至+10 V范围将模拟输入设置为9.99878 V;为111111111 0数字输出(互补偏移二进制)代码调整零。将模拟输入设置为9.99756 V;调整00000000000001数字输出(互补偏移二进制)代码的增益。半刻度校准检查将模拟输入设置为0.00000V;数字输出(互补偏移二进制)代码应为011111111111。

其他范围

上面给出了0 V至+10 V和-10 V至+10 V范围的典型数字编码。0 V至+5 V、-2.5 V至+2.5 V和-5 V至+5 V范围内的编码关系和校准点可通过按比例将0 V至+10 V和-10 V至+10 V范围内列出的相应代码等效值减半来找到范围,分别如表三所示。

利用上述静态调节过程,可以实现零和全量程校准,精度约为±1/2 LSB。通过将小的正弦波或三角波电压与施加到模拟输入的信号相加,输出可以循环通过每个感兴趣的校准码,以更准确地确定每个离散量化电平的中心(或端点)。该动态校准技术的详细描述见D.H.Sheingold,Prentice Hall,Inc.于1986年编辑的《模数转换手册》。

接地、去耦和布局注意事项

许多数据采集部件都有两个或多个接地插脚,这些插脚未在设备内连接在一起。这些“理由”通常被称为逻辑权力回归,模拟公共(模拟电源回路)和模拟信号接地。这些接地(针脚19和22)必须在ADC尽可能靠近转换器的一个点处连接在一起。理想情况下,在转换器下需要一个单一的固态模拟接地平面。电流流过电路卡的导线和蚀刻条纹,由于这些路径具有电阻和电感,在系统模拟接地点和ADC的接地引脚之间可以产生数百毫伏的电压。应为高分辨率转换器提供单独的宽导体条接地回路,以最小化从转换器到系统接地点的路径中电流的噪声和红外损耗。通过这种方式,ADC电源电流和其他数字逻辑门返回电流不会与模拟信号在同一个返回路径中相加,从而导致测量误差。

每个ADC电源端子应尽可能靠近ADC进行电容解耦。大值电容器(例如1μF)与0.1μF电容器并联通常就足够了。模拟电源将被旁路至模拟电源返回引脚和逻辑电源被旁路到逻辑电源返回引脚。

金属盖相对于电源、接地和电信号进行内部接地。不要从外部接地盖。

时钟速率控制

如图13所示,通过将时钟速率控制(引脚23)连接到外部多匝微调电位计(TCR<100 ppm/℃),可以在更快的转换时间下操作AD1376/AD1377。

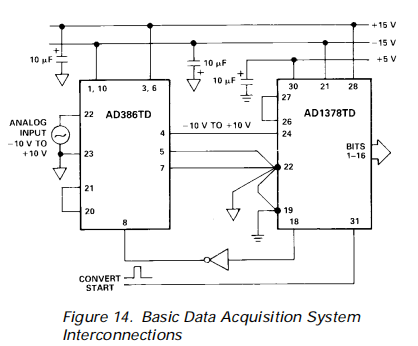

高分辨率数据采集系统

使用AD386和AD1376或AD1377的高分辨率数据采集系统的基本细节如图14所示。转换由转换的下降沿启动启动脉冲。此边缘驱动AD1376或AD1377的状态行高。然后,逆变器驱动AD386进入保持模式。在整个转换过程中,状态保持为高,转换完成后返回低。这允许AD386重新进入跟踪模式。

该电路在A/D输入端由转换启动下降沿产生的暂态过程中会表现出非线性。此边缘重置A/D的内部DAC;产生的瞬态取决于SHA的当前输出电压和A/D的先前转换结果。在图14的电路中,转换启动的下降沿还将SHA置于保持模式(通过A/D的状态输出),导致复位瞬态与SHA的轨迹和保持过渡同时发生。定时偏差和电容耦合会导致一些瞬态信号加入到由SHA获取的信号中,引入非线性。

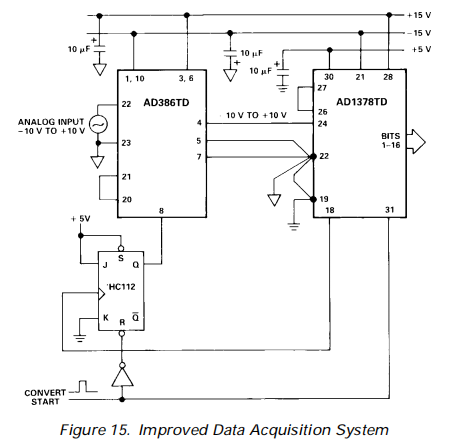

一种更安全的方法是添加触发器,如图15所示。转换启动上升沿在A/D复位瞬变开始前将T/H置于保持模式。状态的下降沿使AD386重新进入跟踪模式。如果长时间转换,系统吞吐量将降低使用启动脉冲。吞吐量可以从:

其中TACQ是T/H获取时间,TCONV是时间A/D转换所需,TCS是转换开始的持续时间。AD1376和AD386的组合将提供大于50 kHz的吞吐量。如果转换开始的宽度与A/D的转换时间相比较小,则不会引入显著的T/H下降误差。

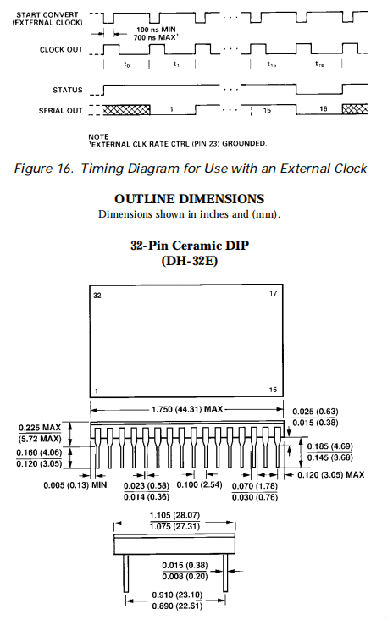

以较慢的转换时间使用AD1376或AD1377为了使A/D与外部时钟同步,用户可能希望以较慢的转换时间运行ADC。这是通过在开始转换输入中运行比内部时钟慢的时钟来实现的。这个时钟必须由窄的负向时钟脉冲组成,如图16所示。脉冲宽度必须至少为100纳秒,但不得大于700纳秒。在下降沿之后立即有上升沿抑制内部时钟脉冲。这使得ADC能够正常工作,并在17个时钟脉冲后完成转换。

状态命令将正常工作,在第一个时钟脉冲后切换为高电平,在第17个时钟脉冲后下降为低电平。通过这种方式,可以使用外部时钟以较慢的转换时间控制ADC。