FAN5009点击型号即可查看芯片规格书

特征

驱动N通道高侧和低侧mosfet同步buck配置12V高压侧和12V低压侧驱动内部自适应“穿透式”保护用于高端驱动的集成自举二极管快速上升和下降时间开关频率高达500kHz输出禁用的OD输入-允许同步带PWM控制器SOIC-8封装提供低热阻MLP封装

应用

微处理器用多相VRM/VRD调节器权力大电流/高频DC/DC转换器大功率模块化电源

一般说明

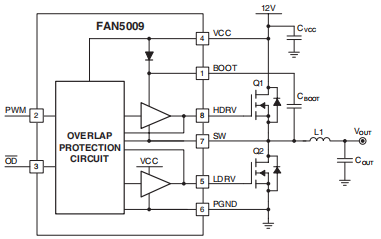

FAN5009是一个双频高频MOSFET驱动器,专为驱动N通道功率mosfet而设计在同步整流buck变换器中。这些司机,结合Fairchild多相PWM控制器和功率mosfet,形成一个完整的核心电压调节器先进微处理器解决方案。风扇5009驱动同步降压调节器到12VGS。上浇口驱动器包括一个集成的引导二极管,只需要一个外部自举电容器(CBOOT)。中的输出驱动程序风扇5009具有高效切换电源的能力频率高达500kHz的mosfet。电路是自适应穿透保护防止mosfet不能同时指挥。风扇5009的额定工作温度为0°C至+85°C,并且提供低成本SOIC-8或MLP封装。

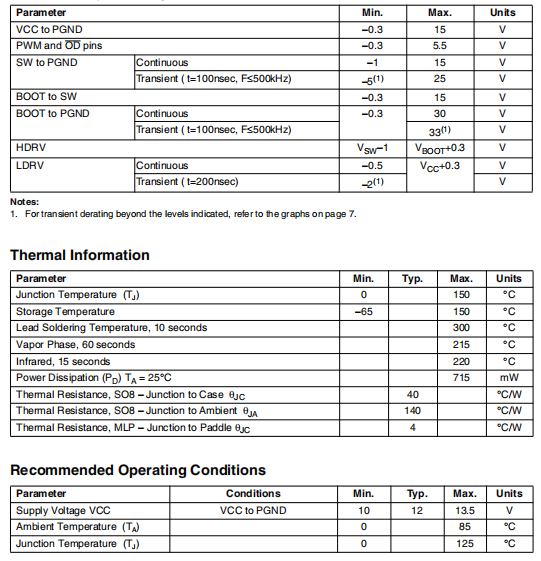

绝对最大额定值在“绝对最大额定值”中列出的应力可能对设备造成永久性损坏。这是仅限应力额定值和设备在这些或其他条件下的功能运行,超出本规范的操作部分并不隐含。暴露于绝对最大额定值条件下延长时间可能会影响设备的可靠性。绝对最大额定值单独应用,而不是组合使用。除非另有规定,电压参考PGND。

电路说明

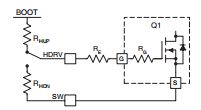

FAN5009是一个双MOSFET驱动器,用于在同步buck变换器中驱动N沟道MOSFET拓扑结构。只需要一个单一的脉冲宽度调制输入信号正确驱动高侧和低侧mosfet。每个驾驶员都能以高达500赫兹。有关FAN5009及其功能,低端驱动器低端驱动器(LDRV)设计用于驱动接地参考低RDS(on)N通道mosfet。偏见LDRV内部连接在VCC和PGND之间。当驱动器启用时,驱动器的输出为与脉宽调制输入的相位。当风扇5009被禁用时(OD=0V),LDRV保持在低位。高端驱动器高侧驱动器(HDRV)设计用于驱动浮动N沟道MOSFET。高压侧的偏压驱动程序由一个自举电源电路开发,包括内部二极管和外部自举电容器(CBOOT)。在启动期间,SW保持在PGND,允许CBOOT通过内部二极管向VCC充电。当脉冲宽度调制输入变高,HDRV将开始向高压侧充电MOSFET栅(Q1)。在这个转换过程中,电荷是从CBOOT中移除并交付到Q1的浇口。作为第一季度打开,开关上升至车辆识别号,强制引导销VIN+VC(BOOT),提供足够的VGS增强第一季度。为了完成切换循环,通过拉动关闭Q1HDRV至SW。当开关打开时,CBOOT再充电到VCC落在PGND。HDRV输出与PWM输入同相。当驾驶员被禁用,高侧门保持在低位。自适应门驱动电路FAN5009采用了先进的设计,确保消除电势的最小MOSFET死区时间穿透(交叉传导)电流。

它感觉到mosfet的状态并自适应地调整栅极驱动,以确保它们不会同时进行。参考图为相关的定时波形。为了防止在从低到高的转换过程中重叠(Q2关到Q1开),自适应电路监视LDRV引脚处的电压。当脉冲宽度调制信号消失时高,Q2将在一些传播后开始关闭延迟(tpdl(LDRV))。一旦LDRV销在~1.2V以下放电,Q1开始在自适应延迟tpdh(HDRV)后打开。在高低转换(Q1)期间防止重叠关至Q2开),自适应电路监测电压在开关管脚处。当脉宽调制信号变低时,Q1将在一些传播延迟(tpdl(HDRV))之后开始关闭。一旦开关引脚降至~2.2V以下,Q2开始开启自适应延迟后tpdh(LDRV)。此外,还监测了第一季度的VGS。当VGS(Q1)为放电低于~1.2V时,启动二次自适应延迟,导致在tpdh(ODRV)之后,Q2被驱动,不考虑软件状态。此函数实现为确保每个开关周期都对CBOOT充电,特别是对于功率转换器下沉电流和开关电压不低于2.2V自适应阈值。二次延时tpdh(ODRV)大于tpdh(LDRV)

应用程序信息

供电电容器选择对于FAN5009的电源输入(VCC),本地陶瓷建议使用旁路电容器来降低噪音和提供峰值电流。使用至少1μF、X7R或X5R电容器。将此电容器靠近风扇5009 VCC和PGND管脚。自举电路自举电路使用电荷存储电容器(CBOOT)和内部二极管,如图1所示。这些部件的选择应在高压侧之后进行选择了MOSFET。所需电容为使用以下公式确定:

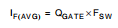

其中QG是高边MOSFET的总栅电荷,而∏VBOOT是高压侧允许的电压降MOSFET驱动器。例如,FDD6696的QG是约35nC@12VGS。对于~300 mV的允许压降所需的自举电容为100nF。好品质必须使用陶瓷电容器。平均二极管正向电流IF(AVG)可以是:

其中FSW是控制器的开关频率。内部二极管的峰值浪涌电流额定值应为检入电路,因为这取决于等效电路整个引导电路的阻抗,包括PCB踪迹。对于要求更高IF的应用程序,外部二极管可与内部二极管并联使用。

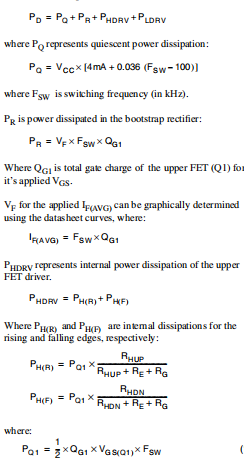

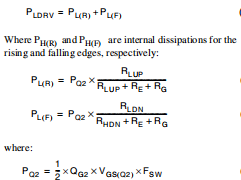

如上文等式8和9所述,总功耗在驱动栅极时,栅极与电阻成正比与MOSFET的内部栅极节点串联,如图所示在下面

RG是FET内部的多晶硅栅电阻。RE是许多设计。注意,引入RE可以减少驱动程序功耗,但过量的RE可能会导致“自适应门驱动”电路。欲了解更多信息,请请参阅Fairchild应用程序注释AN-6003中的“穿透”同步降压转换器。

布局注意事项

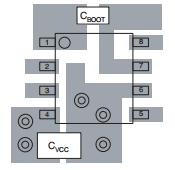

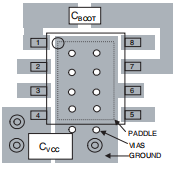

设计印刷品时,请遵循以下一般准则

电路板(见图):

1.找出大电流路径并使用短而宽的(>25 mil)进行这些连接的轨迹。

2.将风扇5009的PGND引脚尽可能靠近可能是低MOSFET的来源。

3.VCC旁路电容器应尽可能靠近可用于VCC和PGND管脚。

4.在可能达到最大化的情况下,使用通孔到其他层远离集成电路的热传导。

5.MLP包上的桨是内部引用的接地。它可以保持漂浮或接地。为了获得最佳的热性能,它应该连接到地面如图所示。

6.MLP中所示的推荐土地类型机械尺寸适用于MLP-8以及SO-8包装。图中的电路演示了一个典型的实现VCORE用单相buck变换器应用。完整的VR10设计示例,请请参阅FAN5019或FAN5018数据表。