FM24C04点击型号即可查看芯片规格书

4096点击型号即可查看芯片规格书

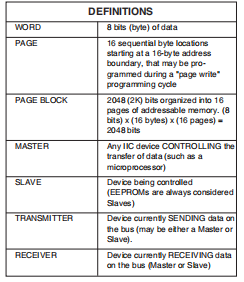

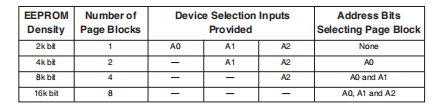

一般说明 :FM24C04U/05U器件是4096位CMOS非易失性器件电可擦存储器这些设备符合标准IIC 2线协议中的所有规范它们被设计成最小化设备管脚数并简化PC板布局要求。FM24C05U的存储器的上半部分(上2Kbit)通过将WP引脚连接到VCC进行写保护本节然后,除非WP切换到VSS,否则内存将无法更改。此通信协议使用时钟(SCL)和数据在主机之间同步时钟数据的I/O(SDA)线路(例如微处理器)和从EEPROM设备。标准IIC协议允许最大16K由Fairchild家族支持的EEPROM存储器2K、4K、8K和16K设备,允许用户配置应用程序所需的内存EEPROMs为了实现更高的EEPROM存储器IIC总线上的密度,必须使用扩展的IIC协议。Fairchild EEPROM是为要求高耐久性、高可靠性和低功耗的应用而设计和测试的。方块图

特征 :扩展工作电压2.7V–5.5V2.7V-5.5V时的400 KHz时钟频率(F)200微安典型有功电流典型的10微安备用电流典型的1微安备用电流(L)0.1微安典型备用电流(LZ)IIC兼容接口–提供双向数据传输协议十六字节页面写入模式–最小化每个字节的总写入时间自动定时写入周期典型写入周期时间为6ms上半部分的硬件写保护(仅限FM24C05U)耐久性:1000000次数据更改数据保存超过40年提供的包装:8针浸渍、8针SO和8针TSSOP有三种温度范围-商用:0°至+70°C-延伸(E):-40°至+85C-汽车(V):-40°至+125°C

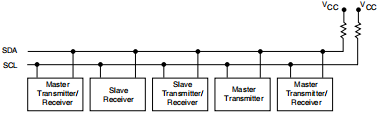

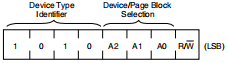

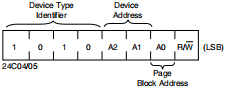

背景信息(IIC总线)IIC总线允许发射机和接收机之间使用时钟信号进行同步双向通信(SCL)和数据信号(SDA)另外还有三个地址信号(A2、A1和A0)统称为“芯片选择信号“到IIC总线上的设备(例如EEPROM)。IIC总线上的所有通信必须以有效的开始条件(由主控),然后是传输(由信息字节(地址/数据)每字节对于接收到的信息,地址接收者提供一个有效的确认脉冲以进一步继续通信除非接收者打算中止通信。根据传输方向(写入或读取),接收器可以是从机或主机典型的IIC通信以停止条件结束(由主机)。寻址EEPROM存储器位置涉及发送包含以下信息的命令字符串:[设备类型]-[设备/页面块选择]-[R/W位]{确认脉冲}-[阵列地址]从机地址从地址是由设备类型组成的8位信息字段(4位)、设备/页面块选择字段(3位)和读取/写入位(1位)。

设备类型IIC总线设计用于支持各种设备,如RAMs,EPROM等,以及EEPROM因此要正确识别IIC总线上的各种设备,4位“设备类型”标识符使用字符串对于eeprom,这个4位字符串是1-0-1-0每个IIC总线上的设备在内部将此4位字符串与其自身的字符串进行比较“设备类型”字符串以确保正确的设备选择。设备/页面块选择当同一类型的多个设备(如多个eeprom)时出现在IIC总线上,然后是A2、A1和A0地址信息位也用作从机地址的一部分每总线上的IIC设备在内部将此3位字符串与其自身的字符串进行比较物理配置(A2、A1和A0引脚)以确保正确设备选择这个比较是在“设备”之外的键入“比较”除了选择EEPROM外,这3个位还用于在选定的电可擦可编程只读存储器每个页面块的大小为2Kbit(256Bytes)根据密度的不同,EEPROM至少可以包含1最多为8个页面块(以2倍数)和选择设备内的页块是通过使用A2、A1和A0位实现的。读/写位从机地址的最后一位表示预期的访问是否读或写如果位是“1”,则读取访问,而如果位是“0”,则访问是写的。

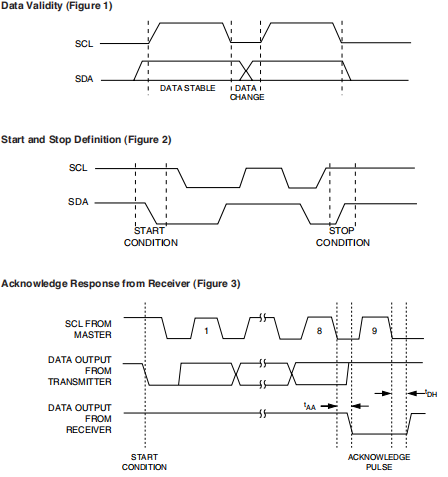

确认是SDA线上由寻址接收器到寻址发射器以指示接收8位数据接收器为每接收到8位数据握手机制已经完成如下:发送8位数据后,发射机释放SDA线,等待ACK脉冲地址如果存在接收器,则在第9个时钟,然后释放SDA线路(至发射机)。参见图。数组地址数组地址是包含要在设备的页块中选择的内存位置。

16K位寻址限制:标准IIC规范限制EEPROM的最大尺寸总线上的内存为16K位这一限制是由于由8位从机组成的寻址协议地址和一个额外的8位字段,称为数组地址这个阵列地址从256个位置中选择1个(28=256)自从IIC规范的数据格式为8位宽,共256 x 8=2048=2K位现在可以由这个8位数组寻址地址这2K位通常被称为“页块”。将此8位数组地址与3位设备/页相结合地址(从属地址的一部分)最多允许8页(23=8)可以寻址的存储器因为每页都是2K位大小,8×2K位=16K位是内存的最大大小。在标准IIC总线上可以寻址这个16Kb的内存可以是单个16Kb EEPROM设备或多个变密度的(最大倍数)到最大值的总共16Kb以满足需要更多在IIC总线上使用的不是16Kb,而是另一种称为“扩展IIC规范”的规范。

管脚说明串行时钟(SCL)SCL输入用于对进出设备的所有数据进行时钟。串行数据(SDA)SDA是一个双向管脚,用于将数据传输到装置它是一个开放式漏极输出,可以与任何开路漏极或开路集电极输出的数量。写保护(WP)(仅限FM24C05U)如果绑定到VCC,则将程序操作绑定到上半部分(上半部分不会执行内存的2位)读取操作是可能的如果绑定到VSS,则启用正常操作,读取/重写整个内存是可能的。此功能允许用户分配内存的上半部分可防止意外编程的只读存储器。当写被禁用时,从地址和字地址将是已确认,但不会确认数据。

这个引脚有一个内部下拉电路但是,在系统上如果不需要写保护,建议pin绑定到VSS。设备选择输入A2、A1和A0(as适当的)这些输入统称为“芯片选择”信号当同一IIC上有多个EEPROM时公共汽车因此,如果存在这些输入,则应连接到VCC或以独特的方式进行VSS,以允许正确选择EEPROM在多个eeprom中在典型的寻址序列中,IIC总线上的每个EEPROM都将这些输入的配置与相应的3位“设备/页面块”进行比较选择“信息(从机地址的一部分),以确定选择例如,如果3位“设备/页面块选择”为1-0-1,则为“设备选择输入”(A2,A1)的EEPROM和A0)分别连接到VCC-VSS-VCC,被选中。根据密度,只有适当数量的“设备“选择输入”在EEPROM上提供对于每个“设备”“选择输入”如果设备上不存在,则使用“设备/页面块选择”字段中的相应位来选择设备内部的“页面块”,而不是设备本身。

设备操作FM24C04U/05U支持双向总线协议协议定义了向总线发送数据的任何设备作为发射机和接收设备作为接收机这个控制传输的设备是主设备被控制的是奴隶主机将始终启动数据传输和提供发送和接收的时钟操作。因此,FM24C04U/05U将被视为所有应用程序中的从属。时钟和数据约定只有在SCL低时,SDA线路上的数据状态才能改变。SCL高期间的SDA状态更改保留用于指示启动和停止条件。启动条件所有命令前面都有start条件,它是SCL高时SDA的高低转换这个FM24C04U/05U连续监测SDA和SCL线路启动条件,在此之前不会响应任何命令条件已满足。停止条件所有通信都由一个停止条件终止,即SCL高时SDA由低到高的转变停止FM24C04U/05U也使用条件来放置设备在待机电源模式下,除非写入操作是正在执行,在这种情况下需要第二个停止条件在tWR周期之后,将设备置于待机模式。

FM24C04U/05U设备在识别到启动条件及其从机地址后,将始终以确认响应如果已选择设备和写入操作,则FM24C04U/05U将在每个后续8位字节的接收。在读取模式下,FM24C04U/05U从机将发送8位对于数据,释放SDA线路并监视该线路是否有应答如果检测到应答,FM24C04U/05U将继续传输数据如果未检测到应答,FM24C04U/05U将终止进一步的数据传输并等待停止条件返回待机电源模式。设备寻址在启动条件之后,主机必须输出它正在访问的奴隶从机最重要的四位地址是设备类型标识符的地址这是固定的1010用于所有EEPROM设备。

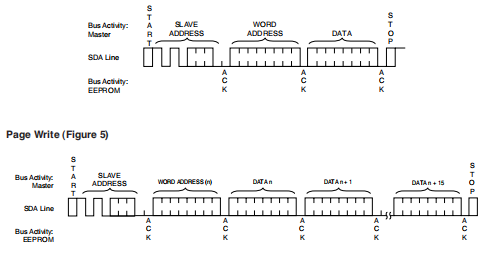

所有IIC EEPROM都使用定义页面的内部协议块大小为2K位(用于字地址0x00到0xFF)。因此,使用地址位A0、A1或A2(如果指定为“P”)与字地址一起访问页块用于访问任何单个数据字节。从地址的最后一位定义是写还是读条件由主机请求“1”表示将执行操作,并由“0”启动写入模式。简单回顾:在FM24C04U/05U识别到开始后条件下,连接到IIC总线的设备等待从设备通过SDA线路传输的地址如果发送从机地址与其中一个设备的地址匹配,即指定的从机通过确认将SDA线路拉低发出信号并等待进一步传输。写操作字节写入对于写操作,需要第二个地址字段,即由八位组成的字地址,提供对选定内存页中256字节中的任意一个在收到字节地址后,FM24C04U/05U用再次确认并等待接下来的8位数据,以确认的方式回应然后主机终止通过生成停止条件进行传输,此时FM24C04U/05U开始对非易失性存储器的内部写入循环当内部写入循环正在进行,FM24C04U/05U输入已禁用,设备将不响应来自的任何请求tWR期间的船长地址见图4,确认和数据传输顺序。

页面写入为了最小化写入周期时间,FM24C04U/05U提供页面写入特征,最多可达到16个连续字节。位置可以一次全部编程(而不是16个单独的字节写入)为了方便这个特性,内存数组是按照“页”来组织的从每16字节地址边界开始的位置(例如,从数组地址0x00、0x10、0x20等开始)第页写操作限制对页内字节位置的访问在换言之,单页写入操作不会交叉到位置在另一页上,但将“翻滚”到每当到达页面末尾和其他位置时显示页面继续被访问页面写入操作可以是开始于页面中的任何位置(起始地址页写入操作不必是第页)。页面写入的启动方式与字节写入相同操作;但不是在发送后终止循环第一个数据字节,主机可以进一步发送多达15个字节收到每个字节后,FM24C04U/05U将响应使用确认脉冲,增加内部地址计数器到下一个地址,并准备接受下一个数据如果在生成停止条件之前,主机应发送超过16个字节,地址计数器将“翻转”并以前写入的数据将被覆盖就像字节写入一样操作,在完成内部写循环地址、确认和数据传输顺序。

确认轮询一旦发出停止条件以指示主机的写入操作,FM24C04U/05U启动内部写入循环ACK轮询可以立即启动这涉及到发出起始条件后接从机地址进行写入操作如果FM24C04U/05U仍忙于写入操作不返回确认如果FM24C04U/05U有完成写入操作后,将返回一个ACK,并且然后,主机可以继续执行下一个读或写操作。写保护(仅限FM24C05U)内存上半部分(上2Kbit)的编程将不会如果FM24C05U的WP引脚连接到VCC,则发生。FM24C05U将响应从机和字节地址;但是如果访问的内存由WP pin写保护,WP pinFM24C05U在第一个字节后不会产生应答已收到的数据因此,程序周期不会在断言停止条件时启动。

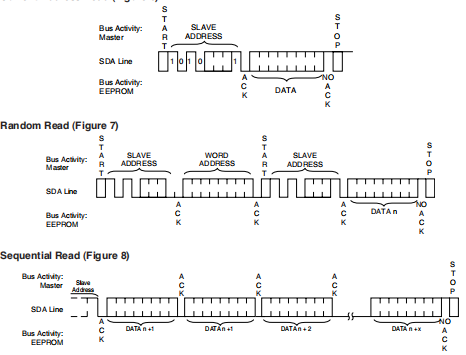

读取操作读操作的启动方式与写操作相同操作,除了从机的R/W位地址设置为1有三种基本读取操作:当前地址读取、随机读取和顺序读取。当前地址读取FM24C04U/05U内部包含一个地址计数器维护访问的最后一个字节的地址,增量为一个因此,如果最后一次访问(读或写)是地址n,下一个读取操作将从地址n+1收到R/W设置为的从机地址时首先,FM24C04U/05U发出确认并发送八位字主人不会承认转让但确实产生了停止条件,因此FM24C04U/05U停止传输地址、确认和数据传输的顺序见图6。随机读取随机读取操作允许主机访问任何内存以随机的方式定位在发出从机地址之前当R/W位设置为1时,主机必须首先执行“虚拟”写入操作主人发出启动条件,从地址,R/W位设置为零,然后是字节地址已读取字节地址确认后,主机立即发出另一个启动条件和从机地址R/W位设为1接下来是FM24C04U/05U的确认,然后是8位字这个主服务器不会确认传输,但会生成停止条件,因此FM24C04U/05U停止传输有关地址、确认和数据传输顺序。顺序读取顺序读取可以作为当前地址读取启动或随机存取读取第一个字是用同样的方式传送的与其他读取模式一样的方式;但是,现在的主机以确认回应,表示它需要额外的数据FM24C04U/05U继续为每个收到确认读取操作由主机没有应答应答或生成停止条件。数据输出与来自地址n的数据是连续的然后是n+1的数据用于读取的地址计数器操作增加所有字地址位,允许在一次操作中要连续读取的内存内容之后整个内存已被读取,计数器“翻转”到记忆的开始FM24C04U/05U继续输出收到的每个确认的数据参见图地址、确认和数据传输顺序。