633点击型号即可查看芯片规格书

333点击型号即可查看芯片规格书

8226点击型号即可查看芯片规格书

模块

功能,体系结构概述,阵列大小和资源,功能描述DS099(v3.1)输入/输出块(IOB),IOB概述,SelectIO接口I/O标准,可配置逻辑块(CLB)块RAM,专用乘法器,数字时钟管理器(DCM)时钟网络,配置模块3:DC和开关特性DS099(v3.1)直流电气特性绝对最大额定值电源电压规格推荐的工作条件直流特性开关特性I/O定时内部逻辑时序DCM计时配置和JTAG定时模块4,引脚说明,配置期间的引脚行为,封装概述,引脚表,封装外形

介绍Spartan®3系列现场可编程门阵列是专门为满足大容量、成本敏感的消费电子应用而设计的。

这八个成员家庭提供的系统门密度从50000到5000000不等。Spartan-3系列的成功建立在早期Spartan IIE系列的基础上,它增加了逻辑资源的数量、内部RAM的容量、I/O的总数和总体性能水平,并改进了时钟管理功能许多增强源于virtex?-ii平台技术。这些Spartan-3fpga的增强功能,结合先进的处理技术,提供了比以前更多的功能和每美元的带宽,在可编程逻辑行业建立了新的标准由于成本极低,Spartan-3 FPGas非常适合广泛的消费电子应用,包括宽带接入、家庭网络、显示/投影和数字电视设备。斯巴达-3系列是一个优于掩模编程asic的替代品。FPGA避免了传统ASIC的高初始成本、冗长的开发周期和固有的灵活性。此外,fpga的可编程性允许在不需要硬件替换的情况下进行现场设计升级,这在asic中是不可能的。

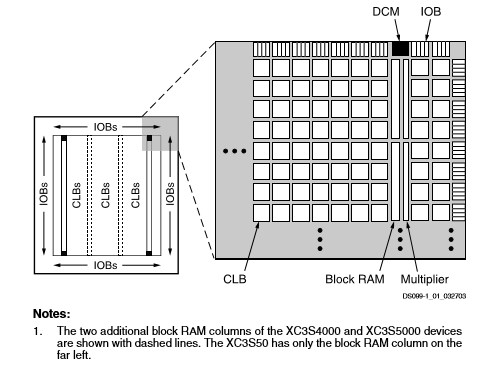

功能,低成本、高性能的逻辑解决方案,适用于大容量、面向消费者的应用程序,高达74880个逻辑单元的密度,selectio接口信令,高达633个I/O管脚,每个I/O的622+MB/s数据传输速率,18个单端信号标准,8个差分I/O标准,包括LVD、RSD,终端通过数字控制阻抗,信号摆动范围从1.14V到3.465V,双数据速率(DDR)支持,DDR,DDR2 SDRAM支持高达333 MB/s,逻辑资源,丰富的逻辑单元,具有移位寄存器功能,宽,快速多路复用器,快速前瞻进位逻辑,专用18 x 18乘法器,与IEEE 1149.1/1532兼容的JTAG逻辑,SelectRAM分层存储器,总块RAM高达1872kbit,总分布式RAM高达520kbit,数字时钟管理器(高达四个DCMs)时钟偏差消除,频率合成,高分辨率相移,八条全局时钟线和丰富的路由,完全由Xilinx ISE®和Webpack软件开发系统支持,Microblaze和PicoBlaze处理器、PCI®和PCI Express®管道端点以及其他IP核,无PB封装选项,Automotive Spartan-3 XA系列变型体系结构概述Spartan-3系列体系结构由五个基本的可编程功能元件组成:可配置逻辑块(CLB)包含基于RAM的查找表(LUT),用于实现可用作触发器或锁存器的逻辑和存储元件。clb可以编程来执行各种各样的逻辑功能以及存储数据。输入/输出块(IOB)控制I/O引脚和设备内部逻辑之间的数据流每个IOB支持双向数据流和三态操作26种不同的信号标准,包括双数据速率(DDR)寄存器。数字控制阻抗(DCI)特性提供了自动片上终端,简化了电路板设计。块RAM以18kbit双端口块的形式提供数据存储,乘法器块接受两个18位二进制数作为输入并计算乘积,数字时钟管理器(DCM)模块为分配、延迟、乘法、除法和移相时钟信号提供自校准的全数字解决方案。这些元素的组织如图1所示。一个iob环围绕着一个规则的clb数组。xc3s50在阵列中嵌入了一列块ram。从XC3S200到XC3S2000的设备有两列块RAMxc3s4000和xc3s5000设备有四个ram列。每列由几个18kbit的ram块组成;每个块都与一个专用的乘法器相关联。DCM位于外部块RAM列的末端Spartan-3系列具有丰富的记录道和交换机网络,将所有五个功能元件互连,在它们之间传输信号。每个功能元件都有一个相关的开关矩阵,允许多个连接到路由。

配置Spartan-3fpgas通过将配置数据加载到健壮的可重编程静态CMOS配置锁存器(CCLs)中进行编程,CCLs共同控制所有功能元件和路由资源在给fpga通电之前,配置数据存储在外部prom或其它非易失性介质中,无论是在板上还是板下。

注:1.xc3s4000和xc3s5000设备的另外两个块ram列用虚线显示。xc3s50在最左边只有block ram列。

电源,配置数据使用五种不同模式中的任意一种写入到fpga中:主并行、从并行、主串行、从串行和边界扫描(jtag)。主从并行模式使用8位宽的selectmap端口。用于存储配置数据的推荐存储器是低成本的Xilinx平台Flash PROM系列,其中包括用于串行配置的XCF00S PROM和用于并行或串行配置的高密度XCF00P PROM。

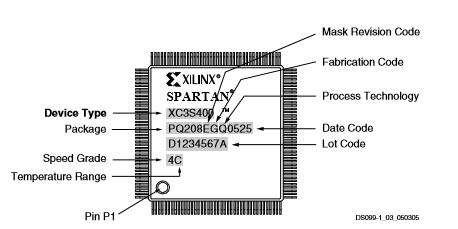

包装标记

四平板包装中Spartan-3 FPGas的顶部标记。BGA封装中Spartan-3 FPGas的顶部标记,但132球屑秤封装(CP132和CPG132)除外。bga封装的标记与四平板封装的标记几乎相同,只是标记相对于球a1指示器旋转。CP132和CPG132封装中Spartan-3 FPGAs的顶部标记“5C”和“4I”部件组合可双重标记为“5C/4I”。带有双标记的设备可以用作-5c或-4i设备。只有在标记的速度等级和温度范围内,才保证设备有一个标记。有些规格根据面具的修订而有所不同。掩模修订版E设备无勘误。自2006年以来的所有货物均为E版面罩。

零件号XC3S400-4PQ208C的Spartan-3现场可编程门阵列QFP封装标记示例

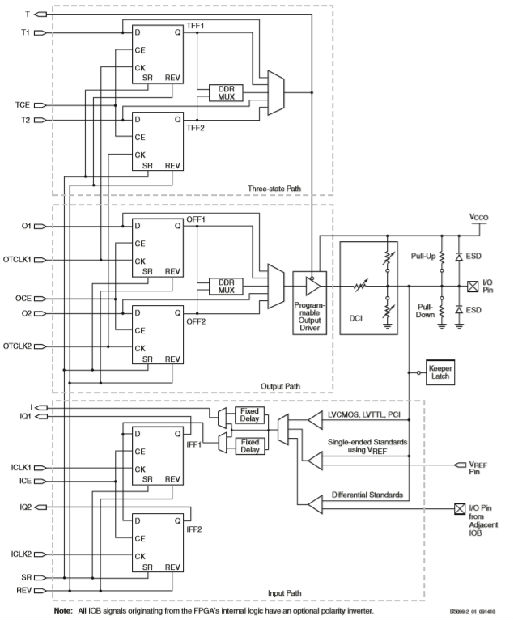

Spartan-3 fpga设计文档Spartan?-3 fpga系列的功能在以下文档中描述。列出了每个指南中涉及的主题。8226;UG331:Spartan-3代FPGA用户指南•时钟资源•数字时钟管理器(DCMs)•块RAM•可配置逻辑块(CLB)-分布式RAM-SRL16移位寄存器-进位和算术逻辑•I/O资源•嵌入式乘法器块•可编程互连•ISE®软件设计工具•IP核心•嵌入式处理和控制解决方案•管脚类型和封装概述•封装图•为FPGas供电•UG332:SPARTAN-3代配置用户指南•配置概述-配置管脚和行为-比特流大小•按模式详细描述-使用Xilinx平台Flash的主串行模式PROM-Slave Parallel(SelectMAP)使用处理器-Slave Serial使用处理器-JTAG模式•ISE iMPACT编程示例创建一个Xilinx用户帐户,并在更新此数据表或相关用户指南时注册以接收自动电子邮件通知输入/输出块(iob)在i/o引脚和fpga内部逻辑之间提供一个可编程的双向接口。IOB内部结构的简化图如图7所示IOB中有三个主要的信号路径:输出路径、输入路径和三态路径。每个路径都有自己的一对存储元素,它们可以充当寄存器或锁存器。有关详细信息,请参阅存储元素函数部分三条主要信号路径如下:•输入路径通过可选的可编程延迟元件直接将数据从焊盘(焊盘连接到封装引脚)传送到I线。有通过一对存储元件到iq1和iq2线的备用路由。iob输出i、iq1和iq2都指向fpga的内部逻辑。延迟元件可以设置为确保保持时间为零•输出路径,从O1和O2线开始,通过多路复用器从FPGA内部逻辑传输数据,然后通过一个三态驱动器传输到IOB板。除此直接路径外,多路复用器还提供插入一对存储元件的选项。•三态路径确定输出驱动器何时为高阻抗。T1和T2线通过多路复用器将数据从FPGA的内部逻辑传输到输出驱动器。除此直接路径外,多路复用器还提供插入一对存储元件的选项。当T1或T2线被断言为高时,输出驱动器为高阻抗(浮动,hi-Z)输出驱动程序激活低启用。•所有进入IOB的信号路径,包括与存储元件相关的路径,都有一个逆变器选项。放置在这些路径上的任何逆变器都会自动吸收到IOB中。

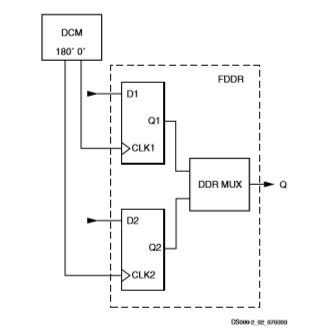

存储元素函数在每个IOB中有三对存储元素,三条路径中的每一条都有一对可以将这些存储元件中的每一个配置为边缘触发d型触发器(fd)或电平敏感锁存器(ld)。输出路径或三态路径上的存储元件对可与专用多路复用器一起使用以产生双数据速率(DDR)传输。这是通过将同步到时钟信号上升沿的数据转换成上升沿和下降沿同步的位来实现的。两个寄存器和多路复用器的组合称为双数据率d型触发器(fddr)。

双数据速率传输双数据速率(DDR)传输描述了将信号同步到时钟信号上升和下降边缘的技术。Spartan-3设备在所有三条IOB路径中使用寄存器对来执行DDR操作iob输出路径上的一对存储元件(off1和off2)用作寄存器,与一个特殊的多路复用器结合形成ddr d型触发器(fddr)。该原语允许ddr传输,其中输出数据位与时钟的上升和下降边缘同步。可以通过在设计中放置fddrrse或fddrcpe组件或符号来访问此功能。DDR操作需要两个时钟信号(50%占空比),一个是另一个的倒转形式。这些信号以交替方式触发两个寄存器,如图8所示。通常,数字时钟管理器(DCM)通过镜像一个输入信号,然后将其移动180度来生成两个时钟信号。这种方法确保了两个信号之间的最小偏差。三态路径(TFF1和TFF2)上的存储元件对还可以与本地多路复用器组合以形成FDDR原语这允许将输出同步到时钟的上升和下降边缘。此DDR操作的实现方式与输出路径相同输入路径(iff1和iff2)上的存储元件对允许i/o接收ddr信号。输入的ddr时钟信号触发一个寄存器,而倒时钟信号触发另一个寄存器。通过这种方式,寄存器轮流捕获传入的ddr数据信号的位。

除了高带宽的数据传输外,DDR还可用于在输出端再现或“镜像”时钟信号这种方法用于同时传输时钟和数据信号类似的方法用于在多个输出端再现时钟信号。这两种方法的优点是输出的偏差最小一些相邻的I/O块(IOB)共享连接两个IOB的ICLK1、ICLK2、OTCLK1和OTCLK2时钟输入的公共路由这些iob对通过它们的差分对名称i o_xn_35;和io_xxp_35;来标识,其中“xx”是i/o对编号,“3535;”是i/o银行编号。包含ddr寄存器的两个相邻iob必须共享公共时钟输入,否则一个或多个时钟信号将无法输出。

上拉和下拉电阻器可选的上拉和下拉电阻器用于分别在未使用的I/O上建立高电平和低电平。上拉电阻器可选择将每个IOB板连接到VCCO。一个下拉电阻器可以选择地将每个焊盘连接到GND这些电阻器分别使用原理图中的上拉和下拉符号放置在设计中。它们还可以实例化为组件、设置为约束或在HDL代码中作为属性传递也可以使用位流生成器(bitgen)选项unusedpin为所有未使用的I/O选择这些电阻器。HSWAP_EN上的低逻辑电平在配置期间激活所有I/O上的上拉电阻器(请参阅第21页的“通电、配置和用户模式期间的I/O”)spartan-3fpga i/o上拉和下拉电阻明显强于先前xilinx fpga家族中使用的“弱”上拉/下拉电阻。等效电阻强度见第61页表33。

保持器电路每个I/O都有一个可选的保持器电路,它在所有驱动器关闭后保持线路上的最后一个逻辑电平。当所有连接的驱动器都处于高阻抗状态时,这有助于防止总线浮动此函数使用KEEPER符号放置在设计中上拉和下拉电阻器超越保持器电路。

ESD保护钳位二极管保护所有的装置衬垫免受静电放电(ESD)和过大电压瞬变的损坏。每个i/o有两个钳位二极管:一个二极管从pad向vcco扩展p-to-n,另一个二极管从pad向gnd扩展n-to-p。在工作过程中,这些二极管通常在关闭状态下有偏压。无论选择何种信号标准,这些钳位二极管始终连接到焊盘。二极管的存在限制了spartan-3fpga的i/o承受高信号电压的能力。

回转率控制和驱动强度两个选项,快速和慢速,控制输出回转率。快速选项支持高速输出切换。慢速选项减少总线瞬态这些选项仅在使用lvcmos或lvttl标准之一时可用,该标准还提供多达七种不同级别的电流驱动强度:2、4、6、8、12、16和24ma。选择适当的驱动强度级别是另一种最小化总线瞬态的方法。

数字控制阻抗(DCI)当输出信号(即从输出到输入再返回)的往返延迟超过上升和下降时间时,通常在传输信号的线路上增加终端电阻。这些电阻有效地将设备的输入/输出阻抗与传输线的特性阻抗匹配,从而防止对信号完整性产生不利影响的反射。然而,随着现代设备支持的高I/O计数,添加电阻需要明显更多的组件和板面积。此外,对于某些封装,例如球栅阵列,可能不总是能够将电阻器放置在引脚附近。DCI通过提供两种片上终端来解决这些问题:并行终端使用集成电阻网络串联端接是控制输出驱动器阻抗的结果。DCI主动调整并联和串联终端,以精确匹配传输线的特性阻抗。此调整过程补偿了因环境温度、电源电压和制造过程的正常变化而导致的输入/输出阻抗差异。当输出驱动器关闭时,根据定义,串联终端接近非常高的阻抗;相反,并联终端电阻保持在目标值DCI仅适用于某些I/O标准,如表10所示。通过对符号或组件应用适当的I/O标准扩展来选择DCI。有五种配置终端的基本方法,如表11所示DCI I/O标准确定哪些终端已生效。hstl_i_dci-、hstl_iii_dci-和sstl2_i_dci-型输出不需要vrn和vrp参考电阻。同样,LVDCI型输入不需要VRN和VRP参考电阻在没有任何dci i/o的组或包含非dci i/o和纯hstl_u dci-或hstl_u dci-型输出或sstl2_u dci-型输出或lvdci-型输入的组中,相关的vrn和vrp管脚可以用作通用i/o管脚。hslvdci(高速lvdci)标准用于双向使用。驱动程序与lvdci相同,而输入与hstl相同。通过使用vref参考输入,hslvdci允许在接收器处比使用单端lvcmos类型接收器时更大的输入灵敏度。

Spartan-3fpga兼容在Spartan-3系列中,所有设备都通过封装实现pin兼容当对未来逻辑资源的需求超过当前使用的Spartan-3设备的容量时,同一个包中的更大的设备可以直接替代较大的设备可能会添加额外的vref和vcco线路,以支持更多的i/o。在较大的设备中,更多的管脚可以从用户I/O转换为VREF线另外,额外的VCCO线路连接到较小设备中“未连接”的管脚上。因此,在电路板初始设计时,通过布置与额外引脚的连接来规划未来的升级是很重要的。Spartan-3系列与之前的任何Xilinx FPGA系列或Spartan-3代FPGas中的其他平台都不兼容。

有关银行的规则在将I/O分配给银行时,必须遵循以下VCCO规则:不要让VCCO管脚未连接到FPGA上。将与(互连)组相关的所有VCCO线路设置为相同的电压水平。分配给(互联)银行I/O的所有标准所使用的V CCO级别必须一致xilinx开发软件会对此进行检查。每个银行的输出仅允许采用以下标准之一:LVDS、LDT、LVDS-EXT或RSD此限制适用于每个设备中的八个银行,即使VCCO级别是跨银行共享的,如CP132和TQ144包中所述。如果分配给(互连)组I/O的任何标准都不使用VCCO,则将所有相关VCCO线路连接至2.5V。通常,从通电到配置结束,对VCCO组4施加2.5V电压。在并联配置或回读操作期间,向VCCO气缸组5施加相同的电压有关如何使用3.3v信号和电源对fpga编程的信息,请参阅3.3v容错配置接口部分。如果分配给气缸组输入的任何标准使用VREF,则遵循以下附加规则:•将气缸组内的所有VREF引脚连接到相同的电压水平。•分配给银行输入的所有标准所使用的参考电压等级必须一致xilinx开发软件会对此进行检查。表8和10描述了不同标准如何使用VREF供应。如果没有一个分配给银行输入的标准使用VREF来偏置输入开关阈值,则所有相关的VREF管脚都作为用户I/o工作。

支持I/O标准的银行例外情况VQ100、CP132或TQ144包中任何Spartan-3设备的银行5不支持DCI信号标准。在这种情况下,气缸组5既没有VRN也没有VRP引脚。

为IOB提供电压三种不同的电源为IOB供电:•V CCO为输出驱动器供电,除使用GTL和GTLP信号标准时外,每个I/O组一个电源。VCCO引脚上的电压决定了输出信号的电压摆动•v ccint是fpga内部逻辑的主电源。V CcAUX是辅助电源,主要是为了优化诸如I/O转换等各种FPGA功能的性能。

在通电、配置和用户模式期间,在没有向fpga通电的情况下,所有i/o都处于高阻抗状态。VCCINT(1.2V)、VCCAUX(2.5V)和VCCO电源可以按任何顺序使用。在通电完成之前,VCCINT、VCCO Bank 4和VCCAUX必须达到各自的最低建议操作水平(见第59页表29)。此时,所有I/O驱动器也将处于高阻抗状态。VCCO气缸组4、VCCINT和VCCAUX用作内部通电复位电路(POR)的输入。应用于hswap_en输入的低电平使用户i/o上的上拉电阻器能够在整个配置过程中从通电开始工作。hswap_en上的高电平将禁用上拉电阻器,从而允许I/O浮动。如果hswap_en引脚浮动,则内部上拉电阻器将hswap_en拉高。一旦通电,fpga就开始初始化其配置存储器。同时,FPGA内部声明全局重置(GSR),它异步地将所有IOB存储元素重置为低状态初始化完成后,INIT_B变高,对M0、M1和M2输入进行采样以确定配置模式此时,配置数据被加载到fpga中。在整个配置过程中,I/O驱动器始终处于高阻抗状态(根据HSWAP_EN输入确定是否有上拉电阻器)全球三态(GTS)网络在启动过程中释放,标志着用户模式下的配置结束和设计操作开始。此时,那些被分配了信号的I/O将处于活动状态,而所有未使用的I/O将保持在高阻抗状态GSR网络的释放,也是启动的一部分,默认情况下使IOB寄存器处于低状态,除非加载的设计颠倒了其各自RS输入的极性。在用户模式下,I/O上的所有内部上拉电阻器都被禁用,HSWAP_en变成一个“不在乎”输入。如果需要在带有信号的I/O上安装上拉或下拉电阻器,则在设计中必须将适当的符号(如上拉、下拉)放置在适当的衬垫上。xilinx开发软件中提供的bitstream generator(bitgen)选项unusedpin确定未使用的i/o在用户模式下是否具有上拉电阻、下拉电阻或无电阻。

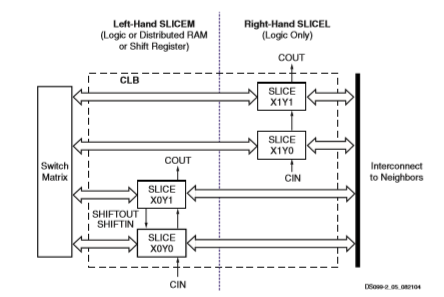

“使用可配置逻辑块”的章节可配置逻辑块(clb)是实现同步电路和组合电路的主要逻辑资源。每个CLB包含四个相互连接的切片,如图11所示这些切片成对分组。每一对都被组织成一个具有独立进位链的列。xilinx开发软件的fpga编辑器部分用于指定片的命名方式如下:字母“x”后跟数字表示片的列。“X”数字从模具左侧到右侧依次递增字母“y”后跟一个数字,用于标识一对中每个切片的位置以及指示CLB行。“Y”数字按以下顺序对从模具底部开始的切片进行计数:0、1、0、1(第一个CLB行);2、3、2、3(第二个CLB行);等等。位于模具左下角的CLB。切片X0Y0和X0Y1构成左侧的列对,其中切片X1Y0和X1Y1构成右侧的列对对于每个clb,术语“left-hand”(或slicem)指示标记有偶数“x”号的一对切片,例如x0,术语“right-hand”(或slicel)指示带有奇数“x”号的一对切

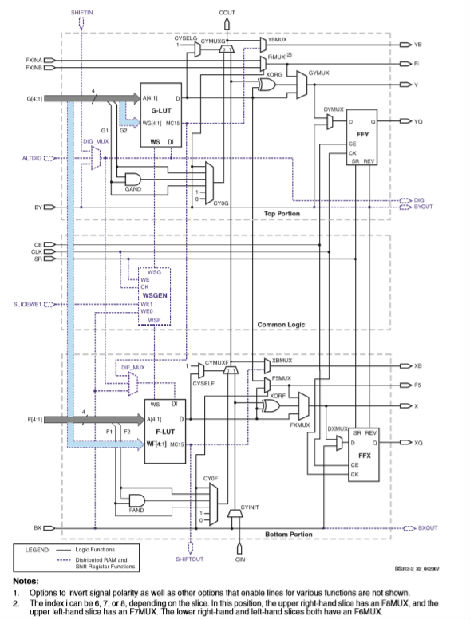

一个片中的两个lut(F和G)中的每一个都有四个逻辑输入(A1-A4)和一个输出(D)这允许任何四变量布尔逻辑运算被编程到它们中。此外,宽函数多路复用器可用于在同一个clb内或跨不同clb有效地组合lut,使得具有更多输入变量的逻辑函数成为可能。右手和左手切片对中的lut不仅支持上述逻辑功能,而且还可以作为rom使用配置时的数据初始化。每个clb的左侧切片对中的lut支持右侧切片对(奇数列,如x1)不支持的两个附加函数。首先,可以将“左侧lut”编程为分布式RAM这种类型的内存在数据路径的任何地方都提供适度的数据缓冲一个左侧的lut存储16位。可以以各种方式组合多个左侧lut以存储更大数量的数据双端口选项结合了两个lut,因此可以从两条独立的数据线进行内存访问。分布式ROM选项允许在FPGA配置期间用数据预加载存储器其次,可以将每个左手LUT编程为16位移位寄存器以这种方式使用,每个lut可以将串行数据延迟1到16个时钟周期。单个CLB的四个左侧lut可以组合起来产生高达64个时钟周期的延迟移位和移位线路级联lut以形成更大的移位寄存器。也可以跨多个CLB组合移位寄存器。由此产生的可编程延迟可用于平衡数据管道的定时。

块RAM概述所有Spartan-3设备都支持块RAM,它被组织为可配置的同步18Kbit块块ram比前面描述的分布式ram特性更有效地存储相对大量的数据。(后者更适合沿信号路径在任何地方缓冲少量数据。)本节介绍基本块RAM功能。有关更多信息,请参阅UG331中题为“使用块RAM”的章节。宽高比,即每个块RAM的宽度与深度是可配置的此外,可以级联多个块以创建更宽和/或更深的存储器原语之间的选择决定块ram是作为双端口存储器还是单端口存储器工作。形式为RAMB16_S[wA]_S[wB]的名称调用双端口原语,其中整数wA和wB分别指定端口wA和wB的总数据路径宽度因此,RAMB16_S9_S18是具有9位宽端口a和18位宽端口B的双端口RAM。形式为RAMB16_S[w]的名称标识单端口原语,其中整数w指定单端口的总数据路径宽度ramb16_s18是具有18位宽端口的单端口ram。其他内存功能,如fifo、数据路径宽度转换、rom等,可以使用xilinx开发软件的core generator™软件轻松获得。

在片上同步情况下,

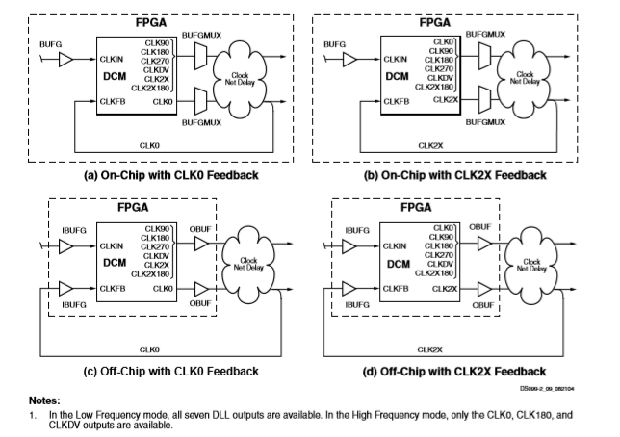

可以通过通用路由资源将dll的七个输出时钟信号中的任何一个连接到fpga的内部寄存器。全局时钟缓冲区(bufg)或bufgmux提供对全局时钟网络的访问。通过将CLK0(或CLK2X,在[b]部分中)路由到全局时钟网络来创建反馈回路,进而驱动CLKFB输入在片外同步情况下,Clk0(或Clk2x)加上任何DLL的其他输出时钟信号使用输出缓冲器(OBUF)退出FPGA,以驱动外部时钟网络加上板上的寄存器。如图21的[c]部分所示,通过使用直接访问全局时钟网络或ibufg的ibufg将clk0(或在[d]部分中的clk2x)馈送回fpga,形成反馈环路。然后,全局时钟网络直接连接到clkfb输入。动态链接库频率模式动态链接库支持两种不同的工作模式,高频和低频,每种模式都在不同的时钟频率范围内指定。dll_frequency_mode属性在两种模式之间进行选择。当属性设置为低时,低频模式允许所有七个DLL时钟输出在低到中等频率范围内运行当属性设置为high时,高频模式允许clk0、clk180和clkdv输出以尽可能高的频率工作。其余的dll时钟输出不可用于高频模式。如果CKIN信号的频率高,使其超过最大允许值,则使用高输入频率,将其划分为可接受的值,使用CKNYLIDVIEBYBYS2属性。当该属性设置为TRUE时,CLKIN频率在进入DCM时被2的因子除以。

本协议所提及的Xilinx硬件FPGA和CPLD器件的声明不受Xilinx有限保修条款和条件的限制,本有限保修不适用于在不符合Xilinx数据表中规定规格的应用或环境中使用产品。所有规格如有更改,恕不另行通知产品的设计或意图不是故障安全的,也不是用于任何需要故障安全性能的应用,如生命支持或安全装置或系统,或任何其他引起死亡、人身伤害或财产或环境损害的潜在风险的应用(“关键应用”)。根据适用的法律法规,在关键应用中使用产品的风险由客户自行承担关键应用免责声明XILINX产品(包括硬件、软件和/或IP核心)不是设计或打算用于故障安全,或用于任何需要故障安全性能的应用,如生命支持或安全设备或系统、三级医疗设备、核设施与安全气囊展开相关的应用,或可能导致死亡、人身伤害或严重财产或环境损害的任何其他应用(单独或共同称为“关键应用”)此外,除非有故障安全或冗余功能(不包括在Xilinx设备中使用软件实现冗余)和操作员故障时的警告信号,否则Xilinx产品的设计或意图不适用于影响车辆或飞机控制的任何应用。客户同意,在使用或分发包含Xilinx产品的任何系统之前,出于安全目的对其进行彻底测试。在适用法律允许的最大范围内,客户承担在关键应用中使用Xilinx产品的全部风险和责任。汽车应用免责声明Xilinx产品不是设计或打算用于故障安全,或用于任何需要故障安全性能的应用,例如与下列应用相关的应用:(i)安全气囊的展开,(ii)车辆的控制,除非有故障安全或冗余功能(不包括在Xilinx设备中使用软件实现冗余)和操作员故障时的警告信号,或(iii)使用可能导致死亡或人身伤害。客户承担在此类应用中使用Xilinx产品的全部风险和责任。