ADP3412点击型号即可查看芯片规格书

3000点击型号即可查看芯片规格书

180点击型号即可查看芯片规格书

特征

一体化同步buck驱动程序;自举高侧驱动器;一个脉冲宽度调制信号产生两个驱动器;可编程转换延迟;防交叉传导保护电路。

应用

多相台式CPU电源;移动计算CPU核心功率转换器;单电源同步降压变换器;标准到同步转换器的适配。

一般说明

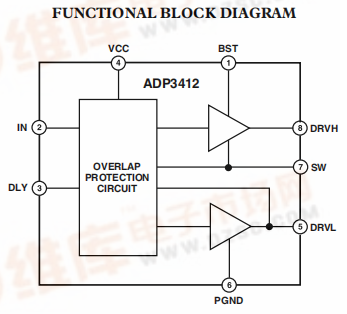

ADP3412是一款为驱动而优化的双mosfet驱动器两个N通道mosfet,它们是a中的两个开关非隔离同步降压功率变换器每一个驱动器能够以20 ns的传播延迟和30 ns的转换时间驱动3000 pf负载。其中一个司机可以自举,用于处理高压与“浮动”高侧门驱动器相关的回转率。这个ADP3412包括重叠驱动保护(ODP),以防止外部mosfet中的穿透电流。

ADP3412

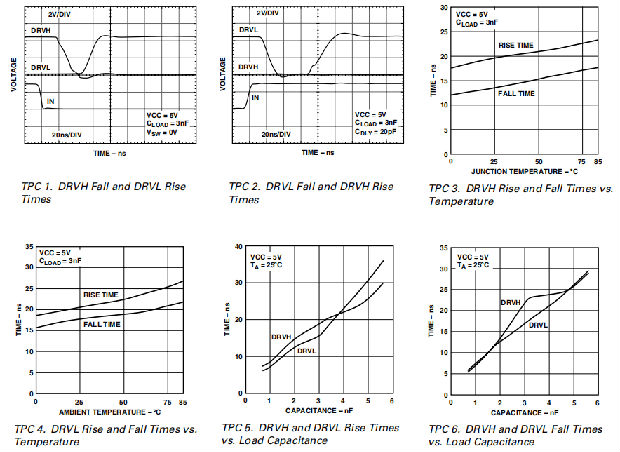

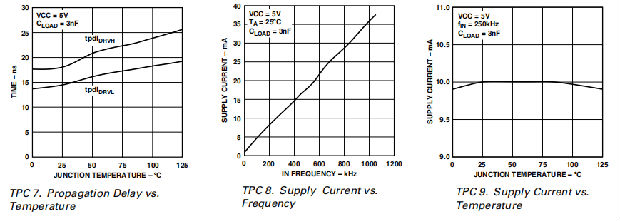

典型性能特征

操作理论

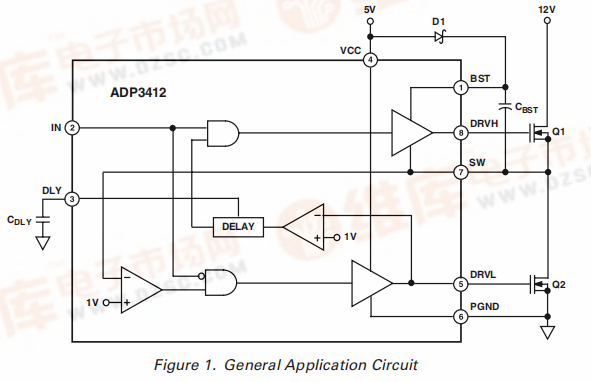

ADP3412是一个双MOSFET驱动器,用于驱动同步buck变换器拓扑中的两个N沟道MOSFET正确驱动高侧和低侧FET只需要一个PWM输入信号每个驱动器都能驱动3nf负载,转换时间仅为20ns。下面将更详细地描述ADP3412及其特性参见图1中的通用应用电路。

低端驱动器

低端驱动器设计用于驱动低rds(on)n通道莫斯费特驱动电源和下沉栅极电流的最大输出电阻为5Ω。低输出电阻允许驱动器在3nF负载下有20ns的上升和下降时间对低端驱动器的偏置在内部连接到VCC电源和PGND。

驱动器的输出与脉宽调制输入相差180度。

高端驱动器

高端驱动器设计用于驱动浮动低RDS(ON)N沟道MOSFET驱动电源和下沉栅极电流的最大输出电阻为5Ω。低输出电阻允许驱动器在3nF负载下有20ns的上升和下降时间。高压侧驱动器的偏置电压由外部自举电源电路产生,该电路连接在BST和SW管脚之间。

引导电路包括二极管d1和引导电容cbst。当ADP3412启动时,开关管脚接地,因此引导电容器将通过D1向VCC充电。当PWM输入变高时,高压侧驱动器将通过从CBST中抽出电荷开始打开高压侧MOSFET,Q1当Q1打开时,SW引脚将上升到VIN,迫使BST引脚达到VIN+VC(BST),这是足以保持Q1打开的门到源电压为了完成这个循环,Q1通过将栅极拉低到SW引脚的电压来关闭当低端mosfet q2打开时,sw引脚被拉到地上。这允许引导电容器再次充电到VCC。高压侧驱动器的输出与脉宽调制输入同步。

重叠保护电路

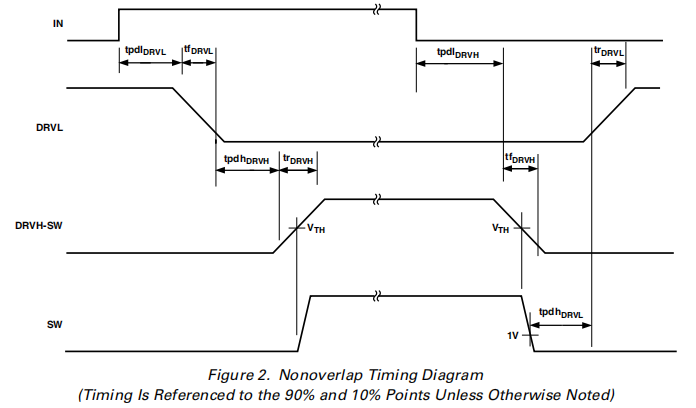

重叠保护电路(opc)防止主电源开关q1和q2同时打开。这样做是为了防止穿透电流流过两个电源开关,以及在开关转换期间可能发生的相关损耗重叠保护电路通过自适应地控制从Q1关闭到Q2打开的延迟,并通过外部设置从Q2关闭到Q1打开的延迟来实现这一点。

为了防止在Q1关闭和Q2打开期间栅极驱动器重叠,重叠电路监视开关管脚处的电压。当PWM输入信号变低时,Q1将开始关闭(在传播延迟之后),但在Q2可以打开之前,重叠保护电路等待SW pin处的电压从VIN降至1v。一旦SW pin上的电压降至1v,Q2将开始打开通过等待sw引脚上的电压达到1v,重叠保护电路确保q1在q2打开之前关闭,而不管温度、电源电压、栅极电荷和驱动电流的变化。

为了防止在q2关断和q1开断期间栅极驱动器的重叠,重叠电路提供由dly引脚上的电容器设置的可编程延迟。当pwm输入信号变高时,q2将开始关闭(在传播延迟之后),但在q1能够打开之前,重叠保护电路等待drvl处的电压降到vcc的10%左右。一旦DRVL处的电压达到10%点,重叠保护电路将等待20 ns的典型传播延迟加上基于外部电容CDLY的附加延迟延迟电容器额外增加1ns/pf的延迟。一旦可编程延迟期结束,Q1将开始开启。延迟允许电流从Q2的体二极管交换到外部肖特基二极管的时间,这允许降低关断损耗虽然不像自适应延迟那样万无一失,但可编程延迟增加了一个安全裕度,以考虑外部功率mosfet在尺寸、栅极电荷和内部延迟方面的变化。

应用信息电源电容器的选择

对于ADP3412的电源输入(VCC),建议使用一个本地旁路电容器来降低噪声并提供一些峰值电流。使用1μF低ESR电容器。多层陶瓷芯片(MLCC)电容器提供低ESR和小尺寸的最佳组合,使陶瓷电容器尽可能靠近ADP3412。

自举电路

引导电路使用电荷存储电容器(CBST)和肖特基二极管,如图1所示。这些元件的选择可以在选择高边mosfet之后进行。

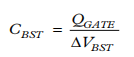

自举电容器必须有一个额定电压,能够处理最大的电池电压加上5伏特。建议最低额定电压为50 V。电容通过以下公式确定:

其中,QGATE是高压侧MOSFET的总栅电荷,而∏是高压侧MOSFET驱动器上允许的电压降例如,irf7811的总门电荷约为20nc。对于200 mV的允许压降,所需的自举电容为100 nF。应使用高质量的陶瓷电容器。

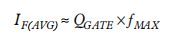

一个肖特基二极管被推荐用于自举二极管,因为它的低正向下降,最大化了用于高侧MOSFET的驱动器。自举二极管必须具有最小40 V额定值,以承受最大电池电压加上5 V。平均正向电流可以通过以下来估计:

其中fMAX是控制器的最大开关频率。应在电路中检查峰值浪涌电流额定值,因为这取决于5V电源的源阻抗和CBST的ESR。

延迟电容器的选择

延迟电容器CDLY用于在低侧FET驱动器关闭和高侧驱动器开始打开时添加额外的延迟延迟电容器在20 ns固定延迟的基础上增加1 ns/pF的附加时间。

如果需要延迟电容器,请寻找具有NPO或COG介质的高质量陶瓷电容器,或寻找高质量云母电容器这两种类型的电容器在1-100 pf范围内可用,并且具有优异的温度和泄漏特性。

印刷电路板布局注意事项设计印刷电路板时,请遵循以下一般准则:

1、找出高电流路径并使用短而宽的路径来建立这些连接。

2、将ADP3412的PGND引脚尽可能靠近下部mosfet的电源。

3、VCC旁路电容器应尽可能靠近VCC和PGND引脚。

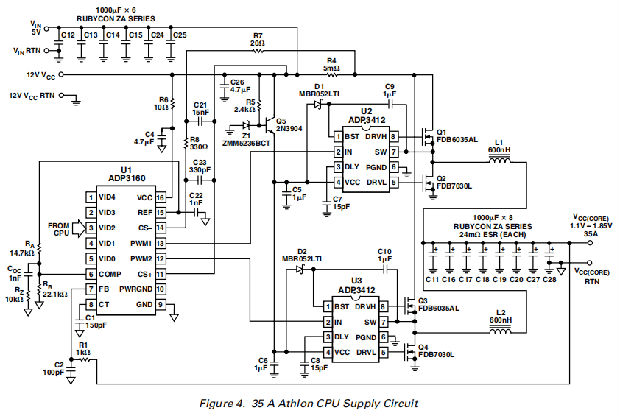

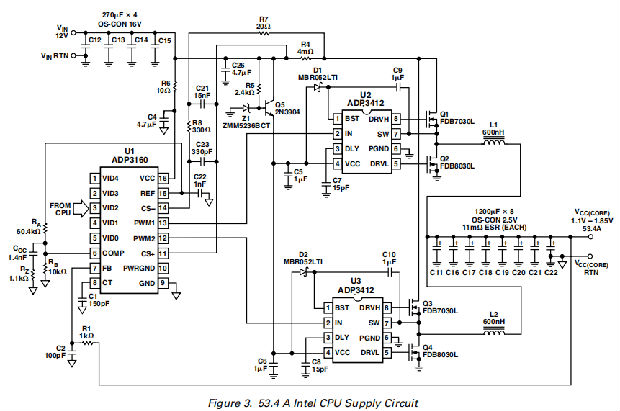

典型应用电路

图3中的电路显示了如何将两个驱动器与ADP 3160相结合,形成用于在大电流GOA计算机中生成VCC(核心)的总功率转换解决方案图4给出了35A处理器的类似应用电路。