10064点击型号即可查看芯片规格书

768点击型号即可查看芯片规格书

256kbit(32k×8)串行(spi)f-ram

特征 :64 kbit/256 kbit铁电随机存取存储器(F-RAM)10064;逻辑组织为8K×8(FM3164)/32K×8(FM31256)高耐久性100万亿(1014)读/写151年数据保留期(见数据保留和耐久表)nodelay8482;写入先进的高可靠性铁电工艺高集成度设备可替换多个部件串行非易失性存储器实时时钟(RTC)低压复位早期断电警告/NMI两个16位事件计数器带写锁的序列号,以确保安全实时时钟/日历2 V时的备用电流:1.15∏A,+25∏C秒,以BCD格式持续数个世纪追踪跨越2099年的年份使用标准32.768 kHz晶体(6 pF)软件校准❐支持备用电池或电容器处理器伴侣VDD和看门狗的有效低复位输出可编程低VDD复位跳闸点❐手动复位滤波和去噪可编程看门狗定时器❐双电池事件计数器跟踪系统入侵或其他事件电源故障中断比较器带锁的64位可编程序列号快速2线串行接口(I2C)高达1兆赫的频率支持100 kHz和400 kHz的传统计时RTC,通过I2C接口控制的主管设备为最多4个存储设备选择管脚低功耗1兆赫时1.5毫安有功电流150μA备用电流工作电压:VDD=2.7 V至5.5 V工业温度:–40℃至+85℃??14针小外形集成电路(SOIC)封装符合有害物质限制(RoHS)

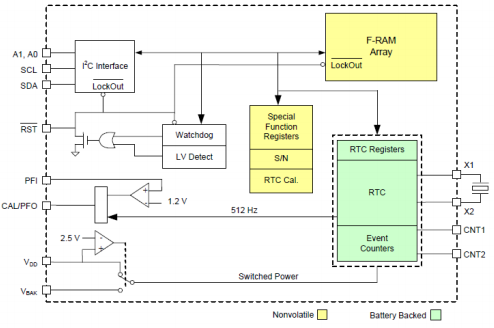

功能概述 :fm3164/fm31256设备集成了f-ram存储器和基于处理器的最常用功能系统。主要功能包括非易失性存储器、实时性时钟,低VDD复位,看门狗定时器,非易失性事件计数器,可锁定的64位序列号区域和通用可用于电源故障(NMI)中断或任何其他目的。fm3164/fm31256是64 kbit/256 kbit非易失性存储器采用先进的铁电工艺。铁电体随机存取存储器或F-RAM是非易失性的类似于ram的读写操作。这段记忆真的不易挥发,而不是电池供电。它提供可靠的数据保留151年,同时消除复杂性,其他原因引起的开销和系统级可靠性问题非易失性记忆。FM3164/FM31256能够支持1014个读/写周期,或1亿倍以上的写操作比EEPROM周期。实时时钟(RTC)在BCD格式。它可以从外部永久供电备用电压源,电池或电容器。这个计时器使用普通的外部32.768khz晶体和提供校准模式,允许软件调整计时准确。处理器伴侣包括通常需要的CPU支持功能。监控功能包括复位输出由低VDD条件或看门狗控制的信号超时当VDD低于可编程阈值,并在100毫秒后保持激活状态VDD高于触发点。可编程看定时器从100毫秒到3秒看门狗定时器是可选的,但如果启用,它将断言重置信号100毫秒,如果没有在超时之前由主机重新启动。标志位表示重置源。pfi上的比较器将外部输入引脚与车载1.2V参考电压。这对于生成电源故障中断(NMI),但可用于任何目的。这个系列还包括一个可编程的64位序列号可以锁定使其不可更改。此外,它还提供了电池备份事件计数器,跟踪上升或在专用输入引脚上检测到下降边缘。

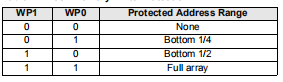

简介:fm3164/fm31256设备结合了一个串行非易失性带有实时时钟(RTC)和处理器伴侣的RAM。同伴是一个高度集成的外围设备,包括处理器管理器,用于早期断电的比较器警告、非易失性事件计数器和64位序列号。FM3164/FM31256集成了这些互补的单个包中公共接口下的不同函数。产品被组织为两个逻辑设备第一个是记忆和第二个是伙伴,包括所有剩余功能从系统的角度来看在串行总线上是两个具有唯一ID的独立设备。存储器被组织为独立的非易失性I2C使用标准设备ID值的内存。实时时钟和使用单独的I2C设备ID访问管理器功能。这允许在维护最近使用的内存地址。时钟和主管功能由25个特殊功能寄存器控制。这个RTC和事件计数器电路由电源维护VBAK引脚上的电源,允许它们从电池或当VDD低于设定阈值时,备用电容器功率。下面描述每个功能块。存储器结构FM3164/FM31256设备的内存大小可用64千比特/256千比特设备使用双字节寻址芯片的存储器部分这使得设备软件与独立的内存对应项兼容,但是它们在整个家庭中都是兼容的。存储阵列逻辑组织为8192×8位/32768×8位,使用工业标准I2C访问接口。存储器采用f-ram技术。因此,可以将其视为RAM,并在I2C总线的速度,写操作没有延迟。它也提供有效的无限写耐力非易失性存储器技术描述了I2C协议存储器阵列可以由软件进行写保护两位在处理器配对区域(寄存器0bh中的wp1、wp0)控制保护设置根据设置,受保护的地址无法写入,I2C接口将无法向受保护的地址确认任何数据。特别的详细描述了包含这些位的函数寄存器下面。

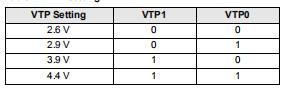

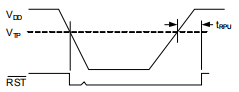

处理器配套除了非易失性RAM,FM3164/FM31256集成了实时时钟和高度集成的处理器同伴伴奏包括一个低VDD复位,一个可编程看门狗定时器,电池供电事件计数器,用于早期电源故障检测的比较器或其他用途和64位序列号。处理主管主管提供主机处理器两个基本功能:电源故障检测与看门狗定时器以逃避软件锁定条件。FM3164/FM31256具有复位引脚(RST)以在电源故障、通电和软件锁定这是一条明渠弱内部上拉到VDD的输出这允许其他重置电源线或连接到第一个管脚。当VDD高于编程触发点,RST输出弱拉至VDD。如果VDD下降到重置跳闸点电压水平(VTP)以下,RST销子将被压低它将一直保持在低位,直到VDD降得太低用于VRST级别的电路操作。当VDD上升时再次高于vtp时,rst至少继续低驱动100 ms(trpu)以确保在可靠的vdd下可靠的系统复位水平当trpu被满足后,第一个pin将返回到弱高级状态。在断言rst时,串行总线活动被锁定即使在VDD降到VTP以下时发生了事务,也会退出。一个当VDD高于VTP时启动内存操作内部完成。下表显示了位VTP(1:0)如何控制低VDD复位。它们位于寄存器0Bh的位1和0中。当VDD低于选定的VTP时,复位引脚将低驱动电压,I2C接口和F-RAM阵列将被锁定出去。图说明了响应于低视频显示器。

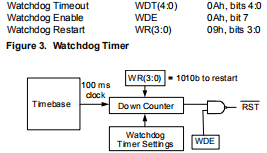

看定时器也可用于驱动主动复位信号。是一个自由运行的可编程定时器。这个超时时间可以在100 ms到3之间进行软件编程第二个在100毫米内通过5-bit非易失性寄存器增量。编程设置为最小值和最小值。根据操作规格的温度。茶监视器有两个附加控制操作,一个可用的手表位(WD)和时间恢复位两者都必须设置,而监视器必须设置。时间在命令驱动RST激活。复位事件时间将自动恢复在复位边缘脉冲如果WDE==0,监视器时间运行,但监视器故障不会因为被征服的低收入世界贸易组织旗帜将是Set,indicating a watchdog fault.这个设置在使用中。软件开发如果开发人员不想驱动设置最大时间设置的说明Disable the Counter to Save Power.第二个控制是Nibble that restarts the time preventing a reset.时间应该在时间价值发生变化后保持原状。注册0AH,比特4:可操作的监视器是7位。守望者被困住了。将模式1010b写入寄存器09H的下一个Nibble。写入此模式也会导致新的时间负荷。价值写入此地址的其他模式不会影响到它操作注意观察时间是自由的。优先于创建它,用户应按上面描述的时间限制。这就保证了,所有的时间都将立即到位。在Enabling之后当VDD在VTP下面时,监视器会失灵。

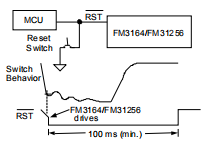

手动复位RST是一个双向信号,允许FM3164/FM31256过滤和反跳手动复位开关。RST输入检测外部低电平状态并通过驱动RST信号低达100毫秒。

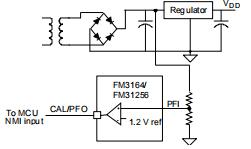

重置标志在重置条件下,将设置一个标志位来指示重置源。低vdd复位由por标志指示,寄存器09H,位6。监视程序重置由WTR标志指示,寄存器09h,位7注意,标志是在内部设置的对重置源的响应,但它们必须由用户清除。读取寄存器时,如果这两种情况都发生在用户上次清除它们之后。早期断电比较器可以为处理器提供早期电源故障警告在VDD退出规范之前。比较器用于创建电源故障中断(NMI)。这可以通过电阻分压器。应用电路如下所示。

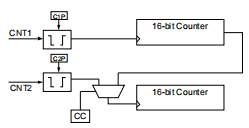

将pfi输入引脚上的电压与板载1.2v电压进行比较参考资料。当pfi输入电压低于此值时阈值,比较器将驱动校准/功率因数输出引脚至低国家比较器具有100 mV(最大)的滞后以减小噪声灵敏度,仅适用于上升的pfi信号。因为一个坠落的pfi边缘,没有迟滞。比较器是一种通用器件及其应用不限于NMI功能。比较器未集成到特殊功能中寄存器,除非它与校准输出共享其输出管脚。当通过设置校准调用RTC校准模式时位(寄存器00H,位2),CAL/PFO输出引脚将用512赫兹方波和比较器将被忽略。自从大多数用户只在生产过程中调用校准模式,这对使用比较器。注:比较器输入PFI的最大电压为在正常工作条件下限制在3.75 V。事件计数器FM3164/FM31256为用户提供两个电池备份事件计数器。输入引脚CNT1和CNT2是可编程边缘探测器。每个时钟一个16位计数器。当边缘出现时,计数器将递增各自的寄存器。计数器1位于寄存器0dh和0eh中,计数器2位于寄存器0fh和10h。可以读取这些寄存器值当VDD高于VTP时,它们将随着时间的延长而增加作为有效的VBAK电源提供。要读取,请设置RC位(寄存器0ch,位3)到1。这是四张照片的快照计数器字节,即使出现计数也允许稳定值在阅读过程中。寄存器可以由允许要由系统清除或初始化的计数器。计数在写入操作期间被阻止。两个计数器可以是通过设置cc级联创建单个32位计数器控制位(寄存器0ch,位2)。级联时,CNT1输入将导致计数器增加。CNT2不用于此模式,应与地面连接。

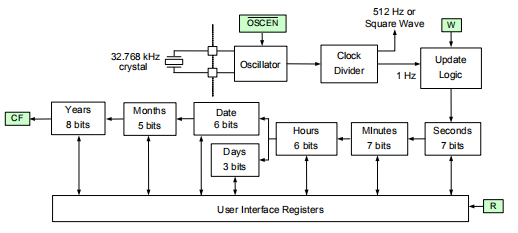

事件计数的控制位位于寄存器0ch中。计数器1极性为位c1p,位0;计数器2极性为位c2p,位1;级联控制为CC,位2;读取计数器位为RC,位3。极性位必须在设置计数器值之前设置。如果极性位改变,计数器可能会无意中增量。如果不使用埋头销,请将它们系在地面。序列号提供了用于写入64位序列号的存储器位置它是一个可写的非易失性内存块,可以由一旦序列号设置好,用户。8字节的数据和锁定位都是通过处理器的设备ID访问。因此序列号区域是独立的与内存数组不同。序列号寄存器可以写的次数不限,所以这些位置是通用存储器。但是,一旦设置了锁位,不能更改值,也不能移除锁。一次锁定序列号寄存器仍然可以被系统。序列号位于寄存器11h到18h中。锁定位是snl(寄存器0bh,位7)。将snl位设置为“1”将禁用写入序列号寄存器,而SNL位不能是变明朗。实时时钟操作实时时钟(RTC)是一种计时设备,可以永久供电的电池或电容器。它提供了一个软件校准功能,允许高精度。rtc由振荡器、时钟分频器和寄存器组成用户访问系统。它将32.768khz时基,提供秒(1赫兹)的最小分辨率。静态寄存器为用户提供对时间值。它包括秒,分,小时的寄存器,星期几、日期、月份和年份。框图说明了RTC功能。用户寄存器与计时器核心同步使用下面描述的寄存器00h中的r和w位。改变从“0”到“1”的R位从核心进入可由用户读取的保持寄存器如果当r被设置时,计时器更新挂起,那么核心将在加载用户寄存器之前进行更新。寄存器是冻结,直到R位清除为“0”。R用于读取时间。将W位设置为“1”将锁定用户寄存器清除为“0”使用户寄存器中的值加载到计时核心。W位用于写入新的时间值。用户应确保不将无效值(如ffh)加载到计时寄存器。对计时核心进行更新连续,除非锁定。

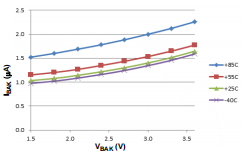

备用电源实时时钟/日历是永久性的动力十足。当主系统断电时VDD引脚将下降。当VDD小于2.5 V时,RTC(和事件计数器)将切换到VBAK上的备用电源。时钟以极低的电流工作以最大化。电池或电容器寿命。但是,结合F-RAM存储器的时钟功能是数据不会丢失不管备用电源是什么。IBAK电流随温度和电压变化(见直流电电气特性表)。下图显示了IBAK作为vbak的函数。这些曲线对于计算电容器用作VBAK源时的备份时间。

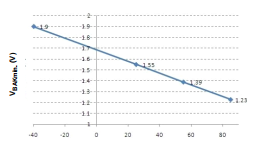

最低vbak电压随温度呈线性变化。这个用户可以期望最低VBAK电压为1.23 V+85°C和-40°C时为1.90 V。在+25°C时测试极限为1.55 V。注:最小VBAK电压的特征是-40°C和+85°C,但不是100%测试。

滴流充电器为了便于电容器备份,VBAK引脚可以选择提供涓流充电电流当VBC位(寄存器0Bh,位2)为设置为“1”,VBAK引脚将源于大约15μA直到VBAK。达到VDD或3.75 V,以较小者为准。在3V系统中,在没有外部二极管的情况下,将电容器充电至VDD电阻充电器在5V系统中,它提供相同的方便,并防止用户超过VBAK最大电压规格。在不使用电池的情况下,应系上VBAK引脚根据下列条件:对于3.3V系统,VBAK应与VDD连接。这是假定的VDD不超过3.75 V。对于5 V系统,将1μF电容器连接至VBAK,并转动打开滴流充电器。VBAK引脚将向内部充电备用电压调节到3.6 V左右。VBAK不应连接到5 V,因为VBAK(最大)规范将超过。一个1μF的电容器将保持功能工作大约1.5秒。尽管VBAK可能连接到VSS,但这不是如果使用同伴,建议使用。没有同伴功能将在2.5伏以下运行注:使用锂电池的系统应将vbc位清除为“0”以防止电池充电VBAK电路包括内部1K系列电阻器作为安全元件。当寄存器00h中的校准位设置为“1”时,时钟进入校准模式。在校准模式下,校准/功率因数输出引脚为专用于校准功能和电源故障输出暂时不可用。通过应用基于频率误差对计数器进行数字校正。在此模式下,CAL/PFO引脚以512 Hz(标称)驱动方波。

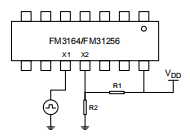

任何测量到的与512赫兹的偏差变成计时错误。用户转换测量的误差并将适当的校正值写入校准寄存器。表中列出了修正系数下面。正ppm误差需要负调整移除脉冲负的ppm错误需要正的增加脉冲的校正正ppm调整有CAL(符号)位设置为“1”,而负ppm调整将CAL设置为“0”。校准后,时钟将具有最大值。校准时每月误差为±2.17 ppm或±0.09分钟温度。校准设置存储在F-RAM中,因此不会丢失备份源失败。它是用位cal(4:0)在寄存器01h。只有当cal位为设置为“1”。要退出校准模式,用户必须清除校准位为“0”。当CAL位为“0”时,CAL/PFO引脚将恢复掉掉电输出功能。晶体振荡器晶体振荡器设计为使用6 pf晶体,无需需要外部组件,如加载电容器。这个FM3164/FM31256设备具有内置的加载电容器优化用于6 pf晶体。如果不使用32.768 kHz晶体,则外部振荡器可以是连接到FM3164/FM31256将振荡器应用于X1引脚它的高电压和低电压水平可以通过轨对轨或振幅低至约500 mV p- p以确保正确操作时,必须在X2引脚上施加直流偏压它应该在x1的高电平和低电平之间居中别针。这可以通过分压器来实现。

在本例中,r1和r2的选择使得x2电压以X1振荡器驱动电平为中心如果你愿意避免直流电流,您可以选择驱动带有外部时钟和X2,使用CMOS的倒时钟逆变器。布局建议x1和x2晶体管脚采用高阻抗电路连接到这些管脚的振荡器会被噪音打乱或者额外的装载。从信号中减少RTC时钟误差开关噪音,必须在这些衬垫周围放置一个护环护环接地。SDA和SCL痕迹应该是从X1/X2衬垫上引出x1和x2记录道长度应小于5 mm。使用地平面最好是背面或内板层。请参见布局示例。红色是顶层,绿色是底层。