256点击型号即可查看芯片规格书

FM25V02点击型号即可查看芯片规格书

特征 :256 kbit铁电随机存取存储器(F-RAM)逻辑组织为32k×8高耐久性100万亿(1014)读/写151年数据保留期(见数据保留和耐久表)nodelay8482;写入先进的高可靠性铁电工艺非常快速的串行外围接口(SPI)高达40兆赫的频率直接替换串行闪存和EEPROM的硬件支持SPI模式0(0,0)和模式3(1,1)复杂的写保护方案使用写保护(WP)引脚的硬件保护使用写禁用指令的软件保护1/4、1/2或整个阵列的软件块保护设备ID制造商ID和产品ID低功耗1 MHz时220μA有功电流90μA(典型)备用电流5μA睡眠模式电流低压运行:VDD=2.0V至3.6V工业温度:–40°C至+85°C■包装8针小外形集成电路(SOIC)封装8针薄双扁平无引线(DFN)封装符合有害物质限制(RoHS)

功能描述 :fm25v02是一个256kbit的非易失性存储器,采用先进的铁电工艺。铁电随机存取存储器或f-ram是非易失性的,执行读写操作。类似于公羊。它提供了151年的可靠数据保留在消除复杂性、开销和系统级别的同时串行闪存、eeprom和其他原因引起的可靠性问题非易失性记忆。与串行闪存和eeprom不同,fm25v02执行写操作以公共汽车速度行驶。不会造成写入延迟。数据是在每个字节之后立即写入内存数组已成功传输到设备。可以无需数据轮询即可开始。

另外,与其他产品相比,该产品具有相当大的写持久性非易失性记忆。FM25V02能够支持1014个读/写周期,或是1亿倍的写周期而不是eeprom。这些功能使FM25V02成为非易失性的理想选择需要频繁或快速写入的内存应用程序。示例包括数据收集,其中对于要求工业控制的地方来说,周期可能是至关重要的串行闪存或eeprom的长写时间会导致数据丢失。FM25V02为串行EEPROM或闪存作为硬件的替代品。这个FM25V02使用高速SPI总线,这增强了f-ram技术的高速写能力。装置包含一个只读设备ID,允许主机确定制造商、产品密度和产品修订。设备规格保证超过工业温度范围为-40°C至+85°C。

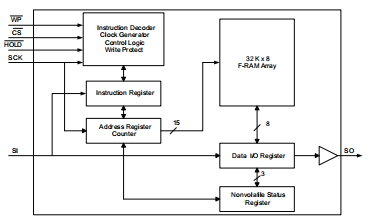

功能概述 :FM25V02是一个串行F-RAM存储器。内存数组是逻辑组织为32768×8位,使用工业标准串行外围接口(spi)总线。这个F-RAM的功能操作类似于串行闪存和串行EEPROM。FM25V02的主要区别具有相同引脚的串行闪存或EEPROM是f-ram具有卓越的写性能、高耐久性和低功耗耗电量。存储器结构当访问FM25V02时,用户地址为32K每个8个数据位的位置。这八个数据位移位连续进出。使用spi访问地址协议,包括芯片选择(允许多个设备在总线上),一个操作码和一个两字节地址。上部钻头地址范围的值是'don't care'。完整的15位地址唯一指定每个字节地址。FM25V02的大多数功能由SPI控制接口或由车载电路处理。访问时间内存操作本质上是零,超过时间需要串行协议。也就是说,存储器被读取或以spi总线的速度写入。不像连环闪光或EEPROM,无需轮询设备是否准备就绪条件,因为写入以总线速度发生。当一个新的总线事务可以转移到设备中,一个写操作已经完成。这在界面中有更详细的解释区域串行外围接口-SPI总线FM25V02是一个SPI从设备,运行速度加快到40兆赫。高速串行总线提供与spi主机的高性能串行通信。许多普通微控制器具有硬件SPI端口,允许直接接口。使用微控制器的普通端口引脚。

FM25V02在SPI模式0和3下运行。SPI概述SPI是一个四针接口,带有芯片选择(CS),串行输入(SI)、串行输出(SO)和串行时钟(SCK)引脚。spi是一个同步串行接口,它使用时钟和用于内存访问的数据管脚,并支持上的多个设备数据总线。SPI总线上的设备使用CS激活别针。芯片选择、时钟和数据之间的关系通过spi模式。此设备支持SPI模式0和3。在在这两种模式下,数据在上升时都被记录到F-RAM中从CS运行后的第一个上升沿开始的SCK边缘活跃。spi协议由操作码控制。这些操作码指定从总线主设备到从设备的命令。激活CS后,从总线传输的第一个字节master是操作码。根据操作码,任何地址和然后传输数据。CS必须在操作完成,然后才能发出新的操作码。spi协议中常用的术语如下:主端spi主设备控制spi总线上的操作。一个spi总线可能只有一个主节点和一个或多个从节点设备。所有的从站共用同一条SPI总线主设备可以使用cs pin选择任何从设备。全部的操作必须由激活通过将从设备的CS销拉低从设备。主人还生成sck和si上的所有数据传输所以线路和这个时钟是同步的。

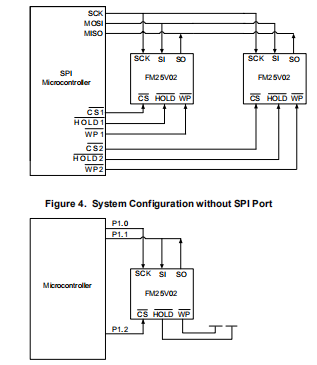

SPI从机主设备通过芯片激活spi从设备选择线条。从设备从spi获取sck作为输入master和所有的通信都与此同步时钟。spi从机从不在spi上启动通信总线,仅根据主机的指示操作。fm25v02作为spi从机运行,可以共享spi与其他spi从设备的总线。芯片选择(CS)要选择任何从设备,主设备需要下拉对应的CS引脚。任何指令都可以发给从机仅当CS引脚低时才使用设备。当设备没有选择,忽略通过si引脚的数据,串行输出引脚(SO)保持高阻抗状态。注:新指令必须从CS的下降沿开始。因此,每个活动芯片只能发出一个操作码选择“循环”。串行时钟(SCK)串行时钟由SPI主机和CS运行后,通信与该时钟同步低。FM25V02为数据启用SPI模式0和3沟通。在这两种模式下,输入被锁定由SCK上升沿上的从设备输出在下降边缘发出。因此,SCK的第一个上升沿表示spi指令的第一位(msb)到达斯宾。此外,所有数据输入和输出都是同步的带着SCK。数据传输(si/so)spi数据总线由两条串行数据线si和so组成沟通。si也被称为master out slave in(mosi)所以被称为主从出(miso)。这个master通过si pin向slave发出指令,而从机通过SO引脚响应。多个从设备可以共享前面描述的si和so行。

FM25V02有两个单独的针,用于硅和硫,它可以如图所示与主机连接。对于没有专用SPI总线的微控制器,可使用通用端口。减少硬件控制器上的资源,可以连接两个数据把销子(si,so)绑在一起,把固定销子和wp销子绑在一起。图显示了这样的配置,它只使用三个管脚。最高有效位(msb)spi协议要求传输的第一个位是最高有效位(msb)。这对地址和数据传输。256kbit串行f-ram对于任何读或写操作。因为地址只有15位,输入的高位被设备忽略。尽管如此位为“不在乎”,Cypress建议将此位设置为“0”以实现向更高内存密度的无缝过渡。串行操作码选择从设备后,CS变低,第一个接收的字节被视为预期操作的操作码。FM25V02使用标准操作码进行内存访问。无效的操作码如果接收到无效的操作码,则忽略该操作码,并且设备忽略si引脚上的任何附加串行数据,直到CS的下一个下降沿,SO引脚保持三态。状态寄存器FM25V02有一个8位状态寄存器。状态中的位寄存器用于配置设备。

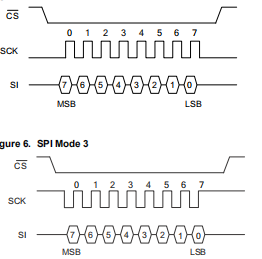

SPI模式FM25V02可以由带SPI的微控制器驱动外围设备以以下两种模式之一运行:spi模式0(cpol=0,cpha=0)spi模式3(cpol=1,cpha=1)对于这两种模式,输入数据在上升时锁定从CS运行后的第一个上升沿开始的SCK边缘活跃。如果时钟从高状态(模式3)开始,则第一个考虑时钟切换后的上升沿。输出数据在SCK的下降沿上可用。

两种SPI模式如第6页图5和图所示第6页第6页。总线主设备不在时的时钟状态传输数据是:模式0时SCK保持在0模式3的SCK保持在1设备从SCK引脚的状态检测SPI模式当通过降低CS引脚选择设备时。如果选择设备时SCK引脚低,SPI模式0为假设SCK引脚高,则在SPI模式3下工作。

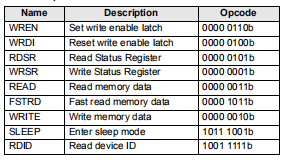

首次接入前通电在通电后的TPU时间内,无法访问FM25V02。用户必须遵守计时参数tpu,即从VDD(分钟)到第一个CS低的最短时间。指挥结构有九个命令,称为操作码,可以发出通过总线主机连接到FM25V02。它们列在表1中。这些操作码控制存储器执行的功能

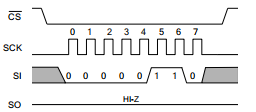

wren-设置写入启用闩锁FM25V02将在禁用写操作的情况下通电。鹪鹩命令必须在任何写操作之前发出。发送wren操作码允许用户发布后续操作码用于写操作。其中包括写入状态寄存器(wrsr)和写入内存(write)。发送wren操作码会导致内部写入启用要设置闩锁。状态寄存器中的一个标志位,称为WEL,指示闩锁的状态。wel='1'表示写入被允许。试图在状态寄存器中写入WEL位对该位的状态没有影响-只有鹪鹩操作码可以设置这个位。WEL钻头将在上升时自动清除wrdi、wrsr或write操作后的cs边缘。这可防止进一步写入状态寄存器或F-RAM没有另一个wren命令的数组。图说明了wren命令总线配置。

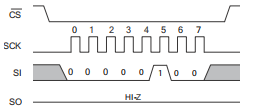

wrdi-重置写入启用闩锁wrdi命令通过清除写入启用闩锁。用户可以验证是否禁用了写入通过读取状态寄存器中的WEL位并验证Wel等于“0”。图说明了wrdi命令总线配置。

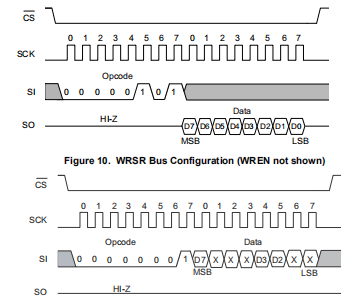

RDSR-读取状态寄存器rdsr命令允许总线主机验证状态寄存器的内容。读取状态寄存器提供有关编写保护功能。在RDSR操作码之后,FM25V02将返回一个包含状态内容的字节登记。wrsr-写入状态寄存器wrsr命令允许spi总线主机写入状态寄存器并通过以下方式更改写保护配置根据需要设置wpen、bp0和bp1位。发行前一个wrsr命令,wp pin必须为高或非活动。笔记在FM25V02上,wp只防止写入状态寄存器,而不是内存数组。在发送wrsr之前命令,用户必须发送wren命令才能启用写。执行wrsr命令是一个写操作,并且因此,清除写启用闩锁。

存储器操作SPI接口,它能够提供高时钟频率,突出了F-RAM技术的快速写入能力。与串行闪存和eeprom不同,fm25v02可以执行以总线速度顺序写入。所有写入内存的操作都以wren操作码和cs开头被断言和解除评价。下一个操作码是write。这个写操作码后接一个包含要写入的第一个数据字节的15位地址(a14-a0)记忆。忽略两字节地址的高位。后续字节是按顺序写入的数据字节。地址在内部递增,只要总线主机继续发布时钟并保持CS低。