WM8770点击型号即可查看芯片规格书

8226点击型号即可查看芯片规格书

说明

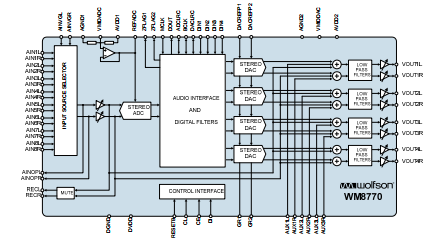

WM8770是一款高性能的多声道音频设备编解码器。WM8770是环绕声处理的理想选择家用高保真音响、汽车音响和其他音响的应用视觉设备。立体声24位多位Sigma-Delta ADC与八立体声声道输入选择器。每个频道都有模拟域静音和可编程增益控制。16-32位数字音频输出字长和支持8kHz至96kHz的采样率。四个立体声24位多位Sigma-Delta DAC与过采样数字插值滤波器。数字音频输入16-32位的字长和8kHz的采样率支持至192kHz。每个DAC通道都有独立模拟音量和静音控制,带一套允许选择外部3的输入多路复用器声道立体声模拟输入到这些音量控制。音频数据接口支持I2

S,左对齐和右对齐调整数字音频格式。设备通过3线串行接口控制。这个接口提供对所有功能的访问,包括通道选择、音量控制、静音、取消强调和增强管理设施。该设备有64线可用TQFP包。

特征

音频性能

-106dB信噪比('A'加权@48kHz)DAC

-102dB信噪比('A'加权@48kHz)ADC

DAC采样频率:8kHz–192kHz

ADC采样频率:8kHz–96kHz

3线SPI或CCB MPU串行控制接口

主从时钟模式

可编程音频数据接口模式-I2型S,左对齐或右对齐-16/20/24/32位字长

四个独立的立体声DAC输出模拟和数字音量控制

模拟旁路通道特性

音量控制的六通道可选辅助输入

8个立体声ADC输入,模拟增益可从+19dB至-12dB,1dB步进

2.7V至5.5V模拟,2.7V至3.6V数字电源操作

5V耐受数字输入

应用

框图

环绕声AV处理器和高保真系统

汽车音响

内部上电复位电路

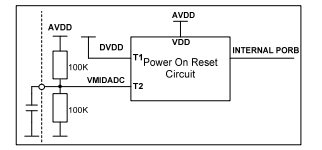

内部通电复位电路原理图

WM8770包括一个内部上电复位电路,用于将数字逻辑复位到开机后的默认状态。

内部por电路的示意图。por电路由avdd供电。这个电路监视DVDD和VMIDADC,如果DVDD或VMIDADC低于最小阈值vpor_关。

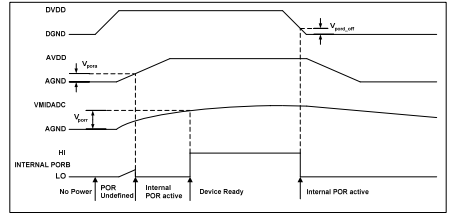

通电时,por电路需要avdd在场才能工作。porb被断言为低直到建立了avdd、dvdd和vmidadc。当avdd、dvdd和vmidadc已建立,porb高释放,所有寄存器都处于默认状态并写入数字接口可能发生。

断电时,每当DVDD或VMIDADC降到最小值以下时,PORB被断言为低阈值vpor_关。如果avdd在任何时候被移除,内部上电复位电路将断电,porb将跟随AVDD。

在大多数应用中,设备释放porb high所需的时间将由vmidadc节点的充电时间。

DVD在AVDD之前通电的典型通电顺序。

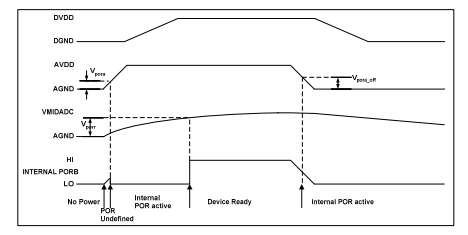

AVDD在DVD之前通电的典型通电顺序

在实际应用中,设计器不太可能控制AVDD和DVD。使用por电路监控vmidadc,确保在向设备通电,设备准备就绪。

实际系统中的典型通电场景。AVDD和DVD必须建立并且vmidadc必须已达到阈值vporr,设备才能准备好了可以写信给。在设备准备就绪之前对设备的任何写入都将被忽略。

在avdd之前dvdd正在通电。在这两种情况下,从通电到设备准备就绪的时间由电荷决定vmidadc的时间。

建议在vmidadc上使用10uf帽进行解耦。vmidadc的充电时间将控制设备通电后准备就绪所需的时间。所需时间对于vmidadc达到阈值是vmidadc电阻串和去耦的函数电容器。电阻串的典型等效电阻为50kohm(+/-20%)。假设10uf电容,vmidadc达到1v阈值所需时间约为110ms。

设备描述

一.导言

是一个完整的8通道DAC,2通道DC音频编码器,包括数字内插和解析滤波器,多位符号三角立体声ADC,和开关电容器多位符号三角洲在每个通道和输出平滑滤波器上具有类似体积控制的DACS。

该装置被实现为四个分离立体声DACS和一个具有柔性输入的立体声ADC。

多路复用器,在一个单个包中并由单个接口控制。四个立体声信道可以用来实现一个5.1信道外围系统。

附加立体声信道的立体声混频下载信道,或完整的7.1信道外围

系统

一个类似的BYPASS路径选项是可用的,以允许任何8个立体声模拟信号。

通过主体积控制,立体声输入到立体声输出。这纯粹地类似输入到类似输出高质量信号路径以实现如果需要的话。这将是Allow,for example,the user to play back a 5.1 channel surround movie through 6 of the DACS,whilst将一个分隔模型或数字信号放回远程房间安装。

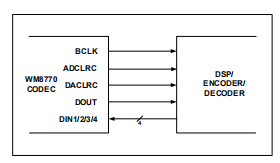

每个立体声DAC都有它自己的数据输入DIN1/文字时钟是共享的他们立体声ADC有自己的数据输出点,文字时钟。Bitclk and McLKAre shared between the ADCS and DAC.音频接口可以被配置为在这里操作。

硕士或斯拉夫式在斯拉夫模式ADCLRC中,DACLRC和BCLK是全部输入。大师模式ADCLRC、DACLRC和BCLK是全部输出。

ADC输入多路复用器被配置为允许大信号电平输入到ADC,使用外部电阻器降低正常操作范围内的大信号幅度OF the ADC.输入PGA还允许输入信号增益到+19DB并衰减下载到本发明允许使用ADC的用户最大灵活性。

一个可选择的立体声记录输出也被提供在直流/R上,并被认为是直流/R输出。

仅用于驱动高阻抗缓冲器。

每个DAC都有自己的模型和分离的数字卷控制。类似体积控制可调节的1DB步和0.5DB步的数字卷控制。模拟与数字Volume controls may be operated independently.加上一个零交叉检测电路每一个DAC用于模拟和数字卷控制。当类似体积零交叉检测是在输入信号到增益阶段时实现衰减值的唯一更新。

关闭类似地面水平。数字容积控制检测通过零的转变在增订卷之前这个小点击和拉链噪声作为增益值改变加上,6,DAC输出包含一个输入选择器和混频器分配一个外部6信道,或5.1信道信号,在DAC信号或在体积控制之前与DAC信号混合。此设备可作为6一种外部提供5.1类型类似输入的信道容积控制使用外部电阻器允许最大输入电平被器件接受,给予最大用户灵活性。设备内部功能的控制由3-wire串行控制接口进行。或CCB类型接口可以使用,可由CE PIN状态在Resetb的上升边缘上选择。控制接口可能与音频数据接口异步,作为控制数据将重新同步到音频处理

EC,CL,DI and Resetb are 5V controlerant with TTL Input Thresholds,allowing the WM8770 to usedWith DVDD=3.3V and be controlled by a controller with 5V output.提供了使用128fs、192fs、256fs、384fs、512fs或768fs的系统时钟的操作。在斯拉夫时钟率之间的模式选择是自动控制的。在主时钟模式下通过控制位粘合剂和DACRATE设置样品速率比。ADC and DAC may run at differentADC和DACS的普通大师时的约束下的鼠标。以…为例主时钟24.576MHz,一个DAC样品速率的96KHz(256fs模式)和一个ADC样品速率48khz(-512fs mode)can be accommadated.大师时钟.样品率(.FS)from less than 8ks//s up to提供适当的系统时钟是输入的。

音频数据接口支持右、左和i2接口格式

音频数据采样率

在典型的数字音频系统中,只有一个中央时钟源产生参考时钟所有音频数据处理都是同步的。这个时钟通常被称为音频系统的主时钟。外部主系统时钟可通过MCLK输入引脚直接应用无需软件配置。在一个有许多可能来源的系统中对于基准时钟,建议使用抖动最小的时钟源

优化ADC和DAC的性能。

WM8770的主时钟支持从256fs到768fs的DAC和ADC音频采样率,其中fs是音频采样频率(daclrc或adclrc),通常为32khz、44.1khz、48khz或96kHz(DAC还支持128fs、192fs和192kHz采样率下的操作)。主人时钟用于操作数字滤波器和噪声整形电路。

在从模式下,WM8770有一个主检测电路,自动确定主时钟频率与采样率之间的关系(在+/-32系统内时钟)。如果存在大于32个时钟错误,接口将被禁用并保持输出最后一个样本的水平。主时钟必须与ADCLRC/DACLRC同步,尽管WM8770可以容忍这个时钟上的相位变化或抖动。典型的masterWM8770的时钟频率输入。

WM8770的信号处理通常以128fs的过采样率对两者进行操作ADC和DAC。dac的例外是使用128/192fs系统时钟操作,例如。

对于192kHz操作,过采样率为64fs。对于96kHz的ADC操作建议用户设置adcosr位。这会改变ADC信号处理过采样率为64fs。

断电模式

wm8770具有断电控制位,允许关闭wm8770的特定部分不用的时候。8通道输入源选择器和输入缓冲区可能断电使用控制位ainpd。当AINPD设置为源选择器的所有输入时(AIN1L/R到AIN8L/R)切换到缓冲vmidadc。控制位adcpd关闭adc和adc输入四个立体声DAC各有一个单独的断电控制位,DACPD[3:0]允许单独的steteo dac在不使用时关闭。模拟输出混频器和EVR也可以通过设置outpd[3:0]关闭电源。输出[3:0]还可切换模拟输出VOUTL/R到VMIDDAC以保持输出上的直流电平。设置AINPD、ADCPD、DACPD[3:0]输出[3:0]将关闭除引用vmidadc、adcref和VMIDDAC公司。这些可以通过设置pdwn关闭。设置pdwn将覆盖所有其他断电控制位。建议8通道输入多路复用器和缓冲器、ADC、DAC和在设置PDWN之前,输出混频器和EVR断电。默认为所有断电要设置的位,PDWN除外。

断电控制位允许设备的某些部分在不使用时断电。为了例如,如果只需要从AINL/R到VOUTL/R的模拟旁路路径,则ADCPD和可设置DACPD[3:0]控制位,使模拟输入和模拟输出通电。

数字音频接口

主模式和从模式

音频接口以从模式或主模式工作,可使用MS控制位选择。在主模式和从模式DACDAT始终是WM8770的输入,ADCDAT始终是输出。默认为从属模式。

在从模式(ms=0)下,ADCLRC、DACLRC和BCLK是WM8770的输入。

DIN1/2/3/4、ADCLRC和DACLRC由BCLK上升沿的WM8770采样。模数转换器数据在DOUT上输出,在BCLK下降沿上变化。通过设置控制位bclkinvBCLK的极性可以反转,以便DIN1/2/3/4、ADCLRC和DACLRC在BCLK下降沿和BCLK上升沿陡变。

在主模式(ms=1)下,ADCLRC、DACLRC和BCLK是WM8770的输出

ADCLRC、DACLRC和BITCLK由WM8770生成。DIN1/2/3/4由WM8770位于BCLK的上升沿,因此控制器必须输出在BCLK下降沿。ADCDAT在DOUT上输出,在BCLK下降沿上变化。由设置控制位bclkinv可以反转bclk的极性,以便对din1/2/3/4进行采样BCLK下降沿和下降沿在BCLK上升沿发生变化。

主模式

音频接口格式音频数据通过数字音频应用于内部DAC滤波器,或从ADC滤波器输出接口。支持3种流行的接口格式:

8226;左对齐模式

•右对齐模式

•I2类

S模式

所有3种格式都先发送msb,并支持16、20、24和32位的字长,其中不支持32位右对齐模式的异常。

在左对齐、右对齐和i2中S模式下,数字音频接口在DIN1/2/3/4在DOUT上输入和输出ADC数据。每个立体声频道的音频数据是时间与ADCLRC/DACLRC多路复用,指示左声道或右声道是否存在。

adclrc/daclrc还用作指示数据开始或结束的计时引用。

在左对齐、右对齐和i2中S模式,每个DACLRC/ADCLRC的最小BCLK数句点是所选字长的2倍。ADCLRC/DACLRC必须至少高达个字长度为bclks,最小字长为bclks。上的任何标记空间比只要满足上述要求,ADCLRC/DACLRC是可接受的。

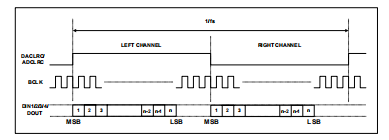

左对齐模式

在左对齐模式下,din1/2/3/4的msb由wm8770在DACLRC转换后的BCLK。ADC数据的msb在dout上输出,并在BCLK的下降沿与ADCLRC相同,可在BCLK的上升沿取样。

ADCLRC和DACLRC在左采样时高,在右采样时低。

左对齐模式时序图

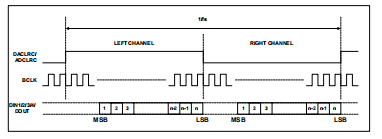

右对齐模式

在右对齐模式下,DIN1/2/3/4的LSB由BCLK上升沿上的WM8770采样在daclrc转换之前。ADC数据的LSB在DOUT上输出,并在在ADCLRC转换之前的BCLK下降沿,可在BCLK公司。左采样时ADCLRC和DACLRC高,右采样时低

右对齐模式时序图

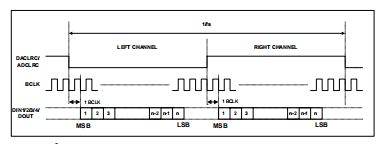

S模式

在I2中

S模式,DIN1/2/3/4的最大有效位由BCLK第二上升沿上的WM8770采样在daclrc转换之后。ADC数据的msb在dout上输出,并在ADCLRC转换后BCLK的第一下降沿,可在BCLK公司。ADCLRC和DACLRC在左采样时低,在右采样时高。

S模式时序图

控制接口操作

WM8770是使用三线串行接口在一个SPI兼容配置或CCB(计算机控制总线)配置。

接口配置由

复位引脚。如果重置B上升沿上的CE引脚低,则选择CCB配置。如果CE在resetb的上升沿上高,选择spi兼容配置。

控制接口允许5V电压,这意味着控制接口输入信号为CE、CL和DIDVDD为3V时,输入高电平为5V。输入阈值由DVDD决定。

resetb也具有5v的耐受性。