180点击型号即可查看芯片规格书

一般说明

FMS7401L是一种数字功率控制器,设计用于对基于模拟的实现要求易于数字控制的应用。FMS7401L是实现镇流器控制、电机控制和电池的理想解决方案管理职能。它集成了多种模拟具有8位微控制器核心的模块,提供高性能、低功耗和一个芯片的小尺寸FMS7401L用于使用电源的应用电压在2.7伏到3.6伏之间。它是用CMOS技术和全静态技术省电。FMS7401L有8针和14针PDIP、SOIC和TSSOP封装。

特征

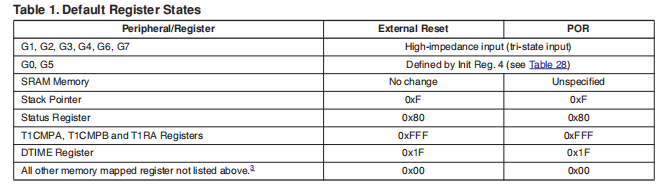

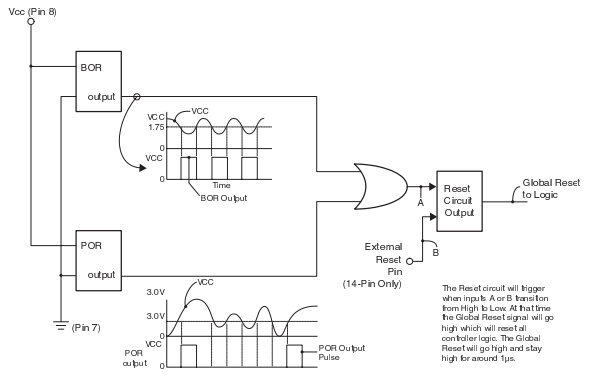

8位微控制器核心1K字节车载代码EEPROM64字节数据EEPROM64字节SRAM复位所有通用I/O引脚上的多输入唤醒带死区控制和半桥输出驱动的快速12位脉冲宽度调制定时器–输入捕捉模式5通道8位模数转换器–20微秒转换时间–采样并保持–内部参考电压(1.21V)–选通自动采样模式自动调零放大器(增益16)未承诺放大器内部电流源发生器(1毫安)片上振荡器–无外部组件–1微秒指令周期时间片上通电复位可编程读写禁用功能内存映射I/O可编程比较器(63级)棕色复位软件可选I/O选项带三态选项的推拉输出弱上拉或高阻抗输入全静态CMOS–节能停止模式–<1.3微安@3.3伏–省电空闲模式–<180微安@3.3伏单电源操作–2.7伏–3.6伏40年数据保留100000次数据更改8/14针PDIP、SOIC和TSSOP封装电路内编程–快速页面写入编程模式复位电路FMS7401L中的复位电路包含四个触发主系统复位的输入条件。当主系统复位时触发时,发生一系列事件,默认所有内存映射寄存器(包括初始化寄存器)和I/O它们的初始状态(见表1)。在系统复位过程中,指令核心执行暂停,允许内部振荡器和其他模拟电路要稳定。一旦系统重置顺序完成,设备将开始其正常操作是执行驻留在代码eeprom存储器中的指令程序。所需的时间要完成的系统重置顺序(treset)取决于单个触发条件,并在电气系统中定义数据表的特性部分。四种复位触发条件如下:上电复位(POR)外部复位1棕色复位(BOR)看复位2

1.1上电复位电路上电复位(por)电路将设备保持在复位状态,直到vcc达到足以保证设备正常工作的电压水平。por电路对不同的vcc斜坡速率敏感,并且必须在svcc内,如数据表的电气特性部分。当VCC下降时,POR电路不产生系统复位。此功能由brown out reset(bor)执行电路,必须由初始化寄存器1.4的boren位启用如果VCC不降到0V在下一个通电顺序之前,必须启用BOR电路和/或通过复位引脚11.2外部复位1如果不能使用por/bor电路正确重置应用程序中的设备。复位输入引脚包含一个内部上拉电阻器,使其成为一个有效的低信号。因此,要发布设备系统重置,在释放之前,重置输入应保持低电平至少10微秒(即返回到高状态)。当复位输入保持在低位时,内部振荡器和其他模拟电路保持在低功率状态降低设备的电流消耗(类似于停止模式的状态)。此外,I/O管脚都初始化为输入三态配置,除非另有规定。5在复位输入信号上升沿,主系统复位序列被触发释放内部振荡器和其他模拟电路,以便它们可以被初始化并开始正常操作。1.3棕色输出复位电路brown out reset(bor)电路是片上模拟比较器外设之一,必须通过初始化寄存器1.4的born位当vcc下降到以下时,bor电路用于保持设备在复位状态在数据表的电气特性部分定义的固定阈值。复位时,设备保持在初始状态直到VCC上升到固定/通电阈值以上。VCC上升到固定/通电阈值之后不久,启动内部系统重置序列。一旦系统复位程序完成,设备将开始正常工作执行代码EEPROM存储器中的指令程序的操作。在VCC缓慢上升和下降以及VCC不下降到0V的情况下,应使用BOR电路在恢复到设备的正常工作范围之前。bor电路可以看作是如果VCC不低于0.7V,则为Por电路。

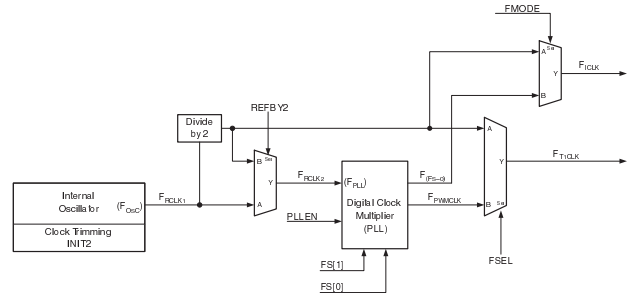

pscale寄存器4的fs[1:0]位为fpwmclk输出选择除法因子(见表3)。fs位可以是软件随时更改;但是,如果脉宽调制定时器1电路处于运行模式,则fs[1:0]值不会更改FPWMCLK输出频率,直到脉冲宽度调制周期结束(一旦TMR1计数器溢出)。上一个fs[1:0]值位于脉宽调制周期结束时间将指示下一个脉宽调制周期的fpwmclk输出的分割因子。当读取fs[1:0]时,报告的值将是软件写入的最后一个值(它可能不一定反映当前脉冲宽度调制周期)。主系统指令时钟(ficlk)源可以由内部振荡器(fosc)或pll的f(f s=0)输出提供使用与fs[1:0]=00选择相同的分割因子。6 pscale寄存器4的fmode位在f(fs=0)之间进行选择。(如果fmode=1)或frclk1除以2信号。在启用fmode位的情况下,可以以一定的速度执行指令比标准快8倍。如果未启用PLL,则无法设置fmode位。5任何尝试写入当pllen=0时,fmode将强制fmode=0忽略任何set指令。一旦启用PLL,软件可能在正常指令执行期间动态更改ficlk的源代码,以加速特定操作。为了同步禁用PLL时钟结构,软件必须在清除pllen位,以便成功禁用pll,例如使用单独的指令,如“rbit pllen,pscale”。还必须考虑停机/怠速节能模式的特殊条件。

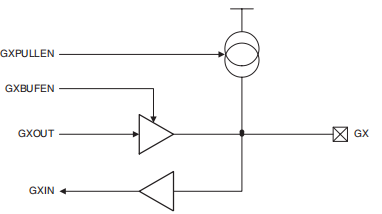

八个I/O引脚(8引脚封装选项上的六个)是双向的。双向I/O引脚可以通过软件单独配置,作为高阻抗输入、弱上拉输入或推拉输出。这个操作状态由数据和配置寄存器中相应位的内容确定。每个双向I/O引脚可用于通用I/O,或在某些情况下,用于由芯片决定的特定替代功能硬件。

多输入唤醒电路:多输入唤醒(MIW)电路可用于用外部事件将设备从停止或空闲模式1唤醒,通过任何一个或所有I/O端口(g0–g7)生成用于软件监控和微控制器硬件中断的标志。军情局使用唤醒启用(wken)、唤醒边缘(wkedge)、唤醒挂起(wkpnd)和t0cntrl内存映射寄存器。2 wken、wkedge和wkpnd是8位寄存器,其中每个位对应于I/O端口引脚(见表21)。所有四个寄存器在系统复位时初始化为0x00。pwmoff输出信号也可以编程为g6端口miw电路的输入。如果PWMOFF/G6输入MIW电路已启用并配置为触发其微控制器硬件中断(EDGEI)。DDELAY寄存器的第6位(pwmint)如果设置为1,则选择pwmoff信号来代替其对MIW电路的G6输入。然后,软件必须通过设置wken[6]位来启用miw pwmoff/g6电路。WKEDG[6]位也必须是清除此项可选择pwmoff信号的上升沿转换作为其wkpnd[6]位触发器。软件可以监视wkpnd[6]标记或启用miw硬件中断(edgei)以帮助检测何时触发pwmoff信号。参考到数据表的可编程比较器电路部分了解更多详细信息。9.1 MIW配置寄存器唤醒启用(WKEN)寄存器单独启用I/O端口的边缘转换以触发唤醒/中断挂起旗帜。如果wken寄存器位为1,则相应的I/O端口的MIW电路(由其位号定义)启用;否则,端口电路保持禁用状态,并且可能不会触发挂起标志。唤醒边缘(wkedge)寄存器位用于编程启用的I/O端口的挂起标志,该标志将从上升/下降边缘过渡。如果wkedge寄存器位为1,启用的I/O端口的下降沿转换将触发挂起标志。

如果为零,启用的I/O端口的上升沿转换将触发挂起标志。MIW电路在所有挂起标志之间共享一个硬件中断(EDGEI),并由唤醒中断启用t0cntrl寄存器的enable(wkinten)位。2如果设置了wkinten位,则为MIW电路启用硬件中断至1.3唤醒挂起(wkpnd)寄存器包含对应于每个I/O端口管脚的挂起标志。如果一个wkpnd寄存器位为1,编程I/O端口边缘转换已触发其挂起标志。如果为零,则标志不挂起并且为否从上次挂起的重置开始发生转换。挂起标志只能由启用的I/O端口触发(如果它的wken寄存器位为1)。一旦触发一个挂起标志,所有标志在逻辑上被“或”放在一起,以在处于“暂停/空闲”状态时触发唤醒模式和/或硬件中断(如果启用)。如果软件要重新进入暂停/空闲模式,则必须清除所有挂起标志,否则将忽略该命令。由于所有MIW挂起标志共享一个硬件中断,软件必须注意启用多个挂起标志时对挂起标志的处理。只要设置了MIW挂起标志,硬件中断将继续以最高优先级执行软件的MIW中断服务例程,直到所有挂起标志已清除。4在退出暂停/空闲模式或离开软件的MIW中断服务例程之前,可以使用RIT指令。

清除特定的挂起标志。rbit指令需要两个指令时钟周期来完成其执行。在第一个循环,所有8个寄存器位都会自动读取,以获得其最新值。在第二个循环中,要清除的位是给定它的新值,然后所有位被重新写入寄存器。使用rbit指令清除单个挂起标志如果仅启用一个唤醒I/O端口,则不会导致潜在危险。但是,如果启用了多个I/O端口,则软件可能如果触发器发生在RBIT指令的第二阶段,则无意中清除最近触发的挂起标志执行。为了避免这种情况,必须使用ld指令清除set pending标志。设计了miw电路这样,软件不能通过将1写入wkpnd寄存器位来触发挂起标志,只能将其清除。行动将1写入wkpnd寄存器位将保留当前位值。将0写入wkpnd寄存器位的操作将清除该位价值。因此,“ld wkpnd,0f7h”指令将清除wkpnd[3],而所有其他位保持不变。