640点击型号即可查看芯片规格书

特征

??ROM中的标准高性能功能

-杜比数字AC-3,5.1信道和2信道解码

每秒高达640 kbit

-杜比Pro逻辑编解码

-mpeg1和mpeg2双通道mpeg2译码pes流解析、pts解码和scr处理可下载的SiliconSoftware功能

-奥雷尔a3d,杜比虚拟环绕,哈曼vmax

-qsound qsurround,空间化器N-2-2家用THX

-srs trusurround,音乐模式

-低音管理和多声道混音柔性输入输出

-串行和/或并行数据流I/O

-串行SPI、串行Z2C或8位并行主机接口

-3个串行输入数据端口和4个串行数据输出端口

-格式化S/PDIF接收机,采样率高达96 kHz

-采样率:32 kHz、44.1 kHz、48 kHz或96 kHz

-格式化的s/pdif ac-3和mpeg发射机输出系统成本低

-无主机操作,无胶屑

-用于数字信号处理器核心和音频输入/输出的独立内部锁相环

-5.1杜比AC-3/MPEG2无需外部RAM

-低成本外部存储器的等待状态生成

-100针塑料四片式包装(PQFP)

-3.3 V电源,5 V兼容I/O,低功耗软件和硬件PC开发环境

-汇编程序/链接程序/模拟器

-带直接PC连接的片上冰支架

-带6个模拟输出的ZR38600DB演示板,麦克风和线路输入,以及可选的PC连接

说明

ZORAN ZR38601是一种高性能可编程数字器件

可实时单片机解码的音频信号处理器杜比数字AC-3 5.1声道和MPEG2数字环绕算法。这是佐兰制造的第四代解码器,基于已证实的ZR38000、ZR38500和ZR38600建筑。硬件块浮点优化用于杜比AC-3和复杂数字音频信号处理

应用。

由于其可编程的高性能和高水平的集成,ZR38 601在满足广泛的灵活性。

尽可能低的系统要求范围成本。在低端,它只需一个dac和一个用于s/pdif的光接口就可以提供标准的固定解码功能。

除了振荡器晶体之外的输入。在高端它可以提供八通道输出、模拟输入、长延迟存储器、自定义操作功能和升级能力使用下载的SiliconSoftware8482;产品增强功能。然而所有这些灵活性都没有设计复杂性。具有简单命令结构的高度可配置的标准功能最小化软件开发,同时进行全套开发工具可供高度定制的产品开发人员使用。

ZR38601主要适用于音频应用,例如

家庭影院音频/视频接收器,数字音频广播(DAB)、三维音频、六声道扬声器系统和卡拉OK处理器;主要是视频应用,如SDTV和HDTV立体声电视接收器、数字有线电视和卫星电视机顶盒

盒子;和多媒体应用,包括音频和视频像多媒体PC和数字视频磁盘(DVD)播放器。

一般说明

Zoran ZR38601是最新的数字音频处理

ZR38000高性能可编程控制器的成员数字信号处理器产品线。它是特别配置的具有外设、I/O功能和数字音频软件。

今天,高质量的数字音频从初级解码开始函数并添加适当的数据流协议和具有I/O配置的接口,以匹配应用程序。这个ZR38601具有这些主要的解码和协议软件功能,但还留有处理周期以用于附加的产品特征。ZR38601还具有系统I/O和硬件配置的灵活性。

ZR38601的管脚和指令集与较早的ZR38600,但具有较高的50-MIPS处理率和更大的内部程序和数据ram和rom。

新的96khz采样率s/pdif解码和增加处理周期和额外功能的存储器。新的硬件特点是一个可编程定时器,一个Z2C串行主机接口和对24位I/O数据格式的更多支持。

功能

ac-3和mpeg及其变体是目前使用的主要解码功能。ZR38601具有这些及其关联使用所需的设置、操作和系统测试功能使它们在最终用户产品中可用的函数。此外,越来越多的电子软件功能可以为产品添加特殊的增强和差异化功能。

解码音频输出最多可以是8个位串行通道来自S/PDIF的DAC格式或六个编码通道

发射器。

记忆

通常不需要外部存储器,但可以为程序和/或数字音频数据。附加程序存储在不使用主机时提供不同或附加的功能并允许选择用于未来可升级性。可能需要外部数据存储器具有长声学延迟、输入缓冲或大数据表。程序内存接口的字节宽度为提供最低成本和零件数量。功能描述下面将更完整地描述ZR38601软件的操作和配置及其硬件配置。

软件操作

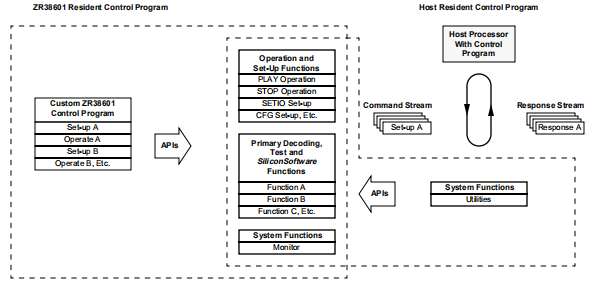

ZR38601的一个主要优点是易于使用系统开发人员对系统的需求范围很广。标准功能易于使用,但自定义功能可以添加而不必返回到具有复杂实时操作系统的自定义软件开发注意事项或详细的I/O协议。以下是所有软件功能都提供了用于主机或api的命令和响应序列(应用程序编程接口)用于从内部调用程序。每个都提供了在not只有一个,但取决于复杂性的一系列方式自定义函数的。

设置、主和硅片软件功能如中间。使用系统实用程序维护与主机的通信,主机可以发出一系列命令通过响应来控制ZR38601的操作。公用事业对函数发出api调用。所有的软件开发即使在功能操作中的变化类型基于获取信息从ZR38601的行动中回来。

或者,命令中的控制信息可以是在从自定义项发出的API调用序列中输入在ZR38601处理器上内部运行的程序。现在不行了主机是必需的。

对于主机命令/响应流或api调用,本机ZR38001代码中的自定义函数可以在没有在公共结构中失去易用性的好处。

标准的主要、操作和设置功能。注意这里有对ZR38601的读写命令和响应从ZR38601到主机。响应是由命令引起的在进行中的正常操作期间下面是带有读取命令的特定命令。

软件-功能

主要解码和测试功能

AC-3型

杜比数字ac-3解码器的主要工作模式功能总结见表2。选择用于输入和输出端口及其格式,包括音频/视频同步(AVS)、常量或请求驱动的PES操作封装输入与dvd的线性pcm。

AC-3输入解码速率高达每秒640 kbits。满的可选择扬声器配置、动态范围压缩、下混、延迟、滤波和错误隐藏策略。也支持卡拉OK混合。

包括下载的卡拉OK系数。

pcm+pro逻辑利用双通道PCM输入,功能的选择是四通道PRO逻辑解码或双通道立体声混频。可以选择扬声器配置,下混合,延迟和环绕滤波。

MPEG标准mpeg1解码器函数接受mpeg1或mpeg2输入流并生成Pro逻辑或双通道DAC形式的立体声输出。可选择扬声器配置,动态范围压缩,下混合,延迟以及环绕滤波。

粉红色噪音这是一个六通道粉红色(等能量每恒定比例带宽)伪随机噪声发生器测试函数。它是用于用户测试听力空间中的说话人平衡。六人组单个扬声器可以在单个可调电平,带或不带限带滤波器。SiliconSoftware功能

三维音频

有六家第三方供应商使用ZR38601号。这个函数提供了一个三维的效果只有两个扬声器的声场。这些经认证的功能是奥雷尔a3d,杜比虚拟环绕,哈曼vmax,qsoundQsurround、Spatializer N-2-2和SRS Trusurround。他们使用2或6通道输入和AC-3、MPEG根据收听区域使用的扬声器,可以想要改变低音频率的分布在演讲者之间。扬声器配置的选择是提供80、100或120的低通截止频率最简单的赫兹。全功能允许低通以及高通滤波器系数单个扬声器的音量。

低音管理与两个或六个声道输入一起工作以及AC-3、MPEG和Pro逻辑解码器。它不起作用虽然有些三维音频功能包括

某些低音管理功能。

DVD-线性动力系统控制模块除了音频/视频同步(AVS)和请求标准解码的驱动pes分组输入特性功能,此DVD功能具有3D音频功能和低音管理层。它适用于双、六或八通道的pcm输入和AC-3,MPEG和Pro逻辑解码器。

霍尔效应/音乐模式

使用此功能,可将短期和长期延迟和混响添加到多通道pcm输入中。延迟系数为下载以模拟各种声学环境(音乐厅、教堂、体育场等)家用THX5.1此功能用于连接到层叠,提供卢卡斯电影院的声音家庭听力环境。输入芯片运行所有标准解码功能,并将其pcm输出传递给用于THX5.1处理的第二个芯片,包括全低音管理、去相关、音色匹配和重新均衡以及单独可编程的信道延迟。

卡拉OK处理除了卡拉OK输入标准的混合特性外解码功能,这是真正的卡拉OK语音处理取消、音高变换、语音回声和混响以及低音管理。可能需要外部数据存储器这个功能。

自定义函数等。

用户函数允许开发人员使用自己的本地ZR38001代码轻松地添加自定义函数,同时保留了指挥和反应结构的控制

ZR38601号。

操作和设置功能总结的操作功能是系统控制一次所需的实时启动和停止命令已选择主解码功能。也包括是获取输入通道和解码状态的命令监控正在进行的操作。PTC和STC时钟可以还应进行监控,以确保音频和视频同步。

设置功能配置硬件和软件在操作开始之前或作为主要操作更改制造的。硬件配置和初始化包括锁相环(plls)、系统时钟和输入/输出(输入/输出)。软件可以通过主机处理器安装到位从它的I/O或内存系统。可能是习俗的形式命令及其参数或直接可执行的本机命令核心dsp处理器的代码。

系统功能

标准zr38601的其余部分用于在每个程序rom中都有系统功能

监视器

这是一个简单的实时操作系统小内核所有ZR38601功能正常运行。公用事业系统实用程序维护各种I/O接口的操作功能之间共享的。其中包括连续剧音频数据端口、串行SPI或Z2C主机接口和命令和响应的并行主机接口。这些实用程序还包括初始化和重置引导例程确定启动ROM并执行其初始化过程。

冰调试使用ZR38000系列进行电路仿真调试模拟器,监视器以单步和程序的断点执行。

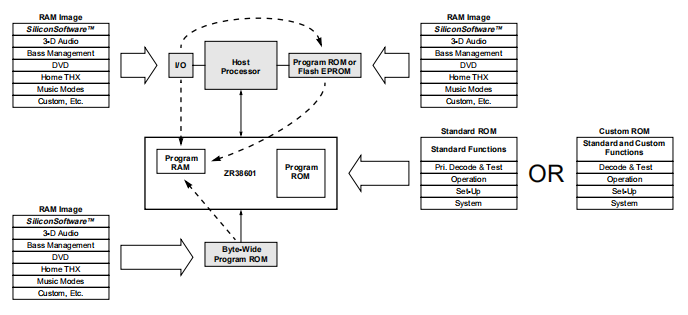

软件-系统配置由于ZR38 601的能力被配置为从低成本、固定功能的设备到非常灵活、全性能的音频。处理器,有很多软件的选择与系统硬件配置相关的配置。重要的注意事项是是否使用了主机使用标准命令。最常见的配置及其相对优势。

不同硬件配置的软件。从片上程序rom,可以是标准版本,也可以是具有如图所示的自定义函数。定制和电子软件功能可以下载到片上用虚线表示的三个源的程序RAM箭头。如果没有主机,则必须从外部加载字节宽的程序只读存储器。对于主机,它可能来自主机的拥有非易失性存储器(通常为rom或flash-eprom)或通过其I/O外围设备,如在线链接或可移动像软盘这样的内存介质。

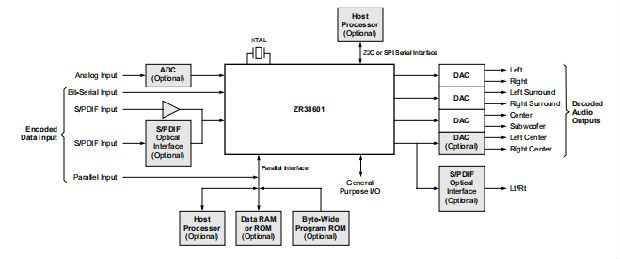

硬件-系统配置所有硬件,复合系统ZR38601。这个主机、数据输入和输出以及外部存储器的选择是总结见表5。那些得到带有标准命令的标准函数被记录下来。个别的矽软体功能支援额外的配置。例如,卡拉OK处理支持所需的位串行adc数据输入和外部数据ram用于音高校正和声音混响。

奥斯特

ZR38601的操作不需要主机微处理器。一种自定义程序,在内部rom或外部rom中rom采用标准的内部rom,就足够了。控制然后通过GPIO(通用输入/输出)端口进行操作。但是,如果使用主机,则最大的灵活性是可用的。这个外部硬件中成本最低的是串行主机接口。这个四线SPI(小型外围接口)或两线Z2C信号(见表6)直接连接到大多数低成本微控制器。主机串行接口没有速度惩罚它使并行接口可以与外部接口一起使用回忆。

ZR38601的并行接口可用于字节范围与微处理器主机的连接以及字节范围的I/O有标准的命令支持。全部16位如果调用了并行接口,则可以将其用于I/O连接开发者的软件。注意并行接口不能在使用主机和I/O时同时使用用于外部数据或程序存储器。

数据输入/输出主要数据输入是单线数字音频接口接收器。这完全符合S/PDIF、IEC-958、AES/EBU和EIAJ CP-340消费者标准。所有标准采样率支持原始或打包的比特流以及使用上的DREQ信号的数据驱动主操作GPIO0端口。串行端口A或字节宽并行接口可以交替地用作信道比特流的主或从。

并行接口也提供数据驱动的主操作,但不能与系统。

最多可输入6个位串行ADC数据通道作为主数据或在需要时以多种行业格式从机硅软件功能。

多达八个位串行DAC数据通道可以输出为相同行业格式的主从机,包括i2s和eiaj,具有字、帧和无帧同步。

端口B、C和D由标准6通道功能使用端口G另外还具有8通道硅软件功能。否则端口G用作S/PDIF主发射机。

外部存储器

并行端口的20个地址和16条数据线允许程序和数据存储用外部存储器的选择需要硅软件功能或未来的灵活性。

对于速度较慢、成本较低的存储器,支持可变等待状态。不与并行主机或I/O接口同时使用。

硬件-数字音频处理器ZR38601由接口、存储器和

ZR38001数字信号处理器核心周围的系统时钟如所示电源连接汇总在表6中。

该图说明了串行输出端口g与s/pdif发射机及其并行多功能用于外部主机、I/O和内存的端口如何利用未使用的16位内存数据线当并行字节宽接口为用于外部主机和I/O。

使用标准功能,六个GPIO信号中的三个专用于静音输入、I/O数据请求输出、DREQ和一个I/O错误输出,错误。

内部存储器很大:32位程序/数据ROM的20Kwords增加了可下载内存。只有数据的存储器是一个10 Kword RAM在20位数据字精度。

两个可编程锁相环(PLL),一个用于DSP核心(FDSP)和一个音频串行端口(FAUDIO)允许这两个关键内部时钟速率的独立选择。

当ZR38601系统振荡器不是由其自身的外部晶体决定,而是由预定的系统时钟频率。有两个pllsDSP核心同步工作在最大50 MIPS。

串行I/O时处理的速率(FDSP=100 MHz)以32、44.1、48或96 kHz的标准采样率工作,不管预定的系统时钟频率是否是公共子倍数。

电源电压为3.3伏以降低功耗,然而所有的I/O信号在5.0伏系统中都有5.0伏的耐受电压。

标准功能描述

ZR38601标准功能由

这些是否发送命令、参数和响应由微处理器通过串行主机接口接收,或使用并行主机时的并行主机接口。这个AC-3的应用程序接口(API),Pro逻辑,粉色噪音等功能相似。这些api由开发人员程序在核心处理器上执行。

主机和带有SPI的ZR38601之间的传输是全双工的,主机是主机。每发一个命令从ZR38601接收回一个字。与并行主机接口或串行Z2C接口为半双工和主人在一起。然后主机必须为发送每个命令后的响应。命令被发送只有从主机和是在一般形式显示。

有两类命令:对译码器和从译码器读回的那些。写作除了基本的操作代码。write命令有三种类型:选择主解码和测试的功能,控制操作的功能(如停止或播放)和那些设置操作

命令操作

本节介绍使用

命令结构及其配置选择。

启动

通过系统复位信号复位后,ZR38601将检查是否要加载外部程序rom。找不到这个会的从内部rom开始执行并等待来自主人。正常主机操作将确认ROM版本编号,然后配置ZR38601以匹配系统以及所需的操作。命令配置序列plltab,pllcfg,cfg是必需的,必须在任何解码功能选择。

pll配置两个锁相环(PLL)允许独立选择核心处理器时钟速率(fdsp)和串行数字音频各种系统时钟频率(fxti)的时钟速率(faudio)以及消息来源。图6显示了系统振荡器,两个plls、串行i/o分配器链和互连选择。它们由plltab、pllcfg和cfg命令。

plltab命令中的dspm和dspd字段确定核心处理器时钟速率,以允许处理性能和低功耗之间的选择更低的时钟频率。表10显示了一些具有代表性的值用于公共系统时钟频率。

plltab命令中的audm和audd字段确定i/o分配器的串行数字音频主时钟速率。

一些代表性和推荐值对于普通采样率和主时钟倍数。

输入/输出配置

cfg配置命令(见第17页)和setio命令(见第19页)确定数字输入和输出

配置。

与数据流输入、输出dac和单位通用寄存器通过输入/输出端口。有七个数字音频输入和输出端口(端口A、E和F是输入端口,端口B、C、D和G是输出)。有六个单位通用用户定义I/O端口:GPIO[5:0]。

串行端口

位串行端口服务于各种外围设备约定。它们的操作完全由cfg决定配置命令。输入端口组A(串行输入A,E、F)和输出端口组B(串行输出B、C、D和G)有单独的时钟系统,可以单独使用选择ZR38601作为主机或从机(端口F可通过端口组B的时钟系统激活)。这个系统时钟(FXTI),音频PLL锁定到系统时钟或s/pdif接收机可以产生主音频时钟。这可以用来生成两个内部输入和输出当它们是主控时的比特率时钟。

如果输入端口组A是主端口,则SCKA的频率为fa=fpsa/(2·spas),其中fpsa是音频时钟faudio。在spas等于1的情况下,fa等于fpsa。分隔器spas是cfg命令中的一个字段。同样,当输出端口组B是主端口,SCKB的率为fb=fpsb/(2·spbs),其中fpsb是内部音频时钟faudio或者通过sckin pin接收的外部时钟fsckin。在当spbs等于1时,fb等于fpsb。

输出是唯一的,当作为主时钟运行时输出也可以从外部提供的主设备导出带有可编程分频率SPB的时钟输入(SCKIN)。

此选择是使用cfg命令中的cb字段进行的。

数字音频接收器

ZR38601的数字音频接收器功能完全符合IEC-958、S/PDIF、AES/EBU和EIAJ CP-340用户模式接口标准。它会锁定传入比特流并提取时钟和数据信息。数据被提供给处理器进行解码和时钟按要求乘以256x或384x的采样率DACS。此主时钟信号可在sckin pin上使用

作为输出。

为了正确操作S/PDIF接收器,需要执行以下初始化步骤:

•应设置plltab命令中的audd变量到大约128×FXTI,其中FXTI是以MHz表示的时钟输入频率(即,如果FXTI=12.288 MHz)audd等于12.288x 128=1572的整数部分。对于256x或384x的采样率,audm应设置为4或6音频时钟输出。

•PLLCFG命令中的F1字段应设置为1。

•cfg命令中的sen字段应设置为1。

audm/audd、f3和spbs的其他代表值当使用s/pdif接收机时,各种采样率和主时钟率。他们是为了普通人选择24.576MHz的系统时钟频率(FXTI)。

数字音频发射机

ZR38601的数字音频发射机完全兼容带iec-958、s/pdif、aes/ebu和eaij cp-340用户模式标准。此功能允许传输数字音频比特流到外部解码器进行处理所有操作模式,即AC-3、MPEG或PCM。通过在cfg命令中设置spo位来启用发射机。这个iec-958要求的信道状态信息应为通过spdifcs命令提供给zr38601,S/PDIF信道状态SPDIFCS部分。它是为外部解码器设置信道状态位很重要正确操作。当S/PDIF输出启用时,第四个串行端口SDG被禁用。注意输出帧使用S/PDIF输出时,大小必须为32位(frb=1)。

通用港口有六个单位通用端口GPIO[5:0]通常配置为复位时的输入。GPIO5通常使用作为静音输入,GPIO0作为DREQ输出。GPIO1是通常是错误输出信号。通过在setio命令。输入管脚,定义为从gpio[5:0]输入进行采样并从gpio读取由主机用setio命令注册。同时它可以设置配置为输出管脚的管脚的状态。

解码器操作典型的解码器功能选择命令序列是:AC3,取消静音…静音…开始,取消静音…首先选择AC-3,然后切换到稍后的序言。如果在命令cfg中设置了drq位,命令序列必须包括播放:AC3,播放,取消静音…静音,停止…MPEG,播放,取消静音…

处理器一般说明

ZR38601的核心处理器具有多功能的内部结构、通用指令集和高速率。能够在很宽的范围内执行许多其他类型的算法各种各样的数字信号处理器应用。这些算法可以为基本的音频解码功能添加区分产品特征。

随着ZR38601的最先进的性能,这些额外的功能只需要很少的处理时间或程序内存。32位宽的允许设备执行大型并发操作数。例如,在一个指令周期可以执行以下操作:

•从寄存器中取出两个源操作数,执行算术运算并将结果存储在寄存器中。

•更新两个数据地址指针

•执行两个并行数据移动操作

•生成下一个程序地址

•获取下一个程序指令。

单个位和即时数据指令以及ZR38601的四级零开销循环和重复指令,产生非常紧凑的代码。大多数指令在一个循环。

ZR38601使用高达100 MHz的内部时钟速率每秒实现5000万条指令(50-MIPS)的性能。这允许每指令周期。一种内部可编程锁相环(PLL)乘法器/分配器电路允许任何外部晶体或要使用的输入时钟(在12-50兆赫范围内)。

ZR38601优化的20位(120分贝)数据精度使其特别适用于光盘质量的音频应用,包括音频均衡、特殊效果和音频在传统固定点DSP的16位数据精度不足的情况下进行混合。此外,通过为块浮点操作提供高性能支持来扩展动态范围(包括一个周期指数检测和两个基于ZR38601的系统固有的比仅通过扩展扩展扩展动态范围的24位精度定点DSP实现更经济有效数据精度。高性能块浮点是由于ZR38601的双向桶式换档器,此功能不可用在大多数传统的16位和24位定点DSP上。

为了简化编程并提高速度,ZR38601体系结构提供了一个通用数据寄存器文件,该文件可以最多提供四个源寄存器和两个目标寄存器根据指示。总共提供8个20位数据寄存器,两个寄存器扩展到48位用作累加器具有8位溢出保护的寄存器。

ZR38601还提供了一个双地址生成器和能够生成两个独立地址的寄存器文件每个指令周期。地址生成器支持模以及位反转寻址,另外还有一套完整的前置和后置修改寻址模式。

ZR38601具有许多内置内存资源。一个大的2K x除了

掩码中的许多编码功能可编程20k x 32位ROM。已经很大的内部10K x 20位数据RAM可以是通过16位外部数据总线和20位扩展片外总线内存地址总线,允许它寻址多达1M个数据字在统一的地址空间中。可编程等待状态可容纳低成本的慢速外部存储器和字节范围如果需要,配置可用于较低的芯片数。

处理器功能描述体系结构概述

ZR38601的详细功能单元处理器。数据路径由算术单元、用于数据的内存部分及其相关地址发电机组。控制路径是指令单元,用于程序的内存部分,及其相关联的程序序列单元。其余的是输入/输出端口和系统接口。

数据路径单元之间的数据流超过单个20位数据具有相应20位数据地址总线的总线。控制流在单个32位程序数据总线上20位程序地址总线。这些双重数据和地址总线被多路传输到较小的单个外部总线外部数据存储器。这种简单的节省空间的总线结构保持高性能,因为每个内部总线有两个每个指令周期的传输,每个单元都是独立的有自己的本地记忆。

ZR38601的高性能从

数据功能单元的功率及其伴随指令,并与控制功率相匹配功能单元及其说明。两者都是依次描述的。

数据和控制路径可以保证在由于快速互连的总线结构和控制两者的宽字指令集。这种观点按功能和指令操作可确认算术单位

运算单元使用全功能ALU(双向桶形移位器)执行处理器中的所有数据路径操作和一个20 x 20位的乘法器,都在多端口外工作注册文件。这七个端口允许两次传入或传出使用三个操作数乘法器和算术运算并行从内存中注册文件,包括存储结果指令周期。除了基本的二补算术和逻辑操作中,48位ALU还可以找到最小值和最大值,规范化,确定块浮点的指数,支持多精度并执行除法原语。一个进一步的精化是一个蝴蝶原语,它计算乘积和差使用辅助加法器。这个取四个操作数,进行乘法、加法和减法运算,并存储两个结果,有助于实现非常快速的4周期基数-2快速傅立叶变换蝴蝶。ALU结果设置适当的状态寄存器位系统接口,具有多个精度的粘性位以及阵列计算。一大类即时数据逻辑和算术指令释放寄存器空间并减少通信编码应用中常见的位操作中的指令计数。乘法器同时提供有符号和无符号操作在由模式寄存器中的ms位。这种分数分数对齐的移位保留了移位的最大42位乘积。这个48位桶式移位器同时进行逻辑和算术移位;模式寄存器中的SD位允许正移位运算符解释为向左或向右移动。第三个数据移位器在以下情况下提供算术移位、舍入和限制将数据从寄存器文件传输到数据总线上。这个从1位向右移动到2位向左移动的范围是由模式寄存器中的ds位决定。

寄存器文件(d0&d1)的八个寄存器中有两个是48位,其余6位是20位,并按中所示对齐一般来说,所有的算术单位运算都是隐式的数据溢出、受限、舍入或寄存器D2-D7相应地被截断。但是当d0或d1是源或目的地,则操作如下以便在这些寄存器中保留完整的48位精度结果。同样,使用数据总线进出d0和d1的传输是基于它们是48位操作数的扩展或缩减。这两个寄存器通常用作高精度累加器,是大多数信号处理算法的核心。

如果隐式操作数不是所需的操作数。地址生成单元从和读取由运算单元操作的数据还原到数据寄存器文件。注册文件位置是由操作字段中的寄存器字段直接寻址指示。对于内部和外部存储器和寄存器,直接寻址也可以使用,但地址生成单元的间接寻址是通常速度更快,程序内存效率更高。地址生成器可以为每个周期可进行两次总线传输,修改后相同同一指令周期中的两个地址。

生成的间接地址可以线性递增或用任意模m。这是在地址生成中完成的按地址alu(aalu)和地址寄存器文件计算的单位下一个地址是在修改后的操作中使用地址寄存器ax与索引寄存器ix的比较模数寄存器mx。汇编程序符号中的五种寻址模式是:注意:堆栈没有索引或循环寻址。指针sp。对于m=hex fffff,对应的a寄存器是以位反转的方式递增,用于执行基数2 fft。对于n点fft,递增索引寄存器必须是装载N/2。

地址寄存器文件可以在数据总线上访问,并且可用于通用寄存器。而且,他们可以从程序数据总线加载即时数据。

内存,它在数据总线上传输,并且仅从数据地址总线。它总是位于最低的内存中从十六进制00000到027FF的地址空间。其他的RAM和ROM宽32位,可同时用于数据和程序存储器。它们可由程序和数据地址总线和are源,以及ram目的地,用于数据和程序数据的传输公共汽车。当程序RAM被写入12位同时从数据总线扩展加载(dbx)寄存器。当程序ram作为数据读取时,dbx寄存器加载最有效的12位数据。这个dbx寄存器也可以作为通用寄存器加载或读取数据的最低有效位为12位。rom总是位于内存中hex e0000到e4fff的位置两个地址总线上的空间。标准ZR38601产品具有与数字音频解码器功能和用于接受来自主机或将操作程序从一个字节宽加载到RAM中外部ROM。注意外部ROM数据在D[11-4]上。程序/数据RAM始终位于十六进制d0000到两条地址总线上的内存空间均为d07ff。它提供快速内部存储器,无需使用内部编程的掩模当ZR38601与外部字节宽度一起使用时的ROM引导ROM或主机微控制器。

所有内部存储器都有一个端口,但与总线,每个指令都可以执行两个完整的操作循环。如果总线是可用。每个内部地址总线都有自己的地址空间,但由于内部记忆和外部记忆并不重叠内存共享一个公共地址总线,所有内存都可以被认为是在一个地址空间中内部数据总线是多路复用到一个较小的外部存储器总线。因此一次只能进行一次外部数据传输。也,每个指令周期只能进行一次传输到较慢的外部记忆。此内存周期时间可以是通过插入等待状态延长,以允许使用较低的成本缓慢的记忆。等待状态的数目由cfg命令,以便外部内存操作执行一个,三到七个指令周期。显示的地址是内部20位的。

可选的外部引导rom为8位宽,连接到d[11-4]。不同宽度的内存可用于如果需要,外部RAM。选项是8位或16位。数据必须在数据总线上左对齐。

复位和中断存储器位置复位和中断向量占用64个(十六进制40)位置的内存。可位于片上20K x 32位的最低部分OM或2K x 32位RAM。这是由模式寄存器如下:程序序列单元所有处理器操作都由解码指令控制在指令寄存器(ir)中。处理器的控制流程是呈现给ir的指令序列。这个程序序列单元通过生成从程序内存中获取指令的程序地址。

ZR38601中的这个单元也是一个强大的地址生成器,通常产生一个最小的长操作序列程序内存传输。这方面的例子是重复和循环指令,允许重复单个和多个无指令开销的指令。在除了这些说明外,控制流程的主要变化由重置操作、中断、分支和程序序列单元响应的子程序。复位和中断操作处理器的操作从系统断言重置PIN。当断言复位时,模式寄存器被设置设置为十六进制00038,状态寄存器设置为十六进制00000。这个串行端口数据寄存器和移位寄存器都被清除对于输出串行端口和串行端口移位寄存器指针被重置。模寄存器和循环结束寄存器被清除。程序计数器设置为十六进制e0000在无条件跳到重置开始之前重置并中断位置C指令分为八个类或位模式格式就是在这里ZR38601最为明显。前三个类提供了完整的运算单元的功能及其操作域(操作码和操作数),但同时执行并行操作。这个并行操作域(并行操作码和并行操作数)指定单次和双次、直接和间接传输源和目标以及地址生成修改操作。位指令也是并行操作。这个最后五类指令用于大字段直接数据传输和程序控制。

对于IV和V类,可能的源或目标寄存器是通用寄存器。对于并行操作,可能源寄存器和目的寄存器包括辅助寄存器。

以及普通登记册。

输入/输出端口

连接到外部存储器和外围设备通过输入/输出端口。有一个16位并行数据端口,8个串行数据端口和6个单位通用用途I/O端口(GPIO)。这些最后一个可以由作为输出或输入的用户。并行端口

ZR38601并行端口以两种不同的模式工作在复位时由引脚P/M选择。它可以作为数据并行端口,用于加载数据、指令和向芯片编程并从中读取状态和其他信息芯片,或者它可以作为外部存储器接口工作。这个外部存储器接口由20位地址总线组成A[19:0]、16位双向数据总线D[19:4]和控制信号CS、RD和wr。数据并行端口接口包括8位双向数据总线pp[7:0]和控制信号cs,rd,wr,err,c/d,rdy。RDY、C/D和ER信号是d[14:12],pp[7:0]也是d[11:4]。当控制外部存储器接口(P/M=0)时,CS是在访问外部内存时断言为低。rd在外部读取周期期间被断言,并且可以使用作为内存的输出启用。wr在外部写入周期,可用于记忆。

ZR38601可以生成等待状态以用于慢速使用cfg命令的wait字段的外部内存。在具有等待状态的访问周期内存接口信号的转换与在零等待周期中,但所有的都被指定的数字拉伸指指令时钟周期(1、3或7)。在没有外部数据的指令周期内访问,rd和wr信号未激活。然而,地址总线继续由内部指令驱动获取地址。

当选择并行I/O接口(P/M=1)时,内部fifo用于使主机能够以长脉冲写入数据。这个rdy输出信号指示fifo何时准备好接收更多数据(rdy=1)或fifo快满而没有准备接受数据(rdy=0)。错误信号是如果在

数据。C/D输入信号区分输入数据和使用hregin/hregout寄存器的指令或状态。当C/D=1传输为主机命令或应答状态时因此写入hregin寄存器或从hregout寄存器。当c/d=0时,则所有来自主机写入内部fifo。cs,rd和wr总是/M=1时输入。当断言reset时,地址和数据总线和控制信号cs、rd和wr都设置为高阻抗状态。

串行DAC和ADC端口串口在ZR38 601上灵活使用,服务范围广。

各种应用和外围设备。三个ADC输入和四个DAC输出可以不同地分组以共享两组通用控制信号,每一组为主控或奴隶。其他选择是字或帧同步,帧大小和16、18、20或24位字传输。一个主时钟输出,可在内部生成组可编程速率时钟。i2s格式,无帧时分复用(TDM)格式和LSB对正帧都支持EIAJ格式。

端口A、E、F总是ADC数据输入,而B、C、D是总是DAC数据输出。端口G可以是DAC数据输出或s/pdif发射机输出。它们可以配置为两个具有共享时钟的组:所有输入和所有输出,或作为两个使用“输出”组中的一个输入进行分组。这个选择由模式寄存器中的AB位构成。B组是唯一的在这种情况下,当作为DAC的源操作时,其时钟输出也可以从外部提供的主时钟导出输入(sckin)。

传输在比特率时钟(scka和sckb)的正或负向边缘,最有效的比特是先移入或移出双缓冲移位寄存器。文字边界由一个单位持续时间帧信号表示(fsa和fsb)对于每个字或交替的字信号(wsa和wsb)表示左声道或右声道,偶数或奇数一言为定。为每组单独选择信号类型16、18、20或24位的字长和帧大小每帧16到256位。状态中的单词select bits当左声道或右声道传输时,寄存器反射每一组。ws/fs信号可能由一个或非i2s格式的更多位间隔。每个组的已完成帧传输由矢量向处理器指示单独启用时中断。TDM例外一帧中每个字都有中断的地方。

每个组可以是辅助串行端口模式寄存器中选择的源或从。当一个信号源,时钟会是独立可编程的电路仿真接口

ZR38601的电路内仿真(ICE)能力通过四次测试提供硬件和软件调使用标准jtag接口的管脚(tdi、tdo、tck、tms)。此接口由片上程序/数据rom中的例程和最高优先级中断提供服务。这提供了硬件的寄存器和存储器读取和设置命令调试。三个断点地址检测寄存器和另外,两个带中断的计数寄存器为ICE中的实时程序调试功能提供了支持。重置和初始化处理器只能通过断言重置信号来重置外部输入引脚。在初始通电时,必须断言在适当的电源电压下,至少160个时钟周期操作条件。上升后运行16个周期边缘。通电后,任何重置都必须断言至少16时钟周期,但如果不需要,则小于128个时钟周期重置PLL。如果用户希望重置plls,则重置信号必须激活至少160个时钟周期。操作在所选重置服务的上升沿之后开始16个周期记忆中的常规位置。但是,处理器不会,接受串行主机命令并返回直到200的响应指令周期已过。为了让解码器操作正确,以下命令序列应提供:PLLTAB、PLLCFG、CFG、AC-3(如果AC-3模式为必需)取消静音。

复位后管脚的状态为三态或外部中断输入信号int是边缘敏感的,并且必须在两个时钟周期内保持断言以设置内部int旗帜。当中断服务程序启动时,此标志被清除,因此任何新的中断条件都必须允许int变高然后再次降低以生成另一个中断。

振荡器和时钟输入xti和xto信号共同为振荡器时钟fxti供电作为来自ttl系统时钟的输入或作为启用内部振荡器的晶体连接。最大值频率fxti为40mhz,最小为4mhz。内线锁相环(pll)由此产生一个dsp核心时钟FDSP。这个内部的数字信号处理器时钟可以在4-100兆赫的范围内。(对于低FDSP频率,应注意,因为spi数据速率按比例降低)。重置后,但是在PLL锁定之前,fdsp=fxti。

外部时钟应用于XTI,而外部晶体连接并联谐振基模晶体应与两个20pf电容器一起使用。