376点击型号即可查看芯片规格书

231点击型号即可查看芯片规格书

8226点击型号即可查看芯片规格书

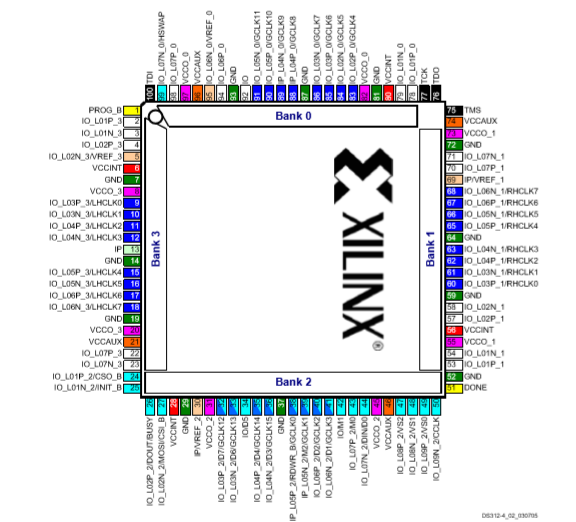

引脚说明封装概述引脚表示意图介绍

Spartan-3E系列现场可编程门阵列(FPGAs)是专门为满足高容量、成本敏感的消费电子应用而设计的。,五人家庭提供的系统门密度从100000到160万不等。

spartan-3e系列是在早期spartan-3系列的基础上,通过增加每个i/o的逻辑量,显著降低每个逻辑单元的成本。新功能提高了系统性能并降低了配置成本。这些SPARTAN-3E增强功能与先进的90纳米工艺技术相结合,提供了比以前更多的功能和每美元带宽,为可编程逻辑行业制定了新的标准。

由于成本极低,Spartan-3E FPGas非常适合广泛的消费电子应用,包括宽带接入、家庭网络、显示/投影和数字电视设备。

斯巴达3e系列是一个优于掩模编程asic的替代品。FPGA避免了传统ASIC的高初始成本、冗长的开发周期和固有的灵活性。此外,fpga的可编程性允许在不需要硬件替换的情况下进行现场设计升级,这在asic中是不可能的。

特点

非常低成本、高性能的逻辑解决方案,适用于大容量、面向消费者的应用,经验证的先进90纳米工艺技术,多电压、多标准SelectIO接口管脚-多达376个I/O管脚或156个差分信号对-LVCMOS、LVTTL、HSTL和SSTL单端信号标准-真正的LVDS,RSD,迷你LVDS差分输入输出3.3V,2.5V,1.8V,1.5V和1.2V的信号-增强双数据速率(DDR)支持-丰富,灵活的逻辑资源-密度高达33192逻辑单元,包括可选的移位寄存器或分布式RAM支持-高效率的广泛的多路复用器,宽逻辑-快速前瞻进位逻辑-带可选流水线的增强型18 x 18乘法器-ieee 1149.1/1532 jtag编程/调试端口,分层selectram内存结构-高达648 kbits的快速块ram-高达231 kbits的高效分布式ram,高达8个数字时钟管理器(dcms)-时钟偏差消除(延迟锁定环)-频率合成、乘法、除法-高分辨率相移-宽频率范围(5兆赫至300兆赫以上),每半个设备8个全局时钟和8个时钟,外加丰富的低偏差路由,与行业标准PROM的配置接口-低成本、节省空间的SPI串行闪存PROM-X8或X8/X16并行NOR闪存PROM-带JTAG的低成本Xilinx平台闪存,完整的Xilinx ISE,Webpack开发系统支持,Microblaze,PicoBlaze嵌入式处理器内核,完全兼容的32/64位33/66 MHz PCI支持,低成本QFP和BGA封装选项-通用封装支持轻松的密度迁移-无铅包装选项

体系结构概述

斯巴达3e系列结构由五个基本的可编程功能元件组成:

可配置逻辑块(CLB)包含灵活的查找表(LUTS),它实现逻辑加上用作触发器或锁存器的存储元件。clb执行各种各样的逻辑功能以及存储数据。输入/输出块(IOB)控制I/O引脚和设备内部逻辑之间的数据流。每个iob支持双向数据流和三态操作。支持多种信号标准,包括四种高性能差分标准。包括双数据速率(DDR)寄存器。块RAM以18kbit双端口块的形式提供数据存储。乘法器块接受两个18位二进制数作为输入并计算乘积。

数字时钟管理器(DCM)模块为分配、延迟、乘法、除法和移相时钟信号提供自校准的全数字解决方案。

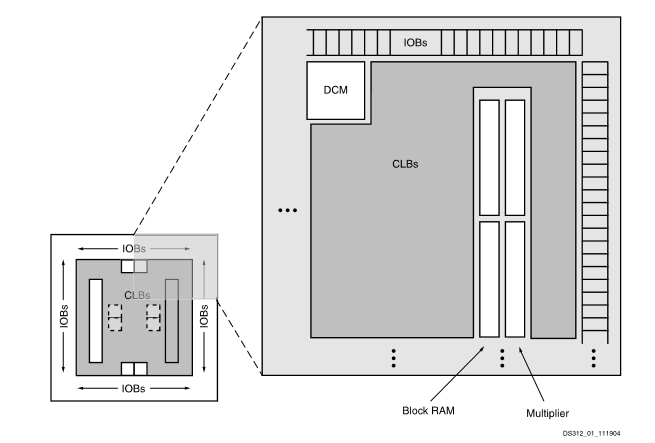

这些元素的组织如图1所示。一个iob环围绕着一个规则的clb数组。除了xc3s100e有一列之外,每个设备都有两列块ram。每个ram列由几个18kbit的ram块组成。每个块ram都与一个专用的乘法器相关联。DCM位于设备的中心,两个位于设备的顶部,两个位于设备的底部。xc3s100e的顶部和底部只有一个dcm,而xc3s1200e和xc3s160e在左右两侧的中间添加了两个dcm。

斯巴达3e家族拥有一个丰富的记录道网络,连接所有五个功能元件,在它们之间传输信号。每个功能元件都有一个相关的开关矩阵,允许多个连接到路由。

数字

配置spartan-3e fpgas通过将配置数据加载到健壮的、可重编程的静态cmos配置锁存器(ccls)中来编程,ccls共同控制所有功能元件和路由资源。fpga的配置数据存储在外部的prom或其它非易失性介质中,无论是板上还是板下。通电后,使用七种不同模式中的任意一种将配置数据写入fpga:

,来自Xilinx平台闪存PROM的主串行口,来自工业标准SPI串行闪存的串行外设接口(SPI),来自工业标准X8或X8/X16并行或非闪存的字节外设接口(BPI)从串行口,通常从处理器下载,从并行,通常从处理器下载,边界扫描(JTAG),通常从处理器或系统测试仪下载。

i/o功能spartan-3e fpga selectio接口支持许多流行的单端和差分标准。

Spartan-3E FPGAs支持以下单端标准:

3.3V、低压TTL、LVTTL,3.3V、2.5V、1.8V、1.5V或1.2V下的低压CMOS(LVCMOS)33 MHz和66 MHz下的3.3V PCI,1.8V下的HSTL I和III,通常用于内存应用1.8V和2.5V下的SSTL I,通常用于内存应用斯巴达3E燃气轮机支持以下不同标准:

LVD,总线LVD,迷你LVD,RSD

包装标识

BGA封装中Spartan-3E FPGas的顶部标记,但132球屑秤封装(CP132和CPG132)除外。bga封装的标记与四平板封装的标记几乎相同,只是标记相对于球a1指示器旋转。

CP132和CPG132封装中Spartan-3E FPGAs的顶部标记。

如架构概述中所述,Spartan-3E FPGA架构由五个基本功能元素组成:

输入/输出块(IOB)可配置逻辑块(CLB)和切片资源,块RAM,专用乘法器,数字时钟管理器(DCM)

以下各节提供了这些功能的详细信息。此外,本节还介绍了以下功能:

时钟基础设施,互连,配置,为Spartan-3e FPGas供电

输入/输出块(IOB)

IOB概述

输入/输出块(iob)在封装引脚和fpga内部逻辑之间提供可编程、单向或双向接口。IOB与斯巴达-3家族相似,但有以下区别:

只添加输入块8226;可编程输入延迟添加到所有块•DDR触发器可在相邻IOB之间共享

单向仅输入块具有完整iob功能的子集。因此,输出路径没有连接或逻辑。以下段落假设对输出功能的任何引用不适用于仅输入块。仅输入块的数量随设备大小而变化,但不超过总IOB计数的25%。

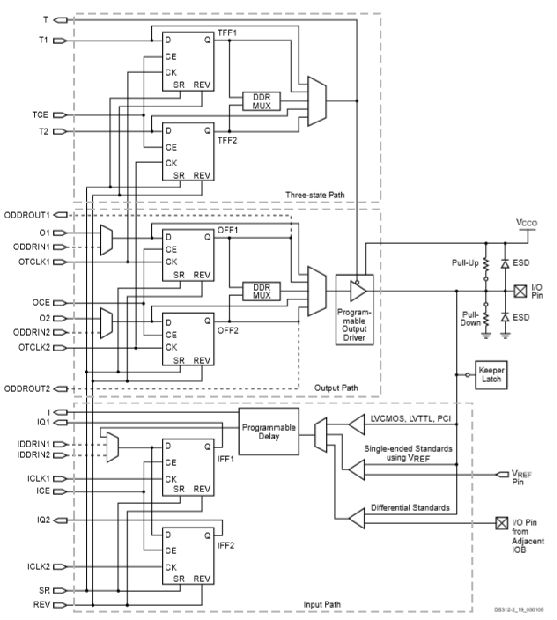

IOB中有三个主要的信号路径:输出路径、输入路径和三态路径。每个路径都有自己的一对存储元素,它们可以充当寄存器或锁存器。有关详细信息,请参见存储元素函数。三条主要信号路径如下:输入路径通过可选的可编程延迟元件直接将数据从焊盘(焊盘连接到封装引脚)传送到I线。之后

延迟元件,有通过一对存储元件到iq1和iq2线的备用路由。iob输出i、iq1和iq2指向fpga的内部逻辑。延迟元件可以设置为确保保持时间为零(参见输入延迟功能)。输出路径,从O1和O2线开始,通过多路复用器从FPGA内部逻辑传输数据,然后通过一个三态驱动器传输到IOB板。除此直接路径外,多路复用器还提供插入一对存储元件的选项。三态路径确定输出驱动器何时为高阻抗。T1和T2线通过多路复用器将数据从FPGA的内部逻辑传输到输出驱动器。除此直接路径外,多路复用器还提供插入一对存储元件的选项。所有进入IOB的信号路径,包括与存储元件相关的路径,都有一个逆变器选项。放置在这些路径上的任何逆变器都会自动吸收到IOB中。

输入延迟函数

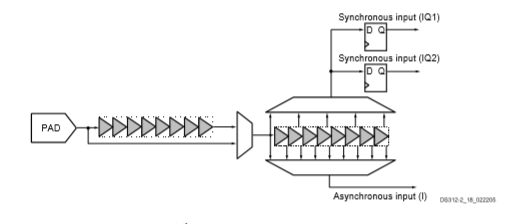

每个IOB都有一个可编程延迟块,可以将输入信号从0延迟到标称4000 ps。在图2中,信号首先被延迟0或2000 ps(标称),然后应用到8抽头延迟线。该延迟线的标称值为每个抽头250 ps。所有8个抽头都可以通过多路复用器直接用作异步输入到fpga结构中。通过这种方式,可以以250 ps的步进对从0到4000 ps的延迟进行编程。8个抽头中的4个也可通过多路复用器连接到同步存储元件的d输入端。在到存储元件的路径中插入的延迟可以在500 ps的步骤中从0到4000 ps变化。第一,粗延迟元素对异步和同步路径都是通用的,必须对两条路径都使用或不使用。

延迟值在配置时在硅中设置一次,它们在设备操作中不可修改。

输入延迟元件的主要用途是作为足够的延迟,以确保在将输入触发器与全局时钟一起使用时不需要保持时间。此函数的必要值由xilinx软件工具选择,并取决于设备大小。如果设计是在时钟路径中使用dcm,那么在用户的设计中延迟元素可以安全地设置为零,并且仍然没有保持时间要求。

异步值和同步值都可以由用户修改,这在时钟或数据输入需要额外延迟的情况下非常有用,例如,在各种类型RAM的接口中。

存储元件功能

每个iob中有三对存储元素,三条路径中的每一条都有一对。可以将这些存储元件中的每一个配置为边缘触发d型触发器(fd)或电平敏感锁存器(ld)。

输出路径或三态路径上的存储元件对可与专用多路复用器一起使用以产生双数据速率(DDR)传输。

这是通过将同步到时钟信号上升沿的数据转换成上升沿和下降沿同步的位来实现的。两个寄存器和多路复用器的组合称为双数据率d型触发器(oddr2)。

个状态路径上较低寄存器的ck输入。输入路径上的上下寄存器有独立的时钟线:ICLK1和ICLK2。

oce使能线控制输出路径上的上下寄存器的ce输入。同样,tce con

trols三态路径上寄存器对的ce输入,ice对输入路径上的寄存器对执行相同的操作。

进入iob的set/reset(sr)行控制所有六个寄存器,与reverse(rev)行一样。

双数据速率传输

双数据速率(DDR)传输描述了将信号同步到时钟信号上升和下降边缘的技术。SPARTAN-3E设备在所有三条IOB路径中使用寄存器对来执行DDR操作。

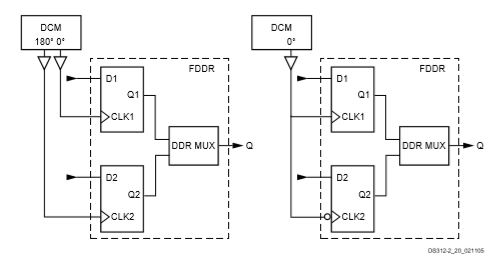

iob输出路径上的一对存储元件(off1和off2)用作寄存器,与一个特殊的多路复用器结合形成ddr d型触发器(oddr2)。该原语允许ddr传输,其中输出数据位与时钟的上升和下降边缘同步。ddr操作需要两个时钟信号(通常占空比为50%),一个是另一个的倒转形式。这些信号交替触发两个寄存器,数字时钟管理器(DCM)通过镜像一个输入信号,然后将其移动180度来生成两个时钟信号。这种方法确保了两个信号之间的最小偏差。或者,iob内的反相器可用于反转时钟信号,因此仅使用一个时钟线以及该时钟线的上升和下降沿作为ddr触发器的两个时钟。

三态路径(tff1和tff2)上的存储元素对也可以与本地多路复用器组合以形成ddr原语。这允许将输出同步到时钟的上升和下降边缘。此ddr操作的实现方式与输出路径相同。

输入路径(iff1和iff2)上的存储元件对允许i/o接收ddr信号。一个输入的DDR时钟信号触发一个寄存器,而反向时钟信号触发另一个寄存器。寄存器轮流捕捉输入ddr数据信号的位。允许此功能的原语称为iddr2。

除了高带宽数据传输外,ddr输出还可用于在输出端再现或镜像时钟信号。此方法用于同时传输时钟和数据信号(同步源)。类似的方法用于在多个输出端再现时钟信号。

寄存器级联特性

在spartan-3e家族中,差分对中的一个iob可以将其输入或输出存储元素与差分对中的另一个iob中的存储元素级联。这是为了使高速ddr操作更易于实现。可用的新DDR连接(虚线),仅可用于IOB之间的路由,而不可用于FPGA结构。请注意,此功能仅在使用差分I/O时可用。

IDDR2号

作为ddr输入对,主iob在iclk1的上升沿(=d1)和iclk2的上升沿(=d2)上注册输入数据,该上升沿通常与iclk1的下降沿相同。然后将这些数据传输到fpga结构中。在某个时刻,两个信号必须被带入同一个时钟域,通常是iclk1。这在高频时可能很困难,因为假设占空比为50%,可用时间仅为时钟周期的一半。

在spartan-3e设备中,信号d2可以级联到相邻从iob的存储单元中。在那里,它被重新注册到iclk1,然后才被馈送到fpga结构中,此时它已经与d1在同一个时域中。这里,fpga结构仅使用时钟iclk1来处理接收到的数据。

奥德2

作为ddr输出对,主iob在oclk1的上升沿(=d1)和oclk2的上升沿(=d2)上注册来自fpga结构的数据,该上升沿通常与oclk1的下降沿相同。这两位数据被ddr mux多路复用并转发到输出管脚。在fpga结构中的某个时刻,信号d2必须从oclk1域引入时钟域oclk2。这在高频时可能很困难,因为可用的时间只有半个时钟周期。

在spartan-3e设备中,信号d2可以通过相邻从iob的存储单元级联。这里,它由oclk1注册,然后转发到主iob,在那里它被重新注册到oclk2,由ddr多路复用器像往常一样选择,然后转发到输出pin。这样,只需使用fpga结构中的时钟oclk1就可以处理用于传输的数据

选择信号标准

Spartan-3E I/O的输入和输出支持广泛的I/O信号标准(表3和表4)。大多数I/O也可用于形成差分对,以支持任何差分信令标准(表4)。

SPARTAN-3E FPGA通过允许I/O标准在不同的银行中混合来提供额外的输入灵活性。必须特别注意确保输入电压不超过VCCO(。对于特定的VCCO电压,表3和表4列出了可以组合的所有IOS标准,以及IOS标准是否仅作为输入支持,或是否可用于输入和输出。

hstl和sstl输入使用参考电压(vref)来偏置输入开关阈值。一旦配置数据文件被加载到要求给定银行的i/o使用hstl/sstl的fpga中,同一银行的一些特定保留的i/o管脚就会自动转换为vref输入。对于不包含hstl或sstl的组,vref管脚仍然可用于用户i/o或输入管脚。

差分标准采用一对信号,一对信号的极性相反。这些标准的噪声消除特性(例如,共模抑制)允许异常高的数据传输速率。本小节介绍SPARTAN-3E设备的差分信令能力。

每个设备包组合指定特定的I/O对,特别优化以支持差异标准。差分对可以通过“显示差分对”选项显示在端号和区域约束编辑器(PACE)中。一个唯一的L号(作为管脚名称的一部分)标识与每个管组相关联的线对。对于每一对,字母p和n分别表示实线和倒转线。例如,管脚名称io_l43p_3和io_l43n_3指示由第3列上的线对l43组成的真线和反转线。VCCO为输出端提供电流,并为片上差分终端提供额外电源。使用片上差分终端时,VCCO必须为2.5V。差动操作不需要VREF管路。

片上差分终端SPARTAN-3E设备在输入差分接收器端子上提供片上100Ω差分终端

(具体范围见模块3)。spartan-3e器件中的片上输入差分终端消除了差分接收器电路中常见的外部100Ω终端电阻。在应用允许的情况下,对LVD、小型LVD和BLVDS使用差分终端。

片上差动终端在VCCO=2.5V的组中可用,专用输入引脚不支持。将diff_term属性设置为true以启用差分I/O管脚对上的差分终端。

diff_term属性在ucf文件中使用以下语法:inst<i/o_buffer_instantiation_name>diff_term=“<true/false>”;上拉和下拉电阻器每个IOB内的上拉和下拉电阻器可以选择强制浮动I/O引脚进入确定的状态。

下拉电阻器通常用于未使用的I/O、输入和三态输出,但可用于任何I/O。下拉电阻器通过电阻器将I/O连接到VCCO。电阻值取决于VCCO电压(有关规格,请参阅模块3)。下拉电阻器类似地将I/O与电阻器接地。pullup和pulldown属性以及库原语打开这些可选电阻。

默认情况下,下拉电阻器终止所有未使用的I/O。未使用的I/O也可以设置为pullup或float。要更改未使用的I/O焊盘设置,请将Bitstream Generator(BitGen)选项unusedPin设置为pullup、pulldown或float。unusedpin选项可通过ISE中生成编程文件的属性访问。

在配置过程中,HSWAP上的低逻辑电平激活所有未在所选配置模式中直接使用的I/O的上拉电阻器。

保持电路

每个I/O都有一个可选的保持电路,当总线没有被主动驱动时,保持总线不浮动。在所有驱动器关闭后,保持器电路保持线路上的最后一个逻辑电平。应用keeper属性或使用keeper库原语来使用keeper电路。上拉和下拉电阻器覆盖保持器设置。

回转率控制和驱动强度

每个iob都有一个转换速率控制,用于设置lvcmos和lvttl输出的输出开关边速率。“旋转”属性控制旋转速率,可以设置为“慢”(默认)或“快”。

每个LVCMOS和LVTTL输出额外支持多达6种不同的驱动电流强度要调整每个输出的驱动强度,请将“驱动”属性设置为所需的驱动强度:2、4、6、8、12和16。

高输出电流驱动强度和快速输出转换率通常会导致最快的I/O性能。然而,这些相同的设置通常也会对印刷电路板(pcb)产生传输线效应,除了最短的线路板外。每个IOB都有独立的回转率和驱动强度控制。使用满足最终应用性能要求的最低回转率和最低输出驱动电流。

同样,由于引线电感,当使用快速、高驱动输出时,给定的封装支持有限数量的同时开关输出(sso)。仅在应用程序需要时使用快速、高驱动输出。

组织成银行的借据

Spartan-3E体系结构将IOB组织为四个I/O组,每家银行都有独立的VCCO和VREF供应。独立的电源允许每家银行独立设置VCCO。类似地,可以为每个银行设置vref供给。VCCO和VREF要求见表3和表4。当使用Spartan-3E设备时,大多数差分I/O标准是兼容的,可以在任何给定的组内组合。每个银行可以支持以下任何两个差异标准:lvds_25输出、mini_lvds_25输出和rsds_25输出。例如,在使用片上差分终端时,lvds_25输出、rsds_25输出和任何其他差分输入是有效的组合。不允许的组合是具有lvds-25输出、rsds-25输出和mini-lvds-25输出的单个列组。

I/O银行规则在将I/O分配给银行时,必须遵循这些VCCO规则:1。即使银行未使用,也必须连接fpga上的所有vcco管脚。2.一个组内所有相关的VCCO线路必须设置为相同的电压水平。三。指定给任何给定银行的I/O的所有标准所使用的VCCO级别必须一致。xilinx开发软件会对此进行检查。表3和表4描述了不同标准如何使用VCCO供应。四。如果银行没有任何VCCO要求,请将VCCO连接到可用电压,如2.5V或3.3V。某些配置模式可能会对VCCO提出附加要求。

如果分配给银行输入的任何标准使用VREF,则必须遵守以下附加规则:1.所有VREF管脚必须连接在一个组内。2.与气缸组相关的所有VREF线路必须设置为相同的电压水平。三。分配给银行输入的所有标准所使用的VREF水平必须一致。xilinx开发软件会对此进行检查。表3描述了不同标准如何使用VREF供应。如果不需要vref来偏置输入开关阈值,则组内的所有相关vref管脚都可以用作用户i/o或输入管脚。

封装外形兼容性

有时,应用程序会超出特定SPARTAN-3E FPGA的逻辑容量。幸运的是,Spartan-3e系列的设计使多种零件类型可用于与管脚兼容的封装外形,如模块4所述。在某些情况下,在同一个内存中可用的设备之间存在细微的差异。这些差异为每个包概述,例如在同一个包中未连接到一个设备但连接到另一个设备的管脚,或在一个包上是专用输入但在另一个包上是完整I/O的管脚。在设计印刷电路板(pcb)时,要为将来可能的升级和封装迁移做好计划。

斯巴达3e系列与之前的任何xilinx fpga系列都不兼容。

专用输入

专用输入是仅用作输入的iob。如果名称以IP开头(例如IP或IP_Lxxx_X),则管脚名称指定一个专用输入。专用输入保留输入功能的IOB的全部功能,但差异输入(IP_Lxxx_X)除外。对于差分专用输入,片上差分终端不可用。要更换芯片上的差分终端,请选择支持输出(IO_lxxx_x)的差分对,或在板上使用外部100Ω终端电阻器。

ESD保护

钳位二极管可保护所有装置衬垫免受静电放电(ESD)和过大电压瞬变的损坏。每个i/o有两个钳位二极管:一个二极管从pad向vcco扩展p-to-n,另一个二极管从pad向gnd扩展n-to-p。在工作过程中,这些二极管通常在关闭状态下有偏压。无论选择何种信号标准,这些钳位二极管始终连接到焊盘。二极管的存在限制了斯巴达3e i/o承受高信号电压的能力。模块3的表1中的VIN绝对最大额定值指定了I/OS可以容忍的电压范围。

IOB的电源电压

IOB由三个电源供电:1。vcco为每个fpga的i/o库提供一个电源,为输出驱动器供电。VCCO引脚上的电压决定了输出信号的电压摆动。2.vccint是fpga内部逻辑的主电源。三。VCUAX是一个辅助电源,主要是为了优化各种FPGA功能,如I/O转换的性能。

上电、配置和用户模式期间的I/O所有I/O都有ESD钳位二极管连接到各自的VCCO电源和GND,VCCINT(1.2V)、VCCAUX(2.5V)和VCCO电源可以按任何顺序使用。在fpga开始其配置过程之前,vccint、vcco bank 2和vccaux必须已达到各自推荐的最低操作要求Levels(see table 2 of module 3)此时,所有我/O驱动器都处于高阻抗状态。VCCO Bank 2,VCCINT,and VCCAU Serve as Inputs to the Internal Power-on Reset C路

一种低水平的应用于HSWAP输入可穿过配置的PUL电阻器上的USER I/OS。在HSWAP上的一个高电平可拆卸拉链电阻器,允许我/骨浮动。HSWAP含有一个软毛衣,如果左漂浮的话,高缺陷。当电源被应用时,FPGA开始初始化其配置存储器。在同一时间,FPGA Internally asserts the global set-reset(“GSR”),which asynchronously resets all IOB storage elements to a default low state.

在初始化完成和配置初始化的基础上,开始进行高,采样M0,M1,和M2输入以确定配置模式。在这一点上,配置数据被载入FPGA。所述I/O驱动器在一个高阻抗状态下(与或无脉冲电阻器,以HSWAP输入确定)通过所述配置。

在配置结束时,GSR Net被释放,将IOB寄存器放置在一个低状态中,除非

负载设计反向其各自的输入极性

全球三个状态(GTS)Net(GTS)Net(GTS)Net)是在启动时释放的,标志着配置结束和用户模式中设计操作的开始。在GTS Net被释放后,所有的用户/OS都在活动,而所有未使用的I//OS都是脆弱的下载(“Pulldown”)。设计师可以控制在GTS之后未使用的I/

一个时钟循环延迟(“Default”),全球文字可启用(GWE)Net被释放,RAM和注册机构可改变状态。一次在使用模式中,HSWAP反复产生的任何Pull-up电阻器都可作为一个通用的设置和HSWAP,I//O.提供关于Pullup和Pulldown的更多信息,见Pull-up和Pull-down电阻器。

可配置逻辑块(CLB)和切片资源

CLB概述

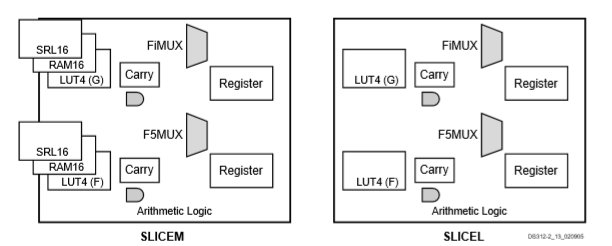

可配置逻辑块(clb)是实现同步电路和组合电路的主要逻辑资源。每个CLB包含四个片,每个片包含两个用于实现逻辑的查找表(LUT)和两个可用作触发器或闩锁的专用存储元素。lut可以用作16x1存储器(ram16)或16位移位寄存器(srl16)。

附加的多路复用器和进位逻辑简化了广泛的逻辑和算术功能。设计中的大多数通用逻辑都自动映射到CLB中的切片资源。每个CLB都是相同的,斯巴达-3E家族的CLB结构与斯巴达-3家族的相同。

CLB阵列

CLB按行和列的常规数组排列

每个密度随CLB的行数和列数而变化

每个CLB包含四个相互连接的切片这些切片成对分组。每一对都被组织成一个具有独立进位链的列。左对同时支持逻辑和内存函数,其切片称为切片。右边的对只支持逻辑,它的片称为片。因此

lut同时支持逻辑和内存(包括ram16和srl16移位寄存器),而half只支持逻辑,这两种类型在数组列中交替出现。slicel减少了clb的大小,降低了设备的成本,并且还可以提供比slicem更高的性能优势。

切片位置指定

xilinx开发软件根据切片的x和y坐标指定切片的位置,从左下角开始,如图11所示。字母“x”后跟一个数字表示从模具左侧到右侧递增的切片列。字母“Y”后跟一个数字,表示一对中每个切片的位置,并指示CLB行,从模具底部开始递增。位于模具左下角的CLB。slicem总是有一个偶数'x'号,slicel总是有一个奇数'x'号。

切片概述

一个切片包括两个lut函数生成器和两个存储元素,以及额外的逻辑

slicem和slicel都有以下共同元素来提供逻辑、算术和rom功能:

•两个4输入lut函数生成器,f和g•两个存储元件•两个宽函数多路复用器,f5mux和fimux•进位和算术逻辑

切片对支持两个附加功能:

•两个16x1分布式RAM块,RAM16•两个16位移位寄存器,SRL16

以下各节将更详细地描述这些元素中的每一个。

逻辑单元

lut和存储单元的组合称为“逻辑单元”。片中的附加功能,如宽多路复用器、进位逻辑和算术门,增加了片的容量,实现了原本需要附加lut的逻辑。基准测试表明,整个片相当于2.25个简单逻辑单元。

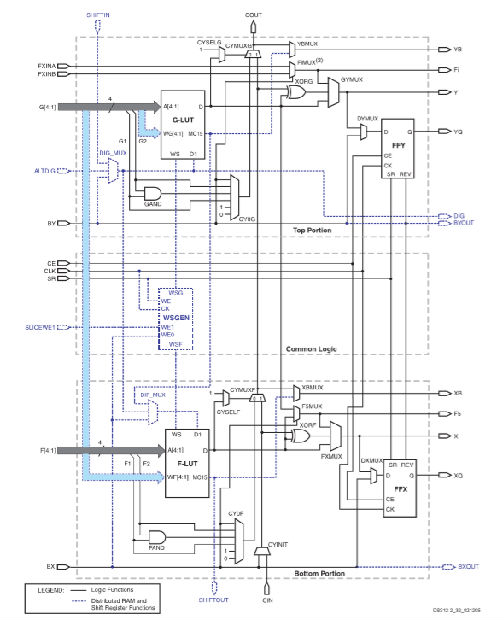

切片详细信息

它表示要在所有切片中找到的元素和连接的超集。虚线和灰色线(以颜色查看时为蓝色)表示仅在切片中而不是切片中找到的资源。

每一个切片都有两个部分,它们被区分为顶部和底部,以保持它们与CLB中的上下切片不同。时钟(CLK)的控制输入

ENABLE(CE)、SLICE WRITE ENABLE(SLICEWE1)和RESET/SET(RS)在两个部分之间共享。

位于切片的顶部和底部的lut分别称为“g”和“f”,或“g-lut”和“f-lut”。切片顶部和底部的存储元素分别称为ffy和ffx。

每个片有两个复用器,f5mux在片的底部,fimux在顶部。根据片的不同,fimux根据其在多路复用器链中的位置采用f6mux、f7mux或f8mux的名称。下切片和切片都有一个F6Mux。上面的切片有一个f7mux,上面的切片有一个f8mux。

进位链作为CIN进入切片的底部,并在顶部退出为CUT。五个多路复用器控制链:底部为cyinit、cy0f和cymuxf,顶部为cy0g和cymuxg。专用算术逻辑包括异或门xorf和xorg(分别为片的底部和顶部)以及和门fand和gand(分别为底部和顶部)。

主要逻辑路径

每个切片操作的中心是位于切片顶部和底部的两个几乎相同的数据路径。下面的描述使用与底部路径关联的名称。(顶部路径名出现在括号中。)基本路径源自CLB外部的互连交换机矩阵。

四条线,f1到f4(或g1到g4在上面的路径),进入切片并直接连接到lut。一旦进入切片,较低的4位路径通过执行逻辑操作的lut“f”(或“g”)。lut数据输出“d”提供五种可能的路径:

一。通过线“X”(或“Y”)退出该片并返回到互连。

2.在切片内部,“x”(或“y”)用作dxmux(或dymux)的输入,dxmux为ffy(或ffx)存储元素的数据输入“d”提供数据。存储单元的“Q”输出驱动退出该条的线XQ(或YQ)。

三。控制进位链上的cymuxf(或cymuxg)多路复用器。

四。对于进位链,用作执行算术运算的xorf(或xorg)异或门的输入,在“x”(或“y”)上产生结果。

5个。驱动多路复用器f5mux实现4位以上的逻辑功能。f-lut和g-lut的“d”输出都用作该多路复用器的数据输入。

除了上面描述的主逻辑路径外,还有两条旁路路径作为bx和by进入片。一旦进入fpga,bx在片的下半部分(或(位于上半部分中)可以接受几个可能的分支中的任何一个:

一。绕过LUT和存储元素,然后退出BXOUT(或BYOUT),并返回到互连。

2.绕过LUT,然后在以XQ(或YQ)退出之前,通过D输入通过存储元件。

三。控制宽功能多路复用器F5MUX(或FIMUX)。

四。通过多路复用器,作为进位链的输入。

5个。驱动lut的di输入。

6.by可以控制ffy和ffx存储单元的rev输入。请参见存储元素函数。

7号。最后,DigiMUX多路复用器可以切换到挖掘线,退出该切片。

控制输入CLK、CE、SR、BX和BY具有可编程极性。lut输入不需要可编程极性,因为它们的功能可以在lut内部反转。

下面的部分提供了有关切片的各个函数的更多详细信息。

查找表

查找表或lut是基于ram的函数生成器,是实现逻辑函数的主要资源。此外,如后所述,每个切片对中的lut可以配置为分布式ram或16位移位寄存器。

片中的两个lut(f和g)都有四个逻辑输入(a1-a4)和一个输出(d)。任何四变量布尔逻辑运算都可以在一个lut中实现。具有更多输入的函数可以由cascad实现

CLK SLICEL/M公共输入FFX/Y时钟或RAM时钟(SLICEM)

向G-LUT RAM输入移位切片顶部输入数据

移位器切片器底部输出移位数据从f-lut ram输出

CIN切片L/M底部输入进位链输入

cout切片l/m顶部输出进位链输出

X切片L/M底部输出组合输出

Y切片L/M顶部输出组合输出

XB切片L/M底部输出进位或F-LUT SRL16组合输出(切片)

YB切片L/M进位或G-LUT SRL16(切片M)的顶部输出组合输出

xq切片l/m底部输出ffx输出

YQ切片L/M顶部输出FFY输出

表7:切片输入和输出(续)

名称位置方向描述

功能描述

右

使用lut或使用稍后描述的宽功能多路复用器。

lut的输出可以连接到宽复用器逻辑、进位和算术逻辑,或者直接连接到clb输出或clb存储单元。

宽多路复用器

宽功能多路复用器有效地结合了lut以允许更复杂的逻辑操作。每个片都有两个这样的多路复用器,f5mux在片的底部,fimux在顶部。f5mux将两个lut多路复用在一个片中。fimux多路复用两个clb输入,这两个输入直接连接到f5mux,fimux结果来自同一片或其他片。

根据切片的不同,fimux的名称为f6mux、f7mux或f8mux。该名称表示在不限制功能的情况下可能的输入数量。例如,f7mux可以生成七个输入的任何函数。

每个mux可以创建比其名称指示的更多输入的逻辑函数。

ATE五个输入的任何功能,四个输入复制到两个LUT,第五个输入控制MUX。因为每个lut可以实现独立的2:1 mux,f5mux可以将它们组合起来创建一个4:1 mux,这是一个6输入函数。如果两个lut具有完全独立的输入集,则可以实现所有九个输入的某些功能。表8显示了每个多路复用器的连接以及不同类型功能可能的输入数量。

专用乘法器SPARTAN-3E设备为每个设备提供4到36个专用乘法器块。乘法器与块ram一起位于一列或两列中,具体取决于设备密度。有关这些块的位置及其连接性的详细信息,请参见模具上RAM块的排列。

乘法器块主要执行2的补码数字乘法,但也可以执行一些不太明显的应用,如简单的数据存储和桶移位。逻辑片还实现了高效的小乘法器,从而补充了专用乘法器。SPARTAN-3E专用倍增器块具有SPARTAN-3 FPGAs提供的额外功能。

每个乘法器执行主操作p=a×b,其中“a”和“b”是两个补码形式的18位单词,“p”是完全精确的36位乘积,也是两个补码形式的。18位输入表示从-13107210到+13107110的值,结果产品从-1717973811210到+1717986918410。

通过符号扩展输入(即复制最有效位),实现输入小于18位的乘法器。更广泛的乘法运算是通过将专用乘法器和基于片的逻辑组合成任何可行的组合来执行的,或者通过将单个乘法器分时来执行的。通过将输入限制在正范围来执行无符号乘法。将最高有效位低位绑定,并在剩余的17个次有效位中表示无符号值。

如图33所示,每个乘法器块在每个乘法器输入和输出上都有可选寄存器。寄存器名为areg、breg和preg,可用于任何组合。时钟输入对一个块中的所有寄存器都是公共的,但每个寄存器都有独立的时钟启用和同步复位控制,使它们成为存储数据样本和系数的理想选择。当用于流水线时,寄存器提高乘法器的时钟速率,有利于更高性能的应用。

使用图34所示的mult18x18sio原语在设计中实例化乘法器。尽管高级逻辑综合软件通常会自动推断出一个乘法器,但是添加流水线寄存器通常需要mult18x18sio原语。连接适当的信号

到mult18x18sio乘法器端口,并将单个areg、breg和preg属性设置为“1”以插入相关寄存器,或设置为0以删除它并使信号路径组合。

数字时钟管理器(DCMS)

与斯巴达-3建筑的区别

•Spartan-3E FPGas有两个、四个或八个DCM,具体取决于设备尺寸。SSPANT-3E DCM的最大相移范围±180°。斯巴达-3的DCM范围是±360°。•SPARTAN-3E动态链接库支持更低的输入频率,低至5兆赫。斯巴达-3 DLL支持低至24兆赫。

概述

SPARTAN-3E数字时钟管理器(DCMS)为时钟频率、相移和偏斜提供灵活、完整的控制。为了实现这一点,dcm采用了延迟锁定环(dll),这是一个全数字控制系统,它使用反馈来保持时钟信号的高精度特性,尽管工作温度和电压正常变化。本节提供DCM的基本描述。有关更多信息,请参阅xapp462:“在spartan-3系列fpgas中使用数字时钟管理器(dcms)”。

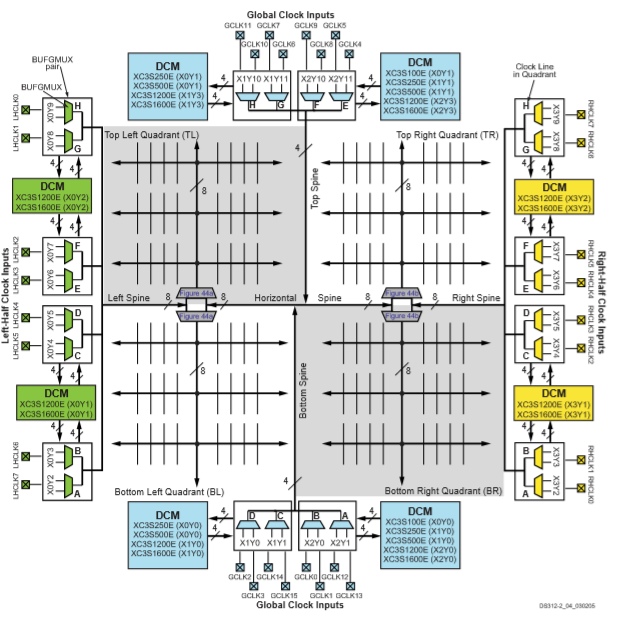

xc3s100e的fpga有两个dcm,一个在设备的顶部,一个在设备的底部。xc3s250e和xc3s500e fpgas各包括四个dcm,顶部两个,底部两个。xc3s1200e和xc3s160e fpgas包含八个dcm,每个边缘有两个(另请参见图42)。spartan-3e fpgas中的dcm被逻辑阵列中的clb包围,不再像spartan-3架构中那样位于块ram列的顶部和底部。数字时钟管理器作为“dcm”原语被实例化为一个设计。

DCM支持三个主要功能:

•时钟偏差消除:时钟偏差描述了在正常情况下,时钟信号偏离零相位对准的程度。当路径延迟的微小差异导致时钟信号在不同时间到达模具上的不同点时,就会发生这种情况。这种时钟偏差会增加设置和保持时间要求以及时钟到输出时间,这在定时非常关键的情况下,在高频运行的应用中可能是不需要的。DCM通过将其产生的输出时钟信号与反馈的另一版本时钟信号对齐来消除时钟偏差。结果,两个时钟信号建立零相位关系。这有效地消除了可能位于从dcm的时钟输出到其反馈输入的信号路径中的输出时钟分布延迟。•频率合成:DCM具有输入信号,可产生多种不同的输出时钟频率。这可以通过将输入时钟信号的频率乘以和/或除以几个不同因素中的任何一个来实现。•移相:DCM提供相对于其输入时钟信号移动其所有输出时钟信号相位的能力。dcm有四个功能部件:延迟锁定环(dll)、数字频率合成器(dfs)、移相器(ps)和状态逻辑dll时钟输入连接

外部时钟源使用全局时钟输入缓冲器(ibufg)进入fpga,该缓冲器直接访问全局时钟网络或通过输入缓冲器(ibuf)。fpga中的时钟信号使用全局时钟复用器缓冲器(bufgmux)驱动全局时钟网。全局时钟网络直接连接到clkin输入。内部和外部连接分别如图39a和图39c所示。差分时钟(例如lvds)可以作为clkin的输入。

dll时钟输出和反馈连接

九个DCM时钟输出中多达四个可以同时驱动同一模具边缘上的四个BUFGMUX缓冲区。所有的DCM时钟输出可以同时驱动一般的路由资源,包括通向OBUF缓冲区的互连。

反馈回路对动态链接库操作至关重要,它是通过使用clk0或clk2x信号驱动clkfb输入来建立的,以便在回路中包括任何不希望的时钟分布延迟。可以使用这两个信号中的任何一个来同步七个dll输出:clk0、clk90、clk180、clk270、clkdv、clk2x或clk2x180。分配给clk_feedback属性的值必须与物理反馈连接一致:clk0的值为1x,clk2x的值为2x。如果在不需要dll的应用程序中使用dcm(即只使用dfs),则不需要反馈循环,因此clk_feedback设置为none。

决定如何连接dll时钟输出和反馈连接的基本情况有两种:片内同步和片外同步

bufgmux对连接到八个全局时钟输入中的四个,这允许对全局时钟输入进行差分输入,而不浪费bufgmux元素。

下边缘bufgmux元素的连接类似于上边缘连接。

在左边缘和右边缘,只有两个时钟输入为每对bufgmux元素供电。

象限时钟路由

fpga内部的时钟路由是基于象限的,每个时钟象限支持8个总时钟信号,在表36和图44中标记为“A”到“H”。单个时钟线的时钟源要么来自沿上下边缘的全局bufgmux元素,要么来自沿关联边缘的bufgmux元素,时钟线为象限内的同步资源元素(CLB、IOB、块RAM、乘法器和DCM)供电。

设备的四个象限是:•右上(TR)•右下(BR)•左下(BL)•左上(TL)注意,象限时钟符号(tr,br,bl,tl)与用于类似iob放置约束的符号是分开的。

配置

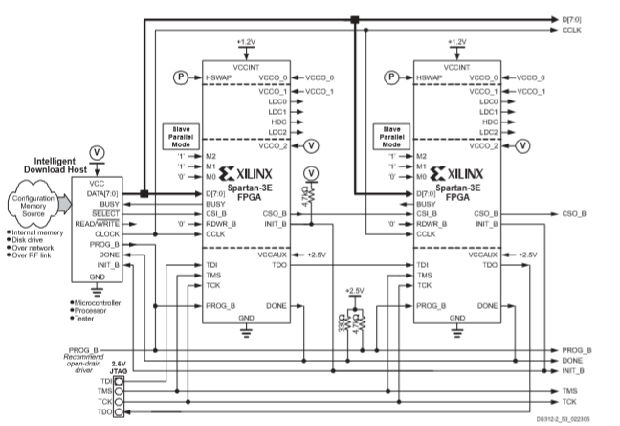

与Spartan-3燃气轮机的区别

一般来说,SPARTAN-3E FPGA配置模式是SPARTAN-3FPGAs中可用配置模式的超集。SPARTAN-3E FPGAs中增加了两种新模式,为工业标准的并行NOR闪存和SPI串行闪存提供了无胶配置接口。与Spartan-3FPGas不同,几乎所有的Spartan-3E配置管脚在配置后都可以作为用户I/O使用。

配置过程

spartan-3e fpga的功能是通过将特定于应用程序的配置数据加载到fpga的内部可重编程cmos配置锁存器(ccls)中来定义的,类似于微处理器的功能由其应用程序定义的方式。对于fpgas,此配置过程使用设备管脚的一个子集,其中一些管脚专用于配置;其他管脚仅用于

在配置完成后作为通用用户I/O借用并返回给应用程序。

Spartan-3E FPGAs提供多种配置选项,以最大限度地降低配置对整个系统设计的影响。在某些配置模式中,fpga生成时钟并从外部存储器源(串行或通过字节宽的数据路径)加载自身。或者,外部主机(例如微处理器)使用简单的同步串行接口或通过字节宽的外设样式接口下载fpga的配置数据。此外,多个fpga设计共享一个配置内存源,创建一个称为菊花链的结构。

三个fpga引脚m2、m1和m0选择所需的配置模式。模式引脚设置如表38所示。当fpga的init_b输出变高时,模式pin值在配置开始时被采样。在fpga完成配置之后,模式管脚可以作为用户i/o使用。

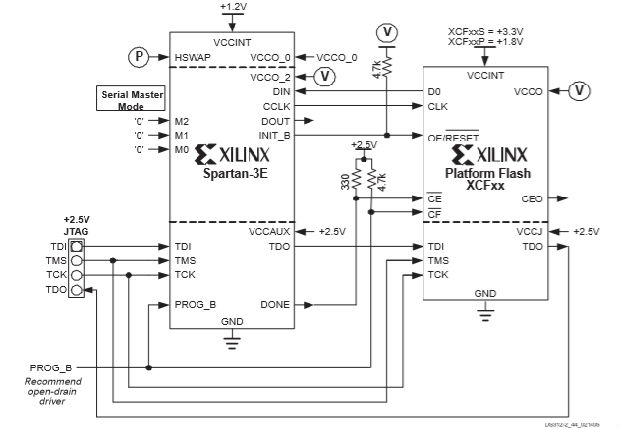

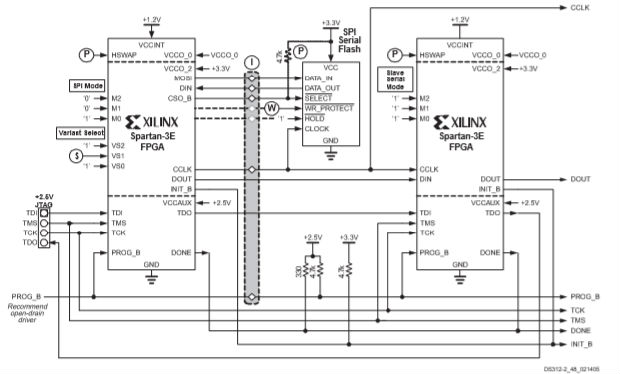

主串行模式

在主串行模式(M[2:0]=<0:0:0>)中,Spartan-3E的FPGA从附加的Xilinx平台闪存PROM进行自我配置,fpga将cclk输出时钟从其内部振荡器提供给

附加的flash prom平台。作为回应,平台flash prom向fpga的din输入端提供位串行数据,而fpga在每个上升的cclk边缘接收这些数据。

如果应用程序需要具有不同配置的多个FPGAs,则使用菊花链配置FPGAs,将主串行模式(M[2:0]=<0:0:0>)用于连接到平台闪存PROM的FPGA,将从串行模式(M[2:0]=<1:1:1>)用于菊花链中的所有其他FPGA。图中左侧的主fpga完成从平台flash加载其配置数据后,主设备使用其dout输出管脚在下降的cclk边缘向菊花链中的下一个设备提供数据。

JTAG接口

spartan-3e fpga和平台flash prom都有一个四线ieee 1149.1/1532jtag端口。两个设备共享tck时钟输入和tms模式选择输入。这些装置可以在jtag链上以任意顺序连接,其中一个装置的tdo输出向链中的以下装置的tdi输入供电。JTAG链中最后一个设备的TDO输出驱动JTAG连接器。

spartan-3e fpgas上的jtag接口由2.5vccaux电源供电。因此,prom的vccj电源输入也必须是2.5v。要创建3.3v jtag接口,请参阅应用说明xapp453:“斯巴达-3 fpgas的3.3v配置”了解更多信息。

系统内编程支持

fpga和平台flash prom都是通过jtag链在系统中编程的。下载支持是由xilinx impact编程软件和相关的xilinx并行电缆iv、multipro或平台电缆usb编程电缆提供。

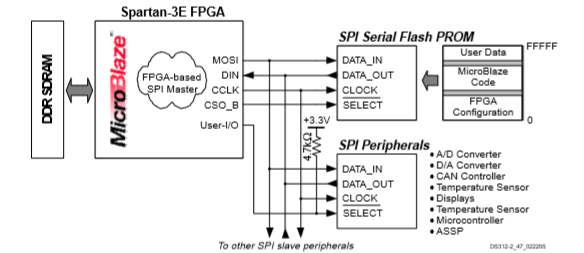

在平台flash中存储额外的用户数据

配置之后,fpga应用程序可以继续使用主串行接口管脚与平台flash prom通信。如果需要,使用更大的平台flash prom来保存额外的非易失性应用程序数据,例如microblaze处理器代码,或其他用户数据,例如序列号和以太网mac id。fpga首先从平台flash prom进行配置。然后利用配置后的fpga逻辑,将平台flash中的微块代码复制到外部ddr sdram中进行代码执行。

“从配置proms读取用户数据”和xapp482:“microblaze平台flash/prom引导加载程序和用户数据存储”,了解如何实现这种接口的具体细节。

串行闪存模式

在SPI串行闪存模式(M[2:0]=<0:0:0>)中,Spartan-3E现场可编程门阵列根据附加的工业标准SPI串行闪存PROM进行自我配置。fpga将cclk输出时钟从其内部振荡器提供给所附spi flash prom的时钟输入。

spi flash prom密度要求

可编程单个SPARTAN-3E现场可编程门阵列的最小可用SPI闪存PROM。商用SPI闪存Prom的密度范围从1兆比特到128兆比特。多个fpga菊花链应用程序需要一个足够大的spi flash prom来包含fpga文件大小的总和。应用程序还可以使用更大密度的spi flash prom来保存除了fpga配置数据之外的其他数据。例如,spi flash prom还可以存储集成在spartan-3e fpga中的microblaze™risc处理器核心的应用程序代码。请参阅配置后使用SPI闪存接口。

CCLK频率

在spi闪存模式下,fpga的内部振荡器产生配置时钟频率。fpga在其cclk输出管脚上提供这个时钟,驱动prom的时钟输入管脚。如果在配置位流中指定,则fpga以其最低频率开始配置,并在配置过程的其余部分增加其频率。使用配置比特流生成器选项指定最大频率。FPGA配置逻辑支持的最大频率取决于提姆。

用于SPI闪存设备。在不检查特定SPI闪存PROM的时序的情况下,使用配置速率=12,其大约为12 MHz。支持快速读取命令的spi flash prom支持更高的数据速率。一些这样的prom支持高达configrate=25或更高,但需要仔细的数据表分析。

配置后使用spi flash接口

在fpga成功完成配置之后,所有连接到spi flash prom的管脚都可用作用户i/o管脚。

如果配置后不使用SPI闪存PROM,请将CSO U B驱动器调高以禁用PROM。然后,mosi、din和cclk管脚可用于fpga应用程序。

由于所有接口管脚在配置后都是用户I/O,所以FPGA应用程序可以继续使用SPI闪存接口管脚与SPI闪存PROM通信,spiflashprom为fpga应用程序提供随机访问、字节寻址、读/写、非易失性存储。

spi flash prom的可用密度从1 mbit到128 mbit不等。然而,一个spartan-3e的fpga需要小于6mbits。如果需要,可以使用更大的spi flash prom来包含附加的非易失性应用程序数据,例如microblaze处理器代码,或者其他用户数据,例如序列号和以太mac id。fpga从spi flash prom进行配置。然后利用配置后的fpga逻辑,将spi闪存中的微块代码复制到外部ddr sdram中进行代码执行。类似地,fpga应用程序可以在spi flash prom中存储非易失性应用程序数据。

从位置0开始存储fpga配置数据。存储从下一个可用的SPI闪存PROM扇区或页面开始的任何其他数据。不要在同一个扇区或页面中混合配置数据和用户数据。

系统内编程支持

在生产应用中,spi flash prom通常在安装到印刷电路板上之前进行预编程。一些第三方prom程序员使用带有连接线的插座适配器提供系统内编程支持。要获得对spi闪存信号的访问,使用开漏驱动程序将fpga的prog_b input低驱动。此操作将所有的fpga i/o管脚(包括连接到spi闪存的管脚)置于高阻抗(hi-z)中。如果hswap输入很高,则i/o在其各自的i/o组上具有到vcco输入的上拉电阻器。然后,外部编程硬件可以直接访问spi闪存管脚

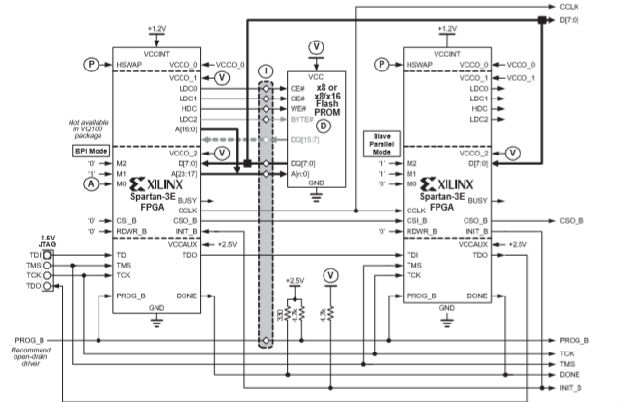

在字节宽外围接口(BPI)模式(M[2:0]=<0:1:0>或<0:1:1>)中,Spartan-3E FPGA从工业标准并行或闪存PROM进行自我配置,如图55所示。现场可编程门阵列产生

连接到24位地址行以访问连接的并行闪存。TQ144包中仅为Spartan-3E FPGAs生成20条地址线。BPI模式不适用于VQ100组件中的Spartan-3E FPGas。

该接口是为标准的并行或flash prom设计的,支持字节宽(x8)和字节宽/半字(x8/x16)prom。接口不支持半字(x16)proms。该接口与其他使用类似接口的存储器(如sram、nvram、eeprom、eprom或屏蔽rom)同样工作良好,但主要设计用于闪存。

还有另一种类型的闪存称为nand flash,通常用于数码相机等存储卡中。spartan-3e fpgas不直接从nand flash存储器配置。

fpga的内部振荡器控制接口时序,fpga在cclk输出管脚上提供时钟。然而,cclk信号并不用于单个fpga应用中。类似地,在配置过程中,fpga驱动prom的控制输入低三个管脚(ldc[2:0]),高一个管脚(hdc)。

系统内编程支持

在生产应用中,并行flash prom通常在安装到印刷电路板上之前进行预编程。系统内编程支持可从第三方边界扫描工具供应商和一些使用带有连接线的插座适配器的第三方PROM程序员处获得。为了获得对并行闪存信号的访问,使用开漏驱动程序驱动fpga的prog_b input low。此操作将所有的fpga i/o管脚(包括连接到并行闪存的管脚)置于高阻抗(hi-z)中。如果hswap输入很高,则i/o在其各自的i/o组上具有到vcco输入的上拉电阻器。然后,外部编程硬件可以直接访问并行闪存管脚。

在开发和测试阶段,fpga本身也可以用作并行flash prom程序员。最初,一个基于fpga的程序员通过jtag下载到fpga中。然后,fpga执行flash prom编程算法,并通过fpga的jtag接口从主机接收编程数据。

使用multiboot选项动态加载多个配置映像

在fpga从并行flash prom的一端使用bpi模式进行自我配置之后,fpga可以触发一个多引导事件并从并行flash prom的另一端重新配置自己。multiboot仅在使用bpi模式时可用,且仅适用于使用单个spartan-3e fpga的应用程序。

默认情况下,多引导模式被禁用。为了触发多引导事件,断言在MultiBoot Trigger(MBT)输入到STARTUPSP-SARTAN3E库原语上持续至少300纳秒的低脉冲。通电时,fpga从连接的并行flash prom加载自身。在本例中,m0模式管脚很低,因此fpga从地址0开始,并通过flash prom存储器位置递增。在fpga完成配置之后,加载到fpga中的应用程序使用fpga逻辑执行板级或系统测试。如果测试成功,fpga会触发一个多引导事件,导致fpga从flash prom存储器的另一端重新配置。第二个配置包含正常操作的fpga应用程序。

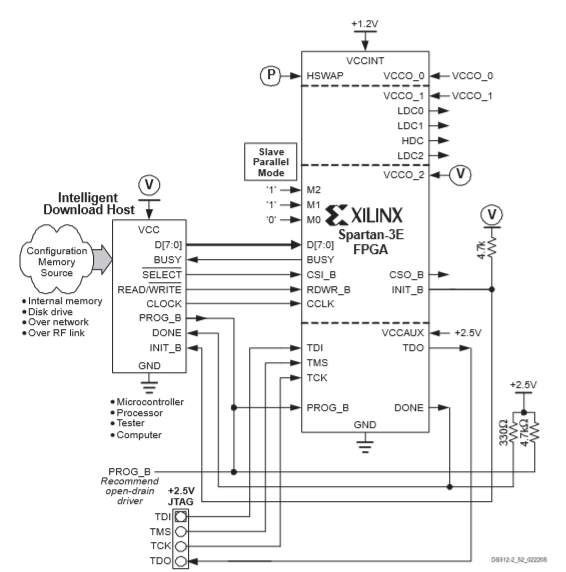

外部下载主机通过脉冲prog_b并监视init_b pin是否变高来启动配置过程,这表示fpga已准备好接收其第一个数据。主机断言有源低芯片选择信号(csi_b)和有源低写入信号(rdwr_b)。然后,主机继续提供数据和时钟信号,直到fpga的done pin变高,表示配置成功,或者直到fpga的init_b pin变低,表示配置错误。

fpga捕获上升cclk边缘的数据。如果cclk频率超过50mhz,那么主机还必须监视fpga的繁忙输出。如果fpga断言busy high,则主机必须将数据保存一个额外的时钟周期,直到busy返回low。如果cclk频率

为50兆赫或更低,忙碌的引脚可能会被忽略,但在配置过程中主动驱动器。

配置过程需要的时钟周期比配置文件大小指示的时钟周期多。在fpga的启动序列中需要额外的时钟,特别是当fpga被编程为等待选定的数字时钟管理器(dcm)锁定到它们各自的时钟输入时。

如果从并行接口仅用于配置fpga,而不用于回读数据,则rdwr_b信号也可以从接口中消除。但是,在配置期间,rdwr_b必须保持低。

从串行模式

在从串行模式(m[2:0]=<1:1:1>)中,外部主机(如微处理器或微控制器)同步串行接口将串行配置数据写入fpga。串行配置数据显示在fpga的din输入管脚上,在外部生成的cclk时钟输入的每个上升沿之前有足够的设置时间。

智能主机启动配置过程,通过脉冲prog_b并监视init_b pin变高,

表示fpga已准备好接收其第一个数据。然后,主机继续提供数据和时钟信号,直到done pin变高表示配置成功,或者直到init_b pin变低表示配置错误。配置过程需要的时钟周期比配置文件大小指示的时钟周期多。在fpga的启动序列中需要额外的时钟,特别是当fpga被编程为等待选定的数字时钟管理器(dcm)锁定到它们各自的时钟输入

模式选择管脚m[2:0]在fpga的init_b输出变高时采样,并且在此期间必须处于定义的逻辑电平。配置后,当fpga的done输出变高时,模式管脚可用作全功能用户i/o管脚。

类似地,fpga的hswap管脚必须是低的才能在所有用户i/o管脚上启用上拉电阻,或者是高的才能禁用上拉电阻。hswap控件必须在整个fpga配置过程中保持恒定的逻辑级别。配置后,当fpga的done输出变高时,hswap pin可用作全功能用户i/o pin,并由vcco_0电源供电。

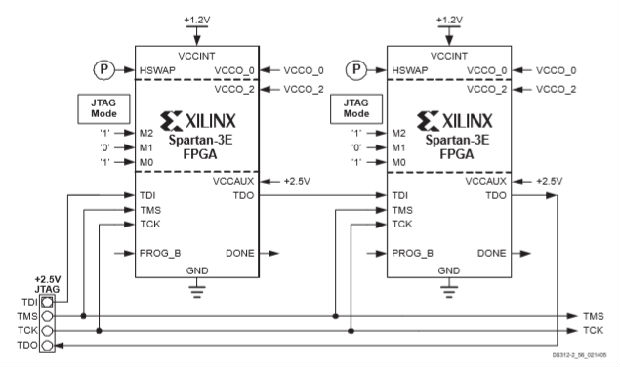

JTAG模式

spartan-3e fpga有一个专用的四线ieee 1149.1/1532jtag端口,无论模式管脚设置如何,只要fpga通电,它就始终可用。然而,当fpga模式管脚被设置为jtag模式(m[2:0]=<1:0:1>)时,fpga在通电事件之后或当prog_b被断言时等待通过jtag端口进行配置。选择jtag模式只需禁用

其他配置模式。配置接口不需要其他管脚。

jtag接口通过将一个设备的tdo输出连接到链中下一个设备的tdi输入很容易级联到任意数量的fpga。链中最后一个设备的tdo输出循环回到端口连接器。

电压兼容性

2.5V VCCAUX电源为JTAG接口供电。所有用户I/O都由各自的VCCO电源分别供电。

将SPARTAN-3E JTAG端口连接到3.3V接口时,JTAG输入引脚必须使用串联电阻将电流限制在10毫安或以下。类似地,tdo管脚是一个cmos输出,功率为+2.5v。tdo输出可以直接驱动3.3v输入,但噪声抗扰度降低。有关更多信息,请参阅应用说明xapp453:“斯巴达-3 fpgas的3.3v配置”。

菊花链的最大比特流大小

SASTAN-3E FPGA在串行菊花链中所支持的最大比特流长度为4294967264位(4比特),大致相当于具有720×C3S1600 E FPGA的菊花链。这只是串行菊花链的一个限制,其中配置数据通过fpga的dout引脚传递。JTAG链没有这样的限制。

配置序列

spartan-3e配置过程是在fpga通电后开始的三阶段过程(por事件)

或者在程序输入被断言之后。在VCCINT、VCCAUX和VCCO Bank 2电源达到各自的输入阈值水平后,会发生上电复位(POR)。在一个por或prog_b事件之后,

三阶段配置过程开始。

一。fpga清除(初始化)内部配置存储器。

2.配置数据被加载到内存中。

三。用户应用程序由启动过程激活。

spartan-3e配置逻辑的通用框图,显示了不同设备输入和比特流生成器(bitgen)选项的交互。

初始化

除非使用fpga的init-b管脚延迟,否则配置在通电或断言fpga prog-b管脚后自动开始。当清除内部配置存储器时,fpga保持开漏init_b信号低。外部保持init_b pin低将强制配置序列器等待,直到init_b再次变高。

直流电特性

在本节中,规范可指定为预先、初步或生产。这些术语的定义如下:

进展:初步估计是基于模拟、早期特征描述和/或从其他族的特征推断得出的。价值观随时可能改变。用作估算,不用于生产。

初步:基于特征。预计不会有进一步的变化。

生产:一旦硅在多个生产批次上进行了表征,这些规范就得到批准。参数值被认为是稳定的,不会有未来的变化。

所有参数限值均代表最坏情况下的电源电压和结温条件。以下适用,除非另有说明:本模块中发布的参数值适用于所有Spartan-3e设备。对于商用和工业级,交流和直流特性使用相同的数字指定。

如果一个特定的斯巴达-3e现场可编程门阵列在功能特性或电气特性上与本数据表不同,这些差异将在单独的勘误表文件中描述。

开关特性

所有斯巴达-3e型fpgas船有两种速度等级:–4和更高性能–5。如表11所示,本文件中的开关特性可指定为提前、初步或生产。每个类别的定义如下:

提前:这些规范仅基于模拟,通常在建立了fpga规范之后很快就可用。尽管采用这一名称的速度等级被认为是相对稳定和保守的,但仍可能出现一些报告不足的情况。

初步:这些规范基于早期完整的硅特性。具有该名称的器件和速度等级旨在更好地指示生产硅的预期性能。与预先报告的数据相比,预先报告的延迟的可能性大大降低。

生产:一旦特定设备系列成员的生产硅足够多,能够在多个生产批次中提供速度文件和设备之间的完全相关性,则批准这些规范。不存在延迟报告不足,客户收到任何后续变更的正式通知。通常,最慢的速度等级在更快的速度等级之前过渡到生产。

生产质量系统必须使用使用指定为生产状态的速度文件编译的fpga设计。使用不太成熟的速度文件名称的fpgas设计应仅在系统原型或预生产鉴定期间使用。在生产质量系统中,不应使用具有指定为预览、高级或初步的速度文件的fpga设计。

每当速度文件名称发生变化时,随着设备向生产状态成熟,xilinx建议在fpga设计上重新运行xilinx ise软件。这确保了fpga设计包含了最新的定时信息和软件更新。

所有规定限值均代表最坏情况下的电源电压和结温条件。除非另有说明,否则以下适用:参数值适用于所有Spartan-3e设备。所有代表电压的参数都是相对于GND测量的。

选择以下时序参数及其代表值,是因为它们作为一般设计要求很重要,或者它们表示基本的器件性能特性。spartan-3e速度文件(v1.10)是xilinx开发软件的一部分,是许多(但不是所有)值的原始源代码。这些文件的速度等级名称如表11所示。为了更完整、更精确和最坏的情况

数据,使用xilinx静态定时分析器(xilinx开发软件中的跟踪)报告的值,并返回注释到仿真网络列表。

数字时钟管理器(DCM)定时

出于规范目的,DCM由三个关键组件组成:延迟锁定环(DLL)、数字频率合成器(DFS)和移相器(PS)。

dll操作的各个方面在所有dcm应用程序中都发挥着作用。所有这些应用程序都不可避免地使用分别连接到clk0或clk2x反馈的clkin和clkfb输入。中的规范适用于仅使用dll组件的任何应用程序。当dfs和/或ps组件与dll一起使用时,dfs和ps表中列出的规范将取代dll表中相应的规范。

所有的DCM时钟输出信号表现出大约50%的占空比。

周期抖动和周期抖动是表征时钟抖动的两种不同方式。这两个规范都描述了平均值的统计变化。

周期抖动是采样的时钟周期集合中所有时钟周期的平均时钟周期的最坏情况偏差(出于规范目的,通常从100000到100多万个样本)。在周期抖动直方图中,平均值是时钟周期。

周期抖动是采样的时钟周期集合中相邻时钟周期之间时钟周期的最坏情况差。在周期抖动直方图中,平均值为零。

VQ100足迹

注意左上角的pin 1指示器和徽标方向。工程样本的足迹略有不同