15000点击型号即可查看芯片规格书

Spartan-II 2.5V现场可编程门阵列系列以极低的价格为用户提供了高性能、丰富的逻辑资源和丰富的功能集。这个六人家庭提供的系统门密度从15000到200000不等。系统性能支持高达200兆赫。

斯巴达II设备通过将先进的工艺技术与流线型的基于Virtex的架构相结合,提供了比其他FPGAs更多的门、I/O和每美元的功能。功能包括块RAM(至56K位)、分布式RAM(至75264位)、16个可选I/O标准和4个DLL。快速、可预测的互连意味着连续的设计迭代继续满足时序要求。

斯巴达II家族是一个优于掩模编程ASIC的替代品。fpga避免了传统asic的初始成本、冗长的开发周期和固有的风险。此外,fpga可编程性允许在现场进行设计升级,无需更换硬件(asic不可能)。

特征

第二代ASIC替换技术-密度高达5292个逻辑单元,系统门高达200000个-基于Virtex架构的流线型功能-无限可重编程性-非常低的成本

系统级功能-selectram+分层存储器:16位/lut分布式ram·可配置4k位块ram·与外部ram的快速接口-完全符合pci标准-低功耗分段路由体系结构-验证的完全可读性/可观察性-高速运算的专用进位逻辑-专用乘法器支持-用于宽输入功能的级联链-具有启用、设置和重置功能的大量寄存器/锁存器-用于高级时钟控制的四个专用dll-四个主低偏斜全局时钟分布网-与ieee 1149.1兼容的边界扫描逻辑•多功能i/o和封装-所有密度的低成本封装-系列通用软件包中的占用空间兼容性-16个高性能接口标准-热插拔紧凑型PCI友好型-零保留时间简化系统计时 完全受强大的Xilinx开发系统支持-基础ISE系列:完全集成的软件-联盟系列:用于第三方工具-完全自动映射,放置和布线概述

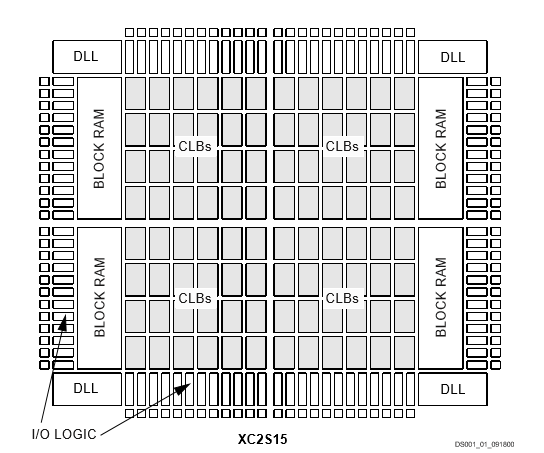

Spartan II系列FPGas具有规则、灵活、可编程的可配置逻辑块(CLB)体系结构,周围环绕着可编程输入/输出块(IOB)。有四个延迟锁定环(dll),在模具的每个角落都有一个。两列块RAM位于模具的对侧,在CLB和IOB列之间。这些功能元素通过多功能路由通道的强大层次结构互连。

Spartan II FPGas是通过将配置数据加载到内部静态存储单元来定制的。使用这种方法可以无限次地重新编程。这些单元中的存储值决定了逻辑功能和在fpga中实现的互连。配置数据可以从外部串行prom(主串行模式)读取,也可以以从串行、从并行或边界扫描模式写入fpga。

Spartan II FPGAs通常用于高容量应用,快速可编程解决方案的多功能性增加了好处。斯巴达II型FPGAs是缩短产品开发周期的理想选择,同时为大批量生产提供了一个经济高效的解决方案。

斯巴达ii型fpgas通过先进的架构和半导体技术实现了高性能、低成本的运行。斯巴达II设备提供高达200兆赫的系统时钟速率。斯巴达II FPGAs在保持领先性能的同时,提供最具成本效益的解决方案。除了大容量可编程逻辑解决方案的传统优势外,Spartan II FPGas还提供了片上同步单端口和双端口RAM(块和分布式形式)、动态链接库时钟驱动器、所有触发器上的可编程设置和复位、快速进位逻辑和许多其他功能。

建议将Xilinx XC17S00A PROM系列用于Spartan II FPGas的串行配置。系统内可编程(ISP)XC18V00 PROM系列推荐用于并行或串行配置。

数字