特征:低功率:48mW+3V;供电范围:+2.7V至+3.7V;带外部参考的可调满标度范围;没有丢失的代码;宽带跟踪/保持:350MHz;断电:15MW SSOP-28机组。

应用

电池供电设备;摄像机;数码相机;计算机扫描仪;通信。

描述

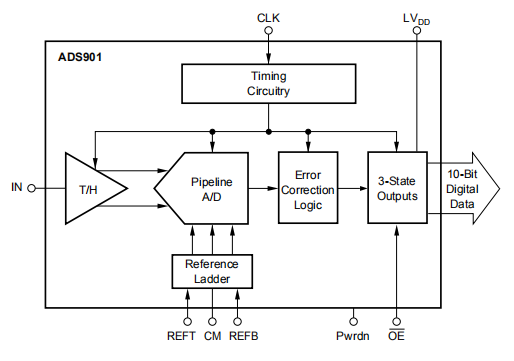

ADS901是一种高速流水线模数转换器,由+3V电源供电。这个完整的转换器包括一个宽带跟踪/保持和一个10位量化器。满标度输入范围由外部参照设定。

ADS901采用数字误差校正技术,为要求苛刻的成像应用提供出色的差分线性度。它的低失真和高信噪比为电信、视频和测试仪器应用提供了额外的裕度。ADS901在SSOP-28包中提供。

操作理论

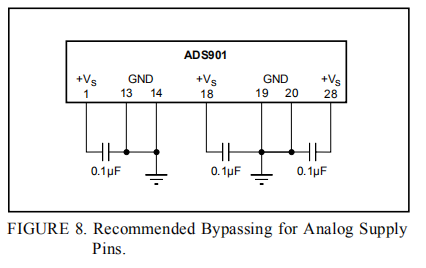

ADS901是一种采用流水线结构的高速采样模数转换器。全差分拓扑和数字纠错保证10位分辨率。差动跟踪/保持电路如图1所示。开关由内部时钟控制,内部时钟具有不重叠的两相信号φ1和φ2。采样时,输入信号被采样在输入电容器的底板上。在下一个时钟阶段,φ1,输入电容器的底板连接在一起,反馈电容器切换到运放输出。此时,电荷在ci和ch之间重新分配,完成一个跟踪/保持循环。差分输出是采样时模拟输入的保持直流表示。跟踪/保持电路还可以将单端输入信号转换为量化器的全差分信号。因此,输入的信噪比性能。该阶段还定义了小信号、全功率带宽、宽带噪声等参数。

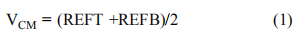

为了适应双极性信号摆动,ADS901使用从外部参考源导出的共模电压(VCM)工作。由于ADS901内部有对称的电阻阶梯,VCM位于顶部和底部参考电压之间。公式(1)可用于计算共模电压电平:

从开始转换信号到有效输出数据有5.0时钟周期数据延迟。标准输出编码是直偏移二进制,其中满标度输入信号对应于输出处的所有“1”。ADS901的数字输出可以通过用逻辑“HI”驱动三态(引脚16)设置为高阻抗状态。正常操作是通过引脚16“lo”实现的,或由于内部下拉电阻器而浮动。此函数用于可测试性目的,但不建议动态使用。

应用

信号摆动和共模的注意事项

ADS901设计为在+3V单电源电压下工作。标称输入信号摆幅为1vp-p,位于+1v和+2v之间。这意味着信号在+1.5v的共模电压(电源电压的一半)附近摆幅为±0.5v(VCM=vs/2)。在某些应用中,增加输入信号的摆动可能是有利的。这将提高可实现的信噪比性能。然而,应考虑将信号摆幅保持在驱动电路工作的线性范围内,以避免任何过度失真。在极端情况下,由于输入端的开关导通电阻随输入电压的变化,转换器的性能将开始下降。因此,在正常运行期间,信号摆幅应保持在离每条轨道约0.5V的位置。

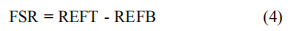

流水线量化器架构有9个阶段,每个阶段包含一个2位量化器和一个2位数模转换器,如图2所示。每个两位量化器级在子时钟的边缘上进行转换,子时钟的边缘与外部应用的时钟的频率相同。每个量化器的输出被输入到其自身的延迟线中,以便将其与从以下量化器级创建的数据时间对齐。这些对齐的数据被送入数字纠错电路,该电路可以根据在冗余位上找到的信息来调整输出数据。该技术为ads901提供了良好的差分线性度,并保证在10位级不丢失码。

驱动模拟输入

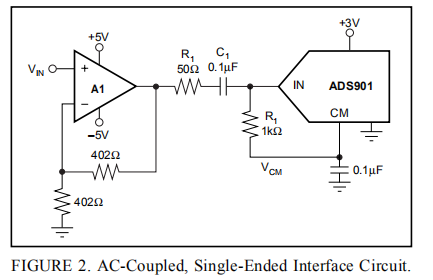

交流耦合驱动器

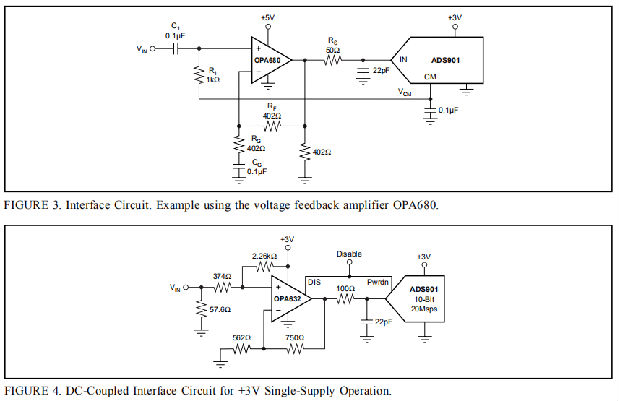

图2显示了一个交流耦合单端的示例使用高速运算放大器的接口电路双电源(OPA650、OPA658)。中点参考电压VCM使双极接地参考输入偏置信号。电容器C1和电阻器R1形成高通频率设置为-3db的滤波器:

c1和r1的值在大多数应用中并不重要,可以自由设置。所示值对应于1.6kHz的频率。

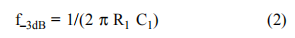

图3描述了一种可用于单电源应用的电路。中间参考电压将运放偏置至适当的共模电压,例如VCM=+1.5V。使用电容器CG,非逆变运放输入的直流增益设置为+1V/V。因此,传输函数修改为:

同样,输入耦合电容器c1和电阻器r1形成高通滤波器。同时,输入阻抗由r1定义。电阻器RS将运放的输出与电容负载隔离,以避免增益峰值甚至振荡。它还可以用来建立一个定义的带宽,以减少宽带噪声。建议值通常在10Ω和100Ω之间。

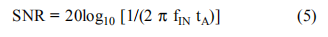

直流耦合接口电路

许多系统现在要求a/d转换器及其驱动器具有+3v的单电源能力。图4显示了仅在+3V电源电压下工作的直流耦合配置的示例。opa632在这个要求很高的应用中提供了优异的性能。其宽的输入输出电压范围,低失真,很好地支持ADS901。OPA632配置为增益+2。输入电平处的374Ω和2.26kΩ电阻器会移动车辆识别号(vin),以便车辆识别号(vin)为0时,车辆识别号(vout)在允许的输出电压范围内。驱动器电路的输入阻抗设置为与50Ω源阻抗匹配。输入电平变换的设计使车辆识别号可以在0V到5V之间,同时将1V到2V的输出电压传送到ADS901。opa632和ads901都有一个断电功能管脚,对于那些需要省电的系统,具有相同的极性。

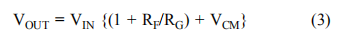

外部参照

ADS901需要引脚22(参考)和引脚24(参考B)上的外部参考。在内部,这些引脚通过电阻梯形图连接,其标称电阻为4kΩ(±15%)。为了在梯形图上建立正确的电压降,外部参考电路通常必须能够提供250微安的电流。利用该电流,ADS901的满标度输入范围设置在+1V和+2V或1VP-P之间。通常,REFT和REFB之间的压降决定ADS901的输入满标度范围(FSR)。公式(4)可用于计算跨度。

根据不同的应用,有几种选择可以在不降低典型性能的情况下为ADS901提供外部参考电压。

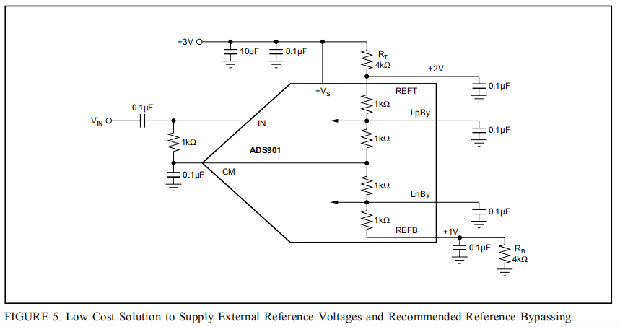

低成本参考溶液

实现所需参考电压的最简单方法是将ADS901的参考梯形图放置在供电轨之间,如图5所示。需要两个附加电阻(RT、RB)来设置通过梯形图的正确电流。但是,根据所需的满标度摆幅和电源电压,可以选择不同的电阻值。

在选择该参考电路时,权衡是由于元件公差和电源变化引起的参考电压变化。在任何情况下,建议使用至少0.1μf陶瓷电容器绕过基准梯形图,如图5所示。电容器有双重用途。它们将绕过时钟馈通和T/H级开关噪声产生的大部分高频瞬态噪声。其次,它们作为电荷库向内部节点提供瞬时电流。

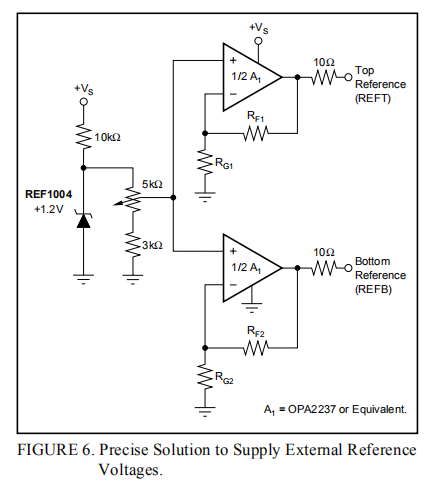

精密参考溶液

对于那些需要更高水平直流精度和漂移的应用,可以使用带有精密参考元件的参考电路(见图6)。一个稳定的+1.2V参考电压由一个双端带隙参考二极管REF1004-1.2建立。使用通用单电源双运算放大器(A1),如OPA2237、OPA2234或OPA2343,可以通过将每个运算放大器设置为适当的增益来生成ADS901所需的两个参考电压;例如:将REFT设置为+2V,将REFB设置为+1V。

时钟输入

ADS901的时钟输入设计为适应+5V或+3V CMOS逻辑电平。为了以最小占空比变化量驱动时钟输入并支持最大采样率(20msps),应使用高速或高级cmos逻辑(hc/hct、ac/act)。当在高采样率下进行数字化时,建议使用具有快速上升和下降时间(2ns或更少)的50%占空比时钟,以满足额定性能规范。然而,ADS901的性能可以承受高达±10%的占空比变化而不会降低。对于输入频率高达奈奎斯特或欠采样应用的应用,必须特别考虑提供具有非常低抖动的时钟。时钟抖动导致孔径抖动(ta),这可能是获得良好信噪比性能的最终限制。方程(5)显示了孔径抖动、输入频率和信噪比之间的关系:

例如,在10MHz满标度输入信号和孔径抖动ta=20ps的情况下,snr是时钟抖动限制为58db。

数字输出

从开始转换信号到有效输出数据有5.0时钟周期数据延迟。标准输出编码是直偏移二进制,其中满标度输入信号对应于输出处的所有“1”。ADS901的数字输出可以通过用逻辑“HI”驱动三态(引脚16)设置为高阻抗状态。正常操作是通过引脚16“lo”实现的,或由于内部下拉电阻器而浮动。此函数用于可测试性目的,但不建议动态使用。

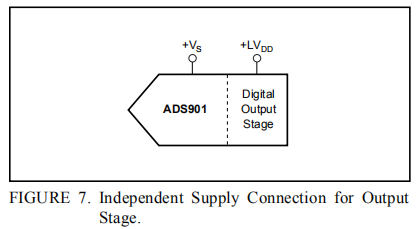

ADS901的数字输出是标准CMOS级,设计为兼容高速TTL和CMOS逻辑系列。逻辑阈值适用于低压cmos:vol=0.4v,voh=2.4v,允许ads901直接与3v逻辑接口。ADS901的数字输出使用专用数字电源引脚(引脚2,LVDD)。通过调节lvdd上的电压,数字输出电平将分别变化。在任何情况下,建议将扇出限制为一个,以保持数据线上的电容负载低于指定的15pF。如有必要,外部缓冲器或锁存器可用于提供额外的好处,将A/D转换器与总线上的任何数字活动隔离,耦合回高频噪声并降低性能。

断电模式

启动掉电模式可以进一步降低ADS901的低功耗。为此,必须将PWRDN引脚(引脚17)连接到逻辑“高”上,以将从电源引出的电流减少约70%。在正常操作中,断电模式由内部下拉电阻器(50KΩ)禁用。

断电时,数字输出设置为3状态。随着时钟的应用,转换器不能准确地处理采样信号。在关闭电源后,以下5个时钟周期的输出数据无效(数据延迟)。

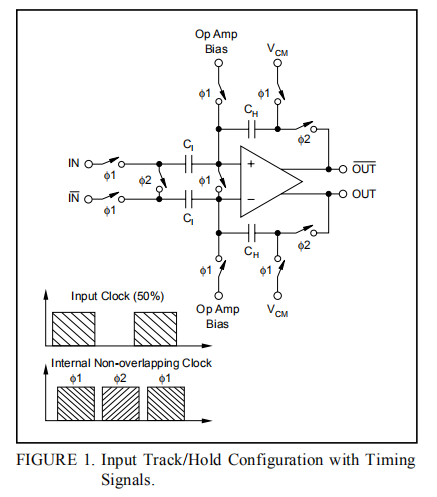

去耦和接地注意事项

ADS901转换器有几个电源管脚,其中一个专用于只提供输出驱动器。其余的电源管脚并不像通常情况那样被分为模拟和数字电源管脚,因为它们在芯片上是内部连接的。因此,建议将转换器视为模拟元件,并仅从模拟电源为其供电。数字电源线通常携带高水平的噪声,这些噪声可以耦合回转换器,并限制可实现的性能。

由于采用流水线结构,转换器还会产生高频瞬态和噪声,反馈到电源线和参考线中。这要求电源和参考引脚被充分旁路。图8显示了模拟电源的推荐去耦方案。在大多数情况下,0.1μf陶瓷芯片电容器足以在宽频率范围内保持低阻抗。它们的有效性在很大程度上取决于接近单个供应管脚。因此,它们应尽可能靠近电源引脚。