W3020点击型号即可查看芯片规格书

1800点击型号即可查看芯片规格书

540点击型号即可查看芯片规格书

描述

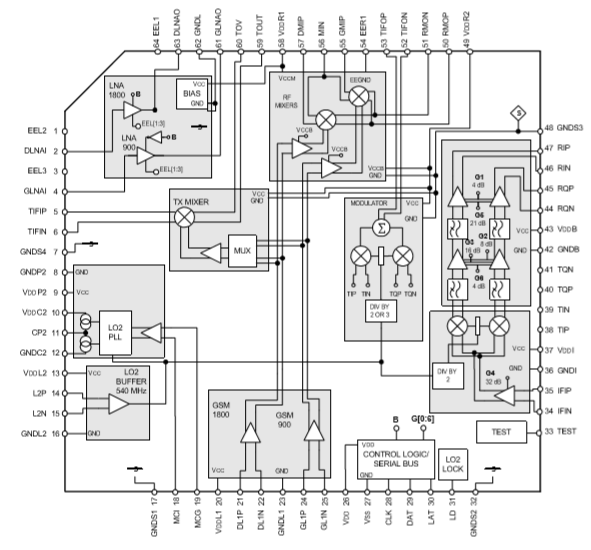

W3020是一款高度集成的GSM收发器,设计用于在双频手机或在900、1800和1900兆赫频段(1900兆赫性能在生产中未经验证)的单频手机中工作。集成电路架构允许射频设计师为三个不同的频段提供解决方案,很少改变PCB,从而提供更快的上市时间和缩短的开发时间。

W3020射频收发器和W3000锁相环与SC1(无线电接口和数字信号处理器)一起设计,以提供完整的GSM蜂窝解决方案。W3020与W3000 UHF高性能PLL IC接口。W3020与W3000结合提供发射机、接收机和频率合成器。添加功率放大器、滤波器和VCO模块完成无线信道。

基带调制信号以差分方式应用于i/q双平衡混频器。为了获得所需的调制频谱掩模,±45°相移本振不需要微调。同时,为了获得高相位精度的信号,I/Q输入信号不需要进行直流偏移校准。来自i/q混频器的if信号输出被求和并输出到外部滤波器,该外部滤波器可降低可互调到接收频带的噪声。然后,该信号被应用到低噪声上变频混频器并被带到rf输出端。

接收信号通过低噪声放大器放大,低噪声放大器与前一滤波器组合,控制接收机灵敏度。然后,该信号通过另一个外部滤波器以将图像频率衰减到可接受的水平。信号通过射频下变频混频器到达中频频率。然后用外部声表面波(saw)滤波器对其进行滤波,使带内阻塞信号达到可接受的水平。信号在接收器的中频带中被放大。中频带包括中频和基带频率的数字增益控制(DGC)放大器和精密低通滤波器。这样可以在消除带内阻塞信号的同时放大信号。精密I/Q解调器将信号分为同相信号和正交信号。I/Q信号经过低通滤波和进一步放大。I/Q放大器包含集成的直流偏移校准电路。输出(I/Q)被馈送至ADC以进行进一步的信号处理。

第二本地振荡器(lo2)包括用于外部压控振荡器(vco)的缓冲器和锁相环(pll),向调制器和接收器的if部分馈送。外部参考源压控晶体振荡器(VCXO)通过计数器从13MHz到1MHz进行划分。1兆赫称为比较频率。540兆赫的VCO频率也被划分为1兆赫。两个信号都被送入相位检测器,产生的误差信号通过外部低通滤波器被送入VCO的控制输入端。

射频收发混频器由两个波段可切换的外部VCO模块驱动,内部缓冲在IC上。VCO都由一个W3000锁相环合成器和环路滤波器控制。使用W3000 PLL中集成的专有缩放技术实现快速带锁。

说明(续)

详细框图

中频/基带放大器

中频放大器是平衡输入/平衡输出类型,并连接到平衡saw滤波器。它由三个增益级组成:一个中频放大器和两个基带放大器。增益可按32、16、8和4db的步骤改变。基带还包含一个电平移位器级,用于直接驱动A/D转换器。电平移位器级有21分贝的增益,可以关闭。以下规格适用于两种操作模式。

中频段的增益通过三线串行总线编程。

中频放大器包含32分贝放大器级,增益为0或32分贝。中频放大器后接固定增益为4db的正交混频器。低通滤波器和解调器之后的第一基带放大器(g3、g2、g6)具有可在0、4、8、12、16、20、24和28db之间选择的增益。使用其他增益步骤,if和基带增益可以在4db步骤中变化64db。第二基带放大器(g5,g1)的增益可在0、4、21和25db之间选择。未测试第二基带放大器部分中的21db增益阶跃,因此不应使用。

中频放大器增益阶跃

基带放大器部分包含将i/q输出处的dc偏移最小化的dc校正电路。基带中的低通滤波器包含用于调谐滤波器截止频率的自校准电路。可选择的增益设置通过

tr寄存器,如编程信息部分所述。滤波器调谐和直流校准也在这一节中解释。

为了达到规定的绝对增益精度,应在室温下校准总增益。这通常是整个手机校准的一部分。绝对增益精度测量相对于室温测量在指定温度范围内的增益变化。在gsm系统中,本规范依赖于所有的rx功能块,而不仅仅是if条。相对增益精度是20分贝范围内增益级精度的测量。在校准32分贝放大器后,确定相对增益精度。

实际收益与请求收益

当32分贝放大器在打开和关闭状态之间切换时,中频带的输入阻抗将略有变化。我们建议在通电状态下将中频带与32分贝放大器匹配,以在输入电平最小时提供与声表面波滤波器的最佳匹配。输入匹配网络可以将中频输入直接匹配到声表面波滤波器或50Ω。

为评估委员会选择了一个与50Ω匹配的网络,以方便实验室测量。为了保持输入阻抗低,并使中频级增益设置之间的阻抗变化最小,在输入端子之间并联一个电阻器。然后,输入网络可以匹配到所需的输入阻抗。(指定的增益包括电阻值500Ω。)出于测试目的,输入已匹配到50Ω,并且if/基带放大器的增益均指50Ω匹配的输入阻抗。I/Q输出端接在高阻抗负载中。增益是电压增益,并将电压增益包含在输入匹配网络的阻抗变换中。

调制器(续)

宽带噪声性能的中频滤波要求

LO2规范

W3020包含用于外部VCO的输入缓冲器和用于在540 MHz下生成第二LO信号的PLL。缓冲器的输出被馈送到接收和发送电路,在接收和发送电路中,信号被分配到if频率。相位噪声包括vco缓冲器对发射和接收电路的贡献。

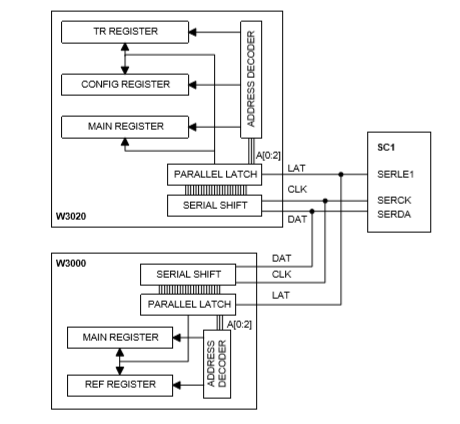

编程信息

W3020和W3000收发器模式(IC RX/TX)以及增益和频带设置使用标准三线总线(时钟、数据、锁存器)编程。W3020和W3000寄存器是可寻址的,因此两个IC可以共享相同的数据、时钟和锁存时间。闩锁行启动当前数据字的下载和执行。

数据字

W3020和W3000芯片通过24位串行字的位内容寻址。一些用于时间关键型交互的词同时处理W3020和W3000,而一些用于初始化的词分别处理W3020和W3000。

W3020通过一条三线串行总线从基带IC获取其所有控制信息。串行数据传输总是由24位组成:3位地址选择5个控制寄存器之一,最多21位数据。当锁存启用信号变高时,数据首先被移位到移位寄存器中,然后在传输完成后并行加载到适当的控制寄存器中。最后一位是紧跟在时钟输入低时发生的从低到高锁存输入转换之前的位。首先加载位24,最后加载位1。四个控制寄存器定义如下:

W3020的发送/接收寄存器。包含用于设置各种发送和接收模式、设置接收增益等的位。预计该寄存器在一帧中会被写入多次。

配置:包含用于控制各种直流偏移校正、滤波器调谐、锁定检测和过载输出等选项的位。预计该寄存器在初始化时会写入一次,然后很少更新。由于它不受上电复位电路的影响,因此在访问W3020芯片时,应首先对该寄存器执行写入操作。此外,建议不要在进行关键操作时更新配置寄存器。

主营:W3000芯片的主计数器和预分频器值。用于在编程W3000时为W3020设置模式和带位函数。

裁判:W3000的参考计数器值。与W3020无关

模式控制

W3020的各种系统模式由模式控制位设置。它们在tr和主寄存器中都是活动的。W3000也将通过W3020在由TR或主寄存器中的模式位设置的任何有效模式中通电。表15给出了每个W3020系统模式的模式位设置。第9页的电源电流表中显示了每种模式下IC的相应典型电源电流。

在睡眠模式下,W3020和W3000都断电,电源电流在微安范围内。在发射突发之前使用发射pll稳定模式,以便通电并锁定lo1和lo2 vco/pll合成器以及连接到调制器电路的相应rf和if lo缓冲器。在此模式下,LO2除以电路保持关闭。类似地,在接收dc校准时隙和随后的接收突发之前使用接收pll设置模式,以便通电并锁定lo1和lo2 vco/pll合成器以及连接到rf混频器和if条的相应rf和if lo缓冲器。在这种模式下,可以通过在配置寄存器中设置C9(在设置期间打开射频混频器)位高来打开射频混频器。发射机开启模式打开所有与发送pll稳定模式相同的电路,同时打开i/q调制器和上变频混频器。

接收器开启模式打开所有与接收pll稳定模式相同的电路,同时打开lna(如果由g0位启用)、rf混频器、if放大器和解调器。当第一次进入接收模式时,如果请求,通过设置tr寄存器中的ftr(滤波器调谐请求)位高和配置寄存器中的c6(滤波器调谐禁用)位低来执行基带lp滤波器调谐(以及低通滤波器调谐部分)。接下来,如果tr寄存器中的ds(dc校正跳过)位低,而配置寄存器中的c5(dc校正禁用)位低,则执行dc偏移校正循环。默认条件是,如果配置寄存器中的C2(直流校准期间的LNA模式)位低,LNA在直流校准期间关闭。另一个默认条件是,如果配置寄存器中的c3(dc校准期间的rx lo1缓冲模式)位低,则在dc校准期间rf混频器lo1缓冲区关闭。

滤波器调谐和直流偏移校正定时

低通滤波器调谐

W3020具有内部校准,以提高低通滤波器带宽的精度。每次向设备施加电源电压并在重启后,应执行滤波器调谐操作。

低通滤波器调谐操作由控制逻辑中的3位控制:n ftr:滤波器调谐请求,在tr寄存器n c4:低通滤波器带宽,在配置寄存器n c6:滤波器调谐禁用,在配置寄存器中

如果滤波器调谐禁用位(c6)编程为高,滤波器带宽设置为编程(标称)值(见表35),并且忽略来自ftr位的任何滤波器调谐请求。

通过执行滤波器调谐校准,可以提高滤波器带宽的精度。可以通过设置tr寄存器中的filter tune request(ftr)位高和配置寄存器中的filter tune disable位(c6)低来执行滤波器调谐。这使得13/4mhz(3.25mhz)时钟能够进入滤波器调谐状态机,然后该状态机运行,直到调谐完成并存储新的滤波器调谐值。过滤优化操作本身需要

兆赫时钟的16.5个周期,或5.1微秒。

滤波器调谐操作应在接收模式下完成。接收模式需要保持激活至少20微秒以允许偏置启动。

如果需要,在滤波器调谐完成后执行直流偏移校准。当与直流偏移校准同时请求时,滤波器调谐操作将在总校准时间上增加5.1微秒。如果在mod位未设置为111时请求滤波器调谐,则仅打开接收偏置电路;其余接收信道保持断电。

滤波器调谐和直流偏移校正定时(续)

直流偏移校准

直流偏移校准操作由配置寄存器和tr寄存器中的几个位控制:n ds:dc校正跳过,仅在tr寄存器n dp:dc预充电,在tr寄存器n c5:dc校正禁用,在配置寄存器n c7:dc粗/精校正,在配置寄存器n dt:dc校正时间,在配置寄存器中

当配置寄存器中的dc校正禁用位(c5)被写入高位时,dc偏移校正电路充电到与0 dc偏移相对应的默认值,并且忽略对dc偏移校正的任何请求。如果dc correction disable=0,则在dc correction skip(ds)和dc precharge only(dp)都较低时,通过将tr(或主)寄存器中的mo位写入值111来启动dc offset校准。与滤波器调谐的情况一样,当偏置电路和输入时钟缓冲器启动时,dc偏移校准的开始被延迟约15μs。

如果在进入RX模式的同时,FTR位也被写入高位,则首先执行滤波器调谐,然后自动开始直流偏移校准。

直流偏移校准运行的时间由配置寄存器中的直流偏移校正时间位dt[0:2]确定。其中有三个位,用户可以选择八个不同的校正时间。

直流偏移校准完成后,3.25兆赫基带时钟停止,自动进入全接收模式,并自动启用LO1缓冲器和LNA(如果g0=1)。

如果在直流预充电(dp=1)设置为高的情况下进入RX模式,则直流偏移电路将通过更短的校准程序,然后自动进入正常接收模式。仅预充电操作的功能与正常校准操作基本相同,因为在预充电操作完成之前,LO1缓冲区和LNA被禁用。仍然会产生15微秒的偏置启动时间。

直流校准期间的接收电路条件也由配置寄存器中的另外两个位控制:直流校准期间n c2:lna开启,直流校准期间高c3:receive lo1 buffer开启,直流校准期间高对于标准直流偏移校准循环和仅直流预充电操作,通过在配置寄存器中设置C2和C3位,可以在LNA和/或LO1缓冲器打开的情况下执行直流偏移校准。

编程示例

这个编程示例演示了如何在通电后对W3020进行编程,以及如何在接收和发送突发信号之前对其进行编程。W3000的参考寄存器是用参考分割比单独初始化的,如W3000数据表中所述