特征

5V电源;50兆赫速度;片上cos查找表片上,10位DAC;串行加载;断电选项;温度范围:-40°C至+85°C;200兆瓦功耗;16导联TSSOP。

应用

频率刺激/波形产生;频率相位调谐和调制;低功耗射频/通信系统;液体和气体流量测量;感官应用:接近、运动和缺陷检测;测试和医疗设备。

一般说明

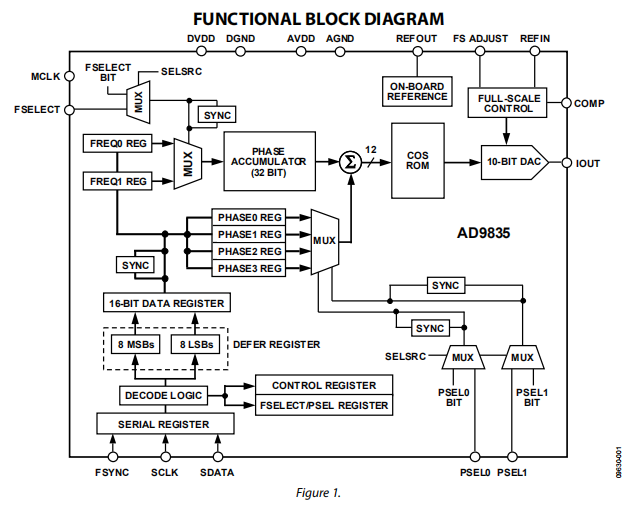

AD9835是一种数控振荡器,采用集成在单个CMOS芯片上的相位累加器、COS查找表和10位数模转换器。为相位调制和频率调制提供调制能力。

支持高达50兆赫的时钟频率。频率精度可以控制在40亿分之一。调制是通过串行接口加载寄存器来实现的。断电位允许用户在不使用AD9835时断电;功耗降低到1.75 mW。该部分可在16导联TSSOP包中获得。

术语

积分非线性

这是任何代码与通过传递函数端点的直线之间的最大偏差。传递函数的端点是零标度,比第一个代码转换(000)低0.5lsb。…00到000。…01)和满标度,最后一个代码转换(111)上方0.5 LSB点。…10到111。…11)。错误以lsb表示。

微分非线性

这是dac中两个相邻码之间测量到的和理想的1lsb变化之间的差。

信号到(噪声+失真)

信噪比(噪声+失真)是在dac的输出端测量的信噪比。信号是基波的有效值大小。噪声是所有非基本信号的均方根和,不超过采样频率(f/2)的一半,但不包括直流分量。信号到(噪声+失真)取决于数字化过程中使用的量化级别的数量;级别越多,量化噪声越小。正弦波输入的理论信噪比由下式给出MCLK

Signal to (Noise + Distortion) = (6.02N + 1.76) dB,其中N是位数。因此,对于理想的10位转换器,Signal to (Noise + Distortion) = 61.96 dB。

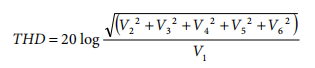

总谐波失真

总谐波失真(thd)是谐波的均方根和基波的均方根值之比。对于AD9835,THD定义为:

其中v是基波的均方根振幅,v1、v2、v3和v4是二次谐波到六次谐波的均方根振幅。

输出符合性

输出一致性是指在dac的输出端可以产生的最大电压,以满足规范要求。当产生大于输出符合性规定的电压时,AD9835可能不符合数据表中列出的规格。

无杂散动态范围

随着感兴趣的频率,基频的谐波和mclk频率的图像出现在dds器件的输出端。无杂散动态范围(sfdr)是指感兴趣频带中存在的最大杂散或谐波。宽频带sfdr给出了最大谐波或杂散的幅度相对于带宽中基频的幅度±2 mhz基频。窄带sfdr给出了在±50khz带宽内最大杂散或谐波在基频附近的衰减。

时钟馈通

将有从MCLK输入到模拟输出的馈通。时钟馈通指的是MCLK信号相对于AD9835输出频谱中基频的幅度。

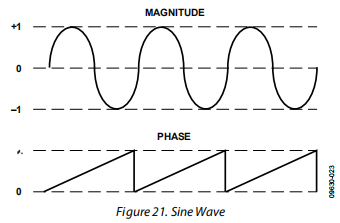

操作理论

正弦波通常是以A(t)=正弦(ωt)的幅值来考虑的。然而,这些都是非线性的,不容易产生,除非通过分段构造。另一方面,角度信息本质上是线性的。也就是说,相位角在每单位时间内以固定角度旋转。角速率取决于信号的频率,传统的速率为ω=2πf。

知道正弦波的相位是线性的,并且给定了一个参考间隔(时钟周期),该周期的相位旋转可以由Δphase=ωδt确定

ω = ΔPhase/δt = 2 πf的求解

求f并用参考时钟频率代替参考周期(1/fMCLK = δt),f = ΔPhase × fMCLK/2 π

AD9835基于这个简单的方程建立输出。一个简单的dds芯片可以用三个主要的子电路实现这个方程。

电路说明

AD9835为射频通信系统设计师提供了令人兴奋的集成水平。AD9835在单个集成电路上集成了数控振荡器(NCO)、COS查找表、频率和相位调制器以及数模转换器。

AD9835的内部电路由三个主要部分组成。这些是数控振荡器(NCO)和相位调制器;COS查找表;数模转换器。

AD9835是一款完全集成的直接数字合成(DDS)芯片。该芯片需要一个参考时钟、一个低精度电阻和八个去耦电容器,以提供高达25兆赫的数字处理正弦波。除了产生这种射频信号外,该芯片完全能够实现广泛的简单和复杂调制方案。这些调制方案完全在数字域中实现,允许使用dsp技术精确而简单地实现复杂的调制算法。

数控振荡器和相位调制器

这包括两个频率选择寄存器、一个相位累加器和四个相位偏移寄存器。nco的主要部件是一个32位的相位累加器,它将输出信号的相位成分组合起来。连续时间信号的相位范围为0π到2π。在这个数字范围之外,正弦函数以周期性的方式重复它们自己。

数字实现也不例外。累加器只是将相号的范围缩放成一个多位数字字。AD9835中的相位累加器是用32位实现的。因此,在AD9835中,2π=2。同样,将Δ相位项标度到0 < ΔPhase < 232 − 1的数字范围内。把这些代换成f = ΔPhase × fMCLK/232

哪里:0 < ΔPhase < 232,相位累加器的输入(即相位步进)可以从freq0寄存器或freq1寄存器中选择,这由fselect管脚或fselect位控制。nco固有地产生连续相位信号,从而避免了在频率之间切换时的任何输出不连续性。

在nco之后,可以添加相位偏移以使用12位相位寄存器执行相位调制。这个寄存器的内容被加到nco的最高有效位上。AD9835有四个相位寄存器,这些寄存器的分辨率为2π/4096。

cos查找表(lut)为了使输出有用,信号必须从相位信息转换成正弦值。由于相位信息直接映射成振幅,rom lut将相位信息转换成振幅。为此,使用数字相位信息来寻址cos-rom lut。尽管nco包含32位相位累加器,但nco的输出被截断为12位。使用相位累加器的完全分辨率是不切实际和不必要的,因为这需要一个包含2个条目的查找表。

只需要在lut中具有足够的相位分辨率,使得输出波形的dc误差由dac中的量化误差控制。这要求查找表的相位分辨率比10位DAC多2位。

数模转换器

AD9835包括一个高阻抗电流源10位DAC,能够以不同速度驱动广泛的负载。通过使用单个外部电阻器(R),可以调整满标度输出电流,以达到最佳功率和外部负载要求。集合

DAC配置为单端操作。负载电阻可以是所需的任何值,只要其上产生的满标度电压不超过电压符合范围。由于满标度电流由R控制,对R的调整可以平衡对负载电阻的变化。然而,如果dac满标度输出电流显著小于4ma,dac的线性度可能降低。集合集合

功能描述

串行接口

AD9835有一个串行接口,每个写入周期加载16位。sclk、sdata和fsync用于将单词加载到ad9835中。

当fsync变低时,ad9835被告知正在向设备写入一个字。第一个位在下一个SCLK下降沿读入设备,其余位在下一个SCLK下降沿读入设备。fsync帧16位;因此,当出现16个sclk下降边缘时,fsync应再次变高。SCLK可以是表5。写入AD9835数据寄存器连续或可选地,SCLK可以在两次写入操作之间高或低空闲。当写入频率/相位寄存器时,前四位标识是否写入频率或相位寄存器,后四位包含目标寄存器的地址,而8个lsb包含数据。

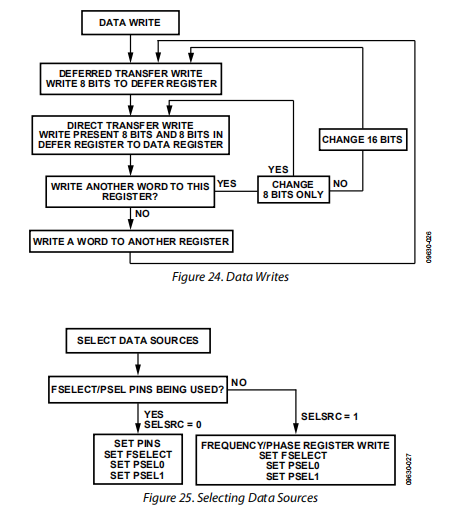

直接数据传输和延迟数据传输

在AD9835中,加载目标频率/相位寄存器时使用16位传输。加载寄存器有两种模式:直接数据传输和延迟数据传输。通过延迟数据传输,8位字被加载到延迟寄存器(8个lsb或8个msbs)中。但是,此数据不会加载到16位数据寄存器中;因此,目标寄存器不会更新。通过直接数据传输,8位字被加载到适当的延迟寄存器(8个lsb或8个msbs)中。

加载延迟寄存器后,立即将完整延迟寄存器的内容加载到16位数据寄存器中,并在下一个mclk上升沿加载目标寄存器。当目标寄存器被寻址时,首先需要延迟传输,然后是直接传输。当延迟寄存器的所有16位都包含相关数据时,可以使用8位加载而不是16位加载来更新目标寄存器,即可以使用直接数据传输。

例如,在一个新的16位字被加载到一个目标寄存器之后,延迟寄存器也将包含这个字。如果下一条写指令是指向同一个目标寄存器,则用户可以立即使用直接数据传输。

当写入相位寄存器时,加载到数据寄存器中的16位字的4个msbs应为零(相位寄存器的宽度为12位)。

要改变频率寄存器的全部内容,需要四个写操作。但是,频率字的16个msb包含在16个lsb的单独寄存器中。因此,可以独立于16个lsb改变频率字的16个msbs。

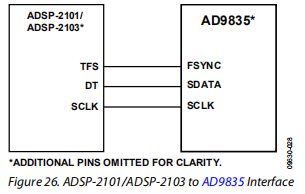

使用fselect、psel0和psel1管脚选择要使用的相位和频率寄存器,或者可以使用相应的位。bit selsrc确定是使用位还是管脚。当selsrc=0时,使用管脚;当selsrc=1时,使用位。当CLR设置为高时,selsrc设置为0,这样管脚就是默认源。从串行(延迟)寄存器到16位数据寄存器以及fselect和psel寄存器的数据传输发生在第16个下降sclk边缘之后。

1X=不在乎。

在下一个mclk上升沿上发生从16位数据寄存器到目的寄存器或从fselect/psel寄存器到相应复用器的数据传输。由于sclk和mclk是异步的,当数据位处于过渡状态时,mclk上升沿可能发生。如果要写入的寄存器正在生成dac输出,这可能会导致短暂的假dac输出。为了避免这种杂散输出,AD9835包含同步电路。

当sync位设置为1时,同步器被启用,数据从串行寄存器(延迟寄存器)传输到16位数据寄存器,fselect/psel寄存器在mclk下降沿上触发的两级管道延迟之后发生。管道延迟确保传输发生时数据有效。类似地,当sync=1时,使用fselect/pselx管脚选择频率/相位寄存器与mclk上升沿同步。当sync=0时,将绕过同步器。

当sync=1时,使用管脚选择频率/相位寄存器在内部与mclk同步,以确保这些输入在mclk上升沿有效。如果满足时间t和t,则输入将在mclk上升沿处处于稳定状态。但是,如果违反时间和时间,内部同步电路将延迟引脚采样的瞬间,确保输入在采样瞬间有效。

等待时间

与每个操作关联的是一个延迟。当输入fselect/psel改变值时,在控制传输到所选寄存器之前有一个管道延迟;在模拟输出由所选寄存器控制之前有一个管道延迟。当满足时间t和t时,当sync=0时,psel0、psel1和fselect具有6个mclk周期的延迟。

当sync=1时,延迟增加到8 mclk个周期。当时间t和t不满足时,延迟可以增加一个mclk周期。类似地,每个写操作都有一个延迟。如果选择的频率/相位寄存器加载了一个新字,则在模拟输出改变之前,有6到7个mclk周期的延迟(关于将数据加载到目标寄存器的mclk上升沿,有一个mclk周期的不确定性)。当sync=1时,延迟为8或9 mclk个周期。

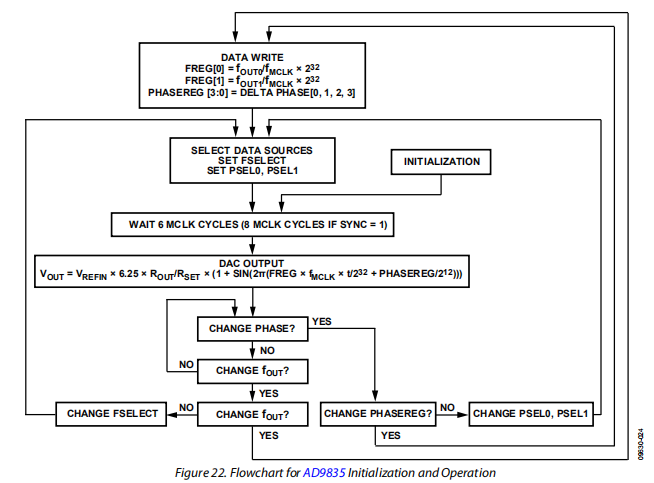

流程图

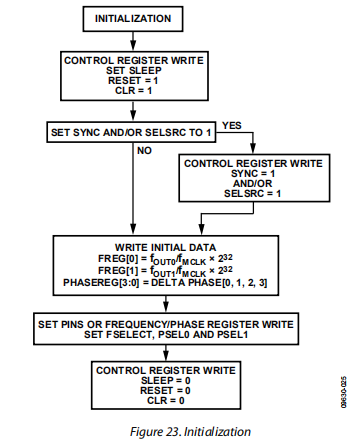

图22中的流程图显示了AD9835的操作程序。当AD9835通电时,该部分应重置,这将相位累加器重置为零,以便模拟输出处于中刻度。为避免在初始化AD9835时产生虚假的DAC输出,复位位应设置为1,直到部件准备好开始产生输出。将clr high设置sync和selsrc为0,以便使用fselect/pselx管脚选择频率/相位寄存器,并绕过同步电路。需要对sync/selsrc寄存器执行写操作,以启用同步电路或将控制更改为fselect/psel位。

复位不复位相位和频率寄存器。这些寄存器将包含无效数据,因此用户应将其设置为已知值。然后将重置位设置为0以开始生成输出。复位设置为0后,DAC输出6 mclk周期将出现一个信号。

模拟输出为f/2×freg,其中freg是加载到所选频率寄存器中的值。该信号按所选相位寄存器(2π/4096×Phasex Reg,其中Phasex Reg是所选相位寄存器中包含的值)中指定的量进行相移。MCLK32频率/相位寄存器的控制可以从管脚交换到位。

应用程序信息

AD9835包含使其适合调制应用的功能。该部分可用于进行fsk等简单调制。更复杂的调制方案,例如gmsk和qpsk,也可以使用ad9835来实现。在fsk应用中,ad9835的两个频率寄存器加载不同的值;一个频率表示空间频率,另一个表示标记频率。数字数据流被馈送到fselect管脚,这将导致ad9835在两个值之间调制载波频率。

AD9835有四个相位寄存器;这使部件能够执行PSK。通过相移键控,载波频率相移,相位改变与输入到调制器的比特流相关的量。四个移位寄存器的存在简化了dsp和ad9835之间所需的交互。

AD9835也适用于信号发生器应用。由于其低电流消耗,该部分适合用作本振器的应用。

接地及布置

容纳AD9835的印刷电路板的设计应使模拟和数字部分分开并限制在板的某些区域。这有助于使用易于分离的地平面。最小蚀刻技术通常对地平面最好,因为它提供了最好的屏蔽。数字和模拟地面只能在一个地方连接。如果AD9835是唯一需要AgNd到DGNd连接的设备,则接地平面应连接在AD9835的AgNd和DGNd管脚处。如果AD9835处于多个设备需要AGND到DGND连接的系统中,则应仅在一个点进行连接,即应在尽可能靠近AD9835的位置建立星形接地点。

避免在设备下运行数字线路,因为这会将噪声耦合到模具上。模拟接地平面应允许在AD9835下运行,以避免噪声耦合。AD9835的电源线应使用尽可能大的轨道,以提供低阻抗路径,并减少故障对电源线的影响。时钟等快速开关信号应使用数字接地屏蔽,以避免将噪声辐射到电路板的其他部分。避免数字和模拟信号交叉。板的相对侧上的痕迹应彼此成直角。这将减少通过电路板的馈通效应。到目前为止,微带技术是最好的,但在双面板上并不总是可行的。在这种技术中,电路板的组件侧专用于地面,而信号则放置在另一侧。

良好的脱钩很重要。AD9835的模拟和数字电源是独立的,并且分开固定,以最小化装置的模拟和数字部分之间的耦合。所有模拟和数字电源应分别与agnd和dgnd断开,0.1 mf陶瓷电容器与10 mf钽电容器并联。为了从去耦电容器中获得最佳效果,它们应尽可能靠近设备放置,理想情况下应正好靠在设备上。在使用公共电源驱动AD9835的AVDD和DVD的系统中,建议使用系统的AVDD电源。该电源应在AD9835和AGND的AVDD管脚之间具有推荐的模拟电源去耦,在DVD管脚和DGND之间具有推荐的数字电源去耦电容。

AD9835与微处理器的接口

AD9835有一个标准串行接口,允许部件直接与多个微处理器接口。设备使用外部串行时钟将数据/控制信息写入设备。串行时钟的频率最高可达20兆赫。串行时钟可以是连续的,也可以在两次写入操作之间高或低空闲。当数据/控制信息被写入ad9835时,fsync被取低并保持低,而16位数据被写入ad9835。fsync信号帧16位信息被加载到ad9835中。

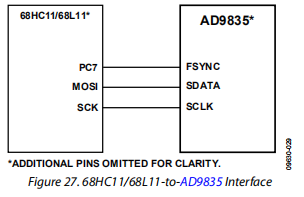

AD9835-TO-ADSP-21XX接口

图26显示了AD9835和ADSP-21xx之间的串行接口。ADSP-21XX应设置为在运动传输交替帧模式(TFSW=1)下工作。ADSP-21XX通过运动控制寄存器编程,应配置如下:内部时钟操作(ISCLK=1)、活动低帧(INVTFs=1)、16位字长(SLEN=15)、内部帧同步信号(ITFs=1)、为每个写入操作生成帧同步(TFSR=1)。在启用运动后,通过将一个字写入TX寄存器来启动传输。数据在串行时钟的每个上升沿上计时,并在SCLK下降沿上计时到AD9835。

AD9835-to-68HC11/68L11接口

图27显示了AD9835和68HC11/68L11微控制器之间的串行接口。通过将spcr中的位mstr设置为1,微控制器被配置为主控制器,这在sck上提供串行时钟,而mosi输出驱动串行数据线sdata。由于微控制器没有专用的帧同步管脚,fsync信号来自端口线(pc7)。正确操作接口的设置条件如下:SCK在两次写入操作之间高空闲(cpol=0),数据在SCK下降沿上有效(cpha=1)。当数据被传送到ad9835时,fsync线被取低(pc7)。68HC11/68L11的串行数据以8位字节传输,在传输周期中仅出现8个下降的时钟边缘。首先传输数据msb。为了将数据加载到ad9835中,在前8位被传输并且对ad9835执行第二串行写入操作之后,pc7被保持在低位。只有在第二个8位被传输之后,fsync才应该被再次调高。

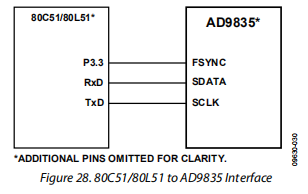

AD9835-to-80C51/80L51接口

图28显示了AD9835和80C51/80L51微控制器之间的串行接口。微控制器在模式0下工作,以便80C51/80L51的TXD驱动AD9835的SCLK,而RXD驱动串行数据线SData。fsync信号再次来自端口上的位可编程管脚(图中使用的是p3.3)。当数据要传输到aad9835时,p3.3取低。80c51/80l51以8位字节发送数据,因此,在每个周期中仅出现8个下降的sclk边缘。

为了将剩余的8位加载到ad9835,p3.3在前8位被发送之后保持低位,并且启动第二写操作来发送第二字节的数据。在第二次写入操作完成后,P3.3被取高。SCLK应在两次写入操作之间高空闲。80c51/80l51以首先具有lsb的格式输出串行数据。AD9835首先接受msb(4个msb是控制信息,接下来的4位是地址,而8个lsb在写入目标寄存器时包含数据)。因此,80c51/80l51的发送例程必须考虑到这一点,并重新排列位,以便首先输出msb。

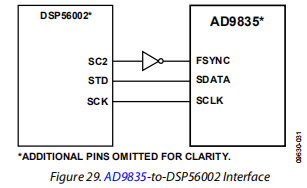

AD9835-to-DSP56002接口

图29显示了AD9835和DSP56002之间的接口。DSP56002配置为具有门控内部时钟(syn=0,gck=1,sckd=1)的正常模式异步操作。帧同步管脚在内部生成(sc2=1),传输宽度为16位(wl1=1,wl0=0),帧同步信号将帧16位(fsl=0)。

帧同步信号在管脚sc2上可用,但在应用于ad9835之前需要反转。DSP56000/DSP56001的接口与DSP56002的接口类似。

评估委员会

系统演示平台

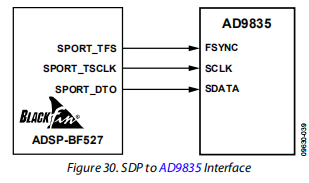

系统演示平台(SDP)是一种硬件和软件评估工具,可与产品评估板一起使用。SDP板基于Blackfin®BF527处理器,通过USB 2.0高速端口与PC相连。请注意,SDP板与AD9835评估板分开出售。

AD9835至运动接口

模拟设备SDP板有一个运动串行端口,用于控制AD9835的串行输入。连接如图30所示。

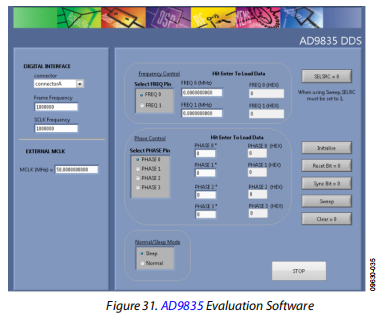

AD9835评估板允许设计者以最小的努力评估高性能AD9835 DDS调制器。AD9835评估板的图形用户界面如图31所示。

DDS评估工具包包括一个填充的、经过测试的AD9835 PCB。评估板提供软件,使用户可以轻松编程AD9835。AD9835评估板的示意图和布局如图32至图36所示。

AD9835可以在最高50兆赫的主时钟下工作。评估板上包括一个50兆赫通用振荡器。然而,可以移除该振荡器,并且如果需要,可以将外部cmos时钟连接到该部件。

一般振荡器有两种选择:AEL 301系列晶体振荡器(AEL晶体有限公司);SG-310SCN振荡器(爱普生丰田公司)。

电源

AD9835评估板的电源可以通过USB连接器提供,也可以通过引脚连接从外部提供。电源线应扭曲以减少接地回路。