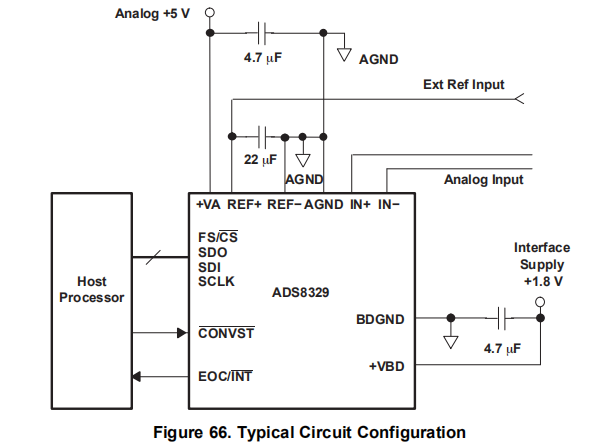

ADS8329/30是一种使用外部基准的高速、低功耗、逐次逼近寄存器(SAR)模数转换器(ADC)。该体系结构基于电荷再分配,它固有地包括一个采样/保持功能。

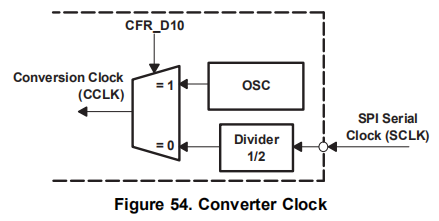

ADS8329/30有一个内部时钟,用于运行转换,但也可以编程运行基于外部串行时钟SCLK的转换。

ADS8329有一个模拟输入。模拟输入提供给两个输入引脚:+in和–in。当转换开始时,这些引脚上的差分输入在内部电容器阵列上采样。在转换过程中,+in和–in输入都与任何内部功能断开。

ADS8330有两个输入端。两个输入共享相同的公共管脚COM。负输入与ADS8329的–in引脚相同。ADS8330可编程为手动选择频道,也可编程为自动频道选择模式,在频道0和1之间自动扫描。

模拟输入

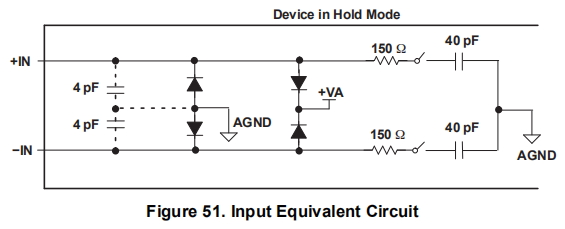

当转换器进入保持模式时,+in和–in输入之间的电压差被捕捉到内部电容器阵列上。输入端的电压限制在agnd–0.2v和agnd+0.2v之间,允许输入端拒绝与输入端相同的小信号。+In输入的范围为-0.2 V至Vref+0.2 V。输入范围[+In–(–In)]限制为0 V至Vref。

通过模拟输入的(峰值)输入电流取决于许多因素:采样率、输入电压和源阻抗。进入ADS8329/30的电流在采样期间为内部电容器阵列充电。该电容充满电后,不再有输入电流。模拟输入电压源必须能够在最小采集时间(120 ns)内将输入电容(45 pF)充电至16位稳定水平。当转换器进入保持模式时,输入阻抗大于1 GΩ。

必须注意绝对模拟输入电压。为保持转换器的线性,+in和–in输入和量程[+in-(–in)]应在规定的范围内。在这些范围之外,转换器的线性度可能不符合规范。为了减少噪声,应使用低通滤波器的低带宽输入信号。应注意确保驱动+输入和-输入的源的输出阻抗匹配。如果没有观察到这一点,两个输入可能有不同的沉降时间。这可能导致偏移误差、增益误差和线性误差,这些误差随温度和输入电压而变化。

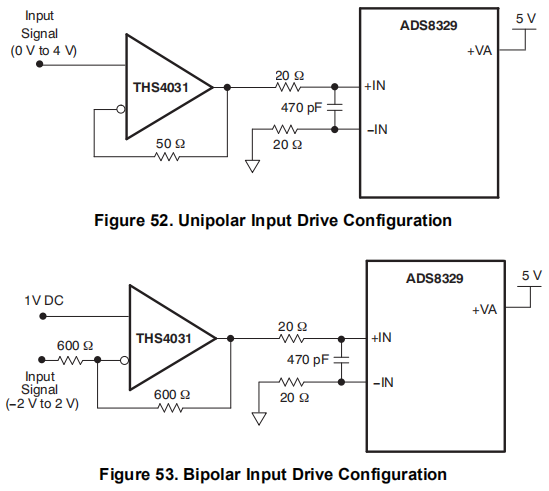

驱动放大器选择

转换器的模拟输入需要用低噪声的运算放大器驱动,如ths4031或opa365。建议在输入管脚处安装RC滤波器,以低通滤除源噪声。建议使用两个20Ω的电阻器和一个470 pF的电容器。转换器的输入是0 V至Vref范围内的单极输入电压。驱动运算放大器的最小–3dB带宽可计算为:f3db = (ln(2) ×(n+1))/(2π × tACQ)

当n等于16时,adc的分辨率(对于ads8329/30)。当tacq=120ns(最小捕获时间)时,驱动放大器的最小带宽为15.6mhz。如果应用程序增加了采集时间,则可以放宽带宽。建议使用德克萨斯仪器公司的OPA365、OPA827或THS4031。源极跟随器配置中用于驱动转换器的ths4031如典型输入驱动配置所示,图52。对于ADS8330,COM引脚上应使用0Ω的串联电阻(或根本不使用电阻)。

双极到单极驱动器

在输入为双极性的系统中,ths4031可以在反向配置中使用,并且对其+输入施加额外的直流偏置,以使对ads8329/30的输入保持在其额定工作电压范围内。当ADS8329/30用于需要良好信噪比和THD性能的信号处理应用时,也建议使用这种配置。直流偏置可以从ref3225或ref3240参考电压ic导出。图53所示的输入配置能够在10 kHz的输入频率下提供优于91 dB的信噪比和-96 dB的总谐波失真。如果使用带通滤波器对输入进行滤波,则应注意确保带通滤波器输入处的信号摆动较小,以使滤波器引入的失真最小。在这种情况下,可以增加图53所示电路的增益,以保持对ads8329/30的输入大,以保持系统的信噪比高。注意,在这种配置中,从+input到ths4031的输出的系统增益是ac信号增益的函数。电阻分压器可用于缩放ref3225或ref3240的输出,以将直流输入处的电压降低至ths4031,以将转换器输入处的电压保持在其额定工作范围内。

参考文献

ADS8329/30可以在0.3V到5V的范围内与外部参考电压一起工作。为确保转换器的良好性能,需要在该引脚上提供干净、低噪声、良好的解耦参考电压。像ref3240这样的低噪声带隙基准可以用来驱动这个引脚。转换器的REF+和REF-引脚之间需要一个22μF陶瓷去耦电容器。这些电容器应尽可能靠近装置的引脚。REF-应通过尽可能短的距离连接到模拟接地平面。

变频器运行

ADS8329/30有一个振荡器,用作控制转换率的内部时钟。这个时钟的频率最小为21mhz。除非设备处于深度断电状态,或设备被编程为使用SCLK作为转换时钟(CCLK),否则振荡器始终打开。最小采集(采样)时间需要3个cclks(在24.5mhz时相当于120ns),转换时间需要18个转换时钟(cclk)(约780ns)来完成一次转换。

如果需要的话,还可以根据外部串行时钟sclk编程运行转换。这允许系统设计器实现系统同步。串行时钟sclk在用作转换时钟(cclk)之前,首先被降低到其频率的1/2。例如,对于42mhz sclk,这为转换提供了21mhz时钟。如果当外部sclk被编程为转换时钟(cclk)的源时,需要在sclk的特定上升沿开始转换(并且选择了手动开始转换),则应观察convst和该上升sclk沿之间的设置时间。这可确保在18个CCLK(或36个SCLK)中完成转换。最小设置时间为20 ns,以确保convst和sclk之间的同步。在许多情况下,转换可以在一个sclk周期(或cclk)后开始,从而导致19 cclk(或37 sclk)转换。一旦同步放松,就不需要20 ns的设置时间。

sclk的占空比只要满足8ns的最小高低时间要求,就不是关键。由于ADS8329/30是为高速应用而设计的,因此必须提供更高的串行时钟(SCLK)才能通过串行接口维持高吞吐量,因此SCLK的时钟周期必须不超过1微秒(用作转换时钟(CCLK))。最小时钟频率也由ADS8329/30内部的电容数字模拟(CDAC)电容器的寄生泄漏控制。

手动频道选择模式

转换周期开始于通过向命令寄存器(cmr)写入通道号来选择采集通道。这个周期时间可以短到4个串行时钟(SCLK)。

自动频道选择模式

如果启用自动频道选择模式,也可以自动完成频道选择。这是默认的频道选择模式。双通道转换器ADS8330有一个内置的2对1多路复用器。如果设备编程为自动通道选择模式,则以固定顺序采集来自通道0和通道1的信号。在下一个循环中,在配置了cfr_d11至1用于自动通道选择模式的命令循环之后,首先访问通道0。此自动访问在将cfr_d11设置为的命令循环之后停止循环0.

开始转换

采集结束或采样实例(EOS)与转换开始时相同。这是通过将convst引脚调低至少40 ns来启动的。在满足最低要求后,可将convst销调高。convst独立于fs/cs,因此可以在需要多个转换器同时采样/保持的应用中使用一个公共convst。ADS8329/30在convst信号的下降沿上从采样模式切换到保持模式。ADS8329/30需要18个转换时钟(CCLK)边缘才能完成转换。转换时间相当于1500ns,内部时钟为12mhz。两个连续convst信号之间的最小时间为21 cclks。

如果是这样编程的(cfr_d9=0),也可以在不使用convst的情况下启动转换。当转换器被配置为自动触发时,下一个转换在转换结束后自动启动3个转换时钟(cclk)。这3个转换时钟(cclk)用作采集时间。在这种情况下,完成一个采集和转换周期的时间是21 cclks。

状态输出eoc/int

当状态管脚编程为EOC且极性设置为激活低时,管脚按以下方式工作:当编程为手动触发器时,CONVST变低后,EOC输出立即变低。在整个转换过程中,EOC保持在低位,转换结束时返回高位。如果自动触发已编程,EOC输出在EOC的前一上升沿后低3个转换时钟(CCLK)。

此状态引脚可编程。当低时间等于转换时间时,它可以用作EOC输出(cfr_d[7:6]=1,1)。此状态管脚可用作int(cfr_d[7:6]=1,0),在转换结束时设置为低,在下一个读取循环中将其设置为高(清除)。此引脚的极性,用作任一功能(EOC或INT),可通过cfr_d7编程。

断电模式

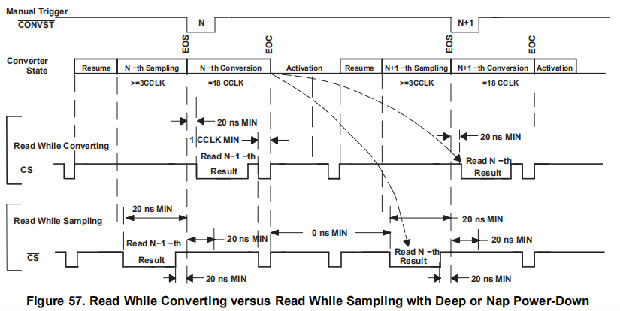

ADS8329/30具有全面的内置断电功能。有三种关机模式:深度关机模式、NAP关机模式和自动NAP关机模式。通过设置相关的cfr位,可启用所有三种断电模式。前两种断电模式在启用时激活。唤醒命令1011b可以从断电模式恢复设备操作。自动关机模式的工作原理略有不同。当转换器在自动NAP关机模式下启用时,转换结束实例(EOC)会将设备置于自动NAP关机状态。采样开始将恢复转换器的操作。配置寄存器的内容不受任何断电模式的影响。当启动NAP或深度断电时,任何正在进行的转换都将中止。

深功率下降模式

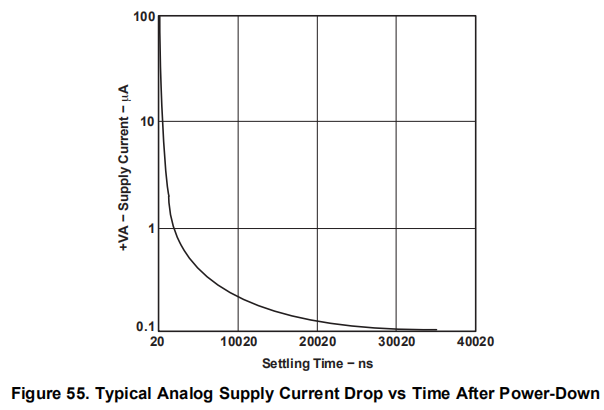

通过写入配置寄存器位cfr_d2,可以激活深度断电模式。当设备处于深度断电模式时,除接口外的所有块都处于断电状态。外部SCLK被阻塞到模拟块。模拟块不再有偏置电流,内部振荡器关闭。在此模式下,电源电流在100 ns内从7毫安降至4毫安。断电后的唤醒时间为1微秒。当配置寄存器中的位d2设置为0时,设备处于深度断电状态。将此位设置为1或发送唤醒命令可以使转换器从深度断电状态恢复。

午睡模式

在NAP模式下,ADS8329/230关闭比较器和中压缓冲器的偏置。在此模式下,电源电流在正常模式下从7毫安降至配置周期后200 ns内的约0.3毫安。从NAP关机模式唤醒(恢复)时间为3 cclks(120 ns,24.5兆赫转换时钟)。一旦控制寄存器中的cfr_d3位设置为0,无论转换状态如何,设备都将进入nap掉电模式。将此位设置为1或发送唤醒命令可以使转换器从NAP关机状态恢复。

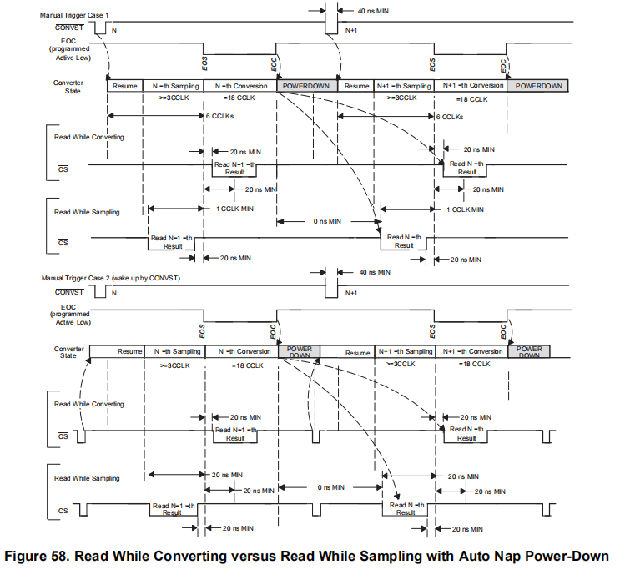

自动捕捉模式

自动捕捉模式几乎与捕捉模式相同。唯一的区别是设备实际断电的时间和唤醒设备的方法。配置寄存器位d4仅用于启用/禁用自动NAP模式。如果启用了自动捕捉模式,则设备在转换完成后关闭偏置,这意味着转换结束将激活自动捕捉关机模式。电源电流在正常模式下从7毫安下降到200毫安左右。convst恢复设备并在3个cclks(120 ns,24.5兆赫转换时钟)中再次打开偏压。当配置寄存器的位d4设置为1时,也可以通过禁用自动NAP模式唤醒设备。任何通道选择命令0xxxb、唤醒命令或设置默认模式命令1111b也可以从自动关闭NAP电源唤醒设备。

注:1、此唤醒命令是命令字中的字1011b。此命令将配置寄存器中的位d2和d3设置为1,而不是d4。但是,唤醒命令确实会将设备从这些关机状态中的任何一个状态(deep/nap/auto nap power down)中删除。2、唤醒时间定义为主机处理器尝试唤醒转换器与转换启动之间的时间。

总采集+转换周期时间:

自动:=21 cclks;手动:≥21 cclks;

手动+深度≥4sclk+100微秒+3 cclk+18 cclk+16 sclk+1微秒断电:

手动+NAP断电:≥4 SCLK+3 CCLK+3 CCLK+18 CCLK+16 SCLK;

手动+自动NAP≥4 SCLK+3 CCLK+3 CCLK+18 CCLK+16 SCLK(使用唤醒恢复)断电:

手动+自动NAP≥1 cclk+3 cclk+3 cclk+18 cclk+16 sclk(使用convst恢复)断电:

数字接口

串行时钟设计用于容纳SCLK频率高达50MHz的最新高速处理器。每个循环都是从fs/cs的下降沿开始的。内部数据寄存器的内容,它可供位于eoc的输出寄存器使用,显示在fs/cs下降沿的sdo输出管脚上。这是msb。输出数据在具有TD(SCLKF-SDovalid)延迟的SCLK下降沿有效,以便主机处理器可以在下降沿读取。串行数据输入也在SCLK的下降沿读取。

完整的串行I/O循环从FS/CS下降沿之后的SCLK第一个下降沿开始并结束16(见注)SCLK下降边缘。串行接口非常灵活。它与cpol=0、cpha=1或cpol=1、cpha=0一起工作。这意味着当sclk较高时,fs/cs的下降沿可能下降。同样的松弛也适用于fs/cs的上升沿,其中sclk可能高或低,只要最后一个sclk下降沿发生在fs/cs的上升沿之前。

注:在某些情况下,根据读取模式组合,一个周期为4个SCLK或最多24个SCLK。

内部寄存器

内部寄存器由两部分组成,4位用于命令寄存器(CMR),12位用于配置数据寄存器(CFR)。

写入转换器

有两种不同类型的寄存器写入,一种是对cmr的4位写入,另一种是对cmr加cfr的16位完全写入。命令集列在表3中。一个简单的命令只需要4个SCLK,写入在SCLK的第4个下降沿生效。16位写入或读取至少需要16个SCLK。

配置转换器和默认模式

转换器可以使用命令1110b(写入cfr)或命令1111b(默认模式)进行配置。对cfr的写入需要4位命令,然后是12位数据。4位命令在SCLK的第4个下降沿生效。cfr写入在sclk的第16个下降沿生效。

默认模式命令可以通过简单地将sdi绑定到+vbd来实现。一旦芯片被选中,SCLK至少会记录4个1s。cfr的默认值在sclk的第四个下降沿加载到cfr中。

cfr默认值均为1s(除了cfr_d1,此位被ADS8329忽略,并且始终读取为0)。相同的默认值适用于通电复位(por)和开关复位后的cfr。

读取配置寄存器

主机处理器可以通过发出命令1100b来读取在cfr中编程的值。该定时与读取转换结果类似,只是convst未使用,并且eoc/int管脚上没有活动。读取的cfr值包含转换数据的前四个msbs加上有效的12位cfr内容。

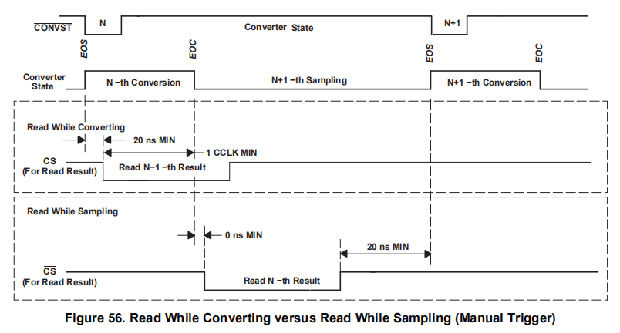

读取转换结果

转换结果可用于EOC处输出数据寄存器(ODR)的输入,并在CS或FS的下一个下降沿处呈现给输出寄存器的输出。然后,主机处理器可以随时通过SDO引脚将数据移出,除了在安静区域。这是取样结束(EOS)前20 ns和后20 ns。采样结束(EOS)定义为使用手动触发器时convst的下降沿,如果使用自动触发器,则定义为EOC之后的第三转换时钟(CCLK)的结束。

fs/cs的下降沿不应放置在转换结束时的精确时刻(至少一个转换时钟(cclk)延迟)(默认情况下,当eoc变高时),否则数据损坏。如果fs/cs放在转换结束之前,则读取先前的转换结果。如果在转换结束后放置fs/cs,则读取当前转换结果。

转换结果是16位数据,采用直接二进制格式,如表4所示。通常需要16个SCLK,但需要16个以上SCLK的情况除外(见表6)。串行输出(SDO)的数据输出首先是左调整的msb。尾随位先用标记位(如果启用)加上所有零填充。在fs/cs再次升高之前,sdo保持低位。当fs/cs较低时,sdo处于活动状态。fs/cs 3的上升沿表示sdo输出。

注:当sdo不在3状态时(当fs/cs低且sclk正在运行时),转换结果的一部分在sdo管脚处输出。位数取决于提供了多少SCLK。例如,手动选择通道命令周期需要4个SCLK,因此SDO输出4个转换结果的msbs。例外情况是SDO在任何复位(PoR或软件复位)后立即输出循环中的所有1s。

如果使用sclk作为转换时钟(cclk),并且使用连续sclk,则在采样时间(6 sclk)期间,由于静默区要求,不可能将所有16个sdo位都打卡。在这种情况下,最好在转换期间读取转换结果(36个SCLK或48个SCLK处于自动休眠模式)。

标签模式

ads8330包括一个特性tag,它可以用作一个tag来指示哪个信道是转换结果的来源。在从sdo读取lsb之后添加一个地址位,指示如果启用了标记模式,结果来自哪个通道。通道0的地址位为0,通道1的地址位为1。转换器需要的sclk超过4位命令所需的16个,加上12位cfr或16个数据位(因为附加了标记位)。

链模式

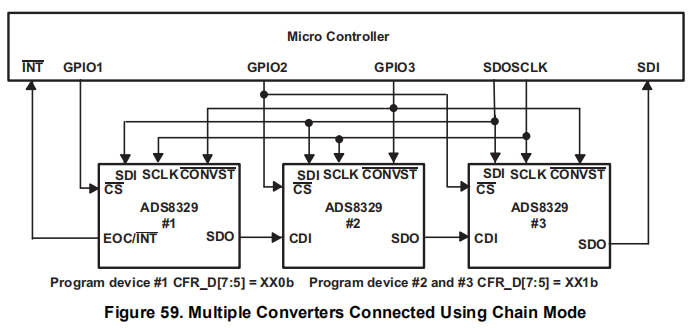

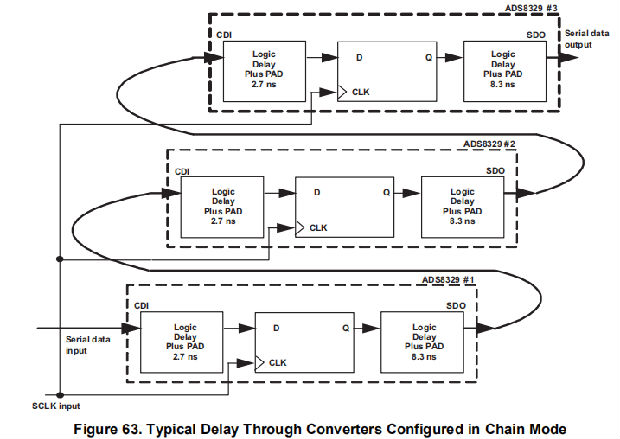

ADS8329/30可以作为单个转换器或在具有多个转换器的系统中工作。当使用多个转换器时,系统设计者可以利用简单的高速spi兼容串行接口,将它们串联在一个链中。cfr中的一个位用于将eoc/int状态pin重新配置为次级串行数据输入,即链数据输入(cdi),用于上游转换器的转换结果。这是链式操作。三个转换器的典型连接如图59所示。

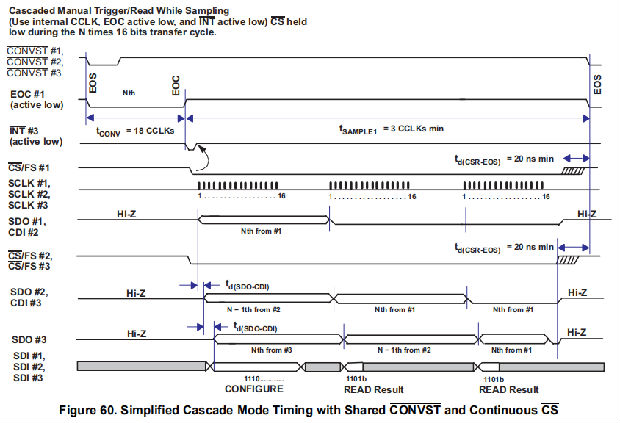

在链式模式下使用多个转换器时,第一个转换器配置为常规模式,而下游的其余转换器配置为链式模式。当转换器被配置为链式模式时,cdi输入数据直接进入输出寄存器,因此串行输入数据通过转换器时具有16 sclk(如果标签功能被禁用)或24 sclk延迟,只要cs处于活动状态。具体时间见图60。在此定时中,每个转换器中的转换是同时进行的。

采样时级联手动触发/读取

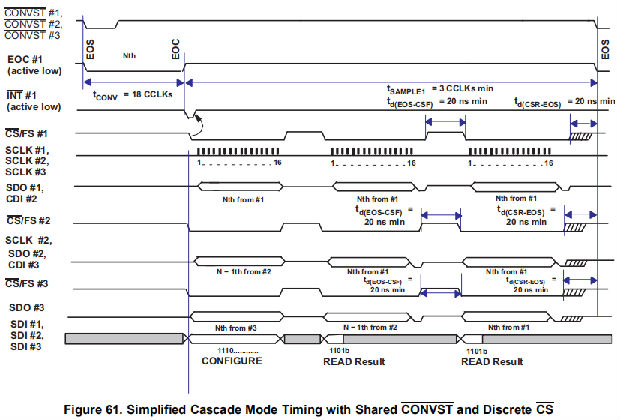

当转换器在链式模式下工作时,必须小心处理多个CS信号。在整个数据传输过程中,不同的芯片选择信号必须为低信号(在本例中,三个转换器为48位)。下降芯片选择后的第一个16位字始终是来自接收芯片选择信号的芯片的数据。

情况1:如果没有切换芯片选择(CS保持低),则接下来的16位是来自上游转换器的数据,以此类推。如图60所示。如果链中没有上游转换器,如示例中的转换器1,则来自转换器的相同数据将重复显示。

情况2:如图61所示,如果在链模式数据传输周期中切换芯片选择,则在所有三个离散16位周期中,重复读取来自转换器的相同数据。这不是一个理想的结果。

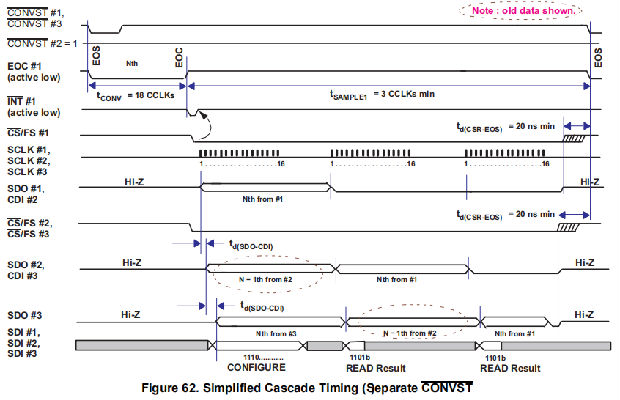

图62显示了一个稍微不同的场景,其中convst不被第二个转换器共享。转换器1和转换器3具有相同的convst信号。在这种情况下,converter 2仅向下游传递先前的转换数据。串行读取周期所需的SCLK数量取决于不同读取模式、标记位、链模式和信道选择方式(即,自动信道选择)的组合。

转换器之间的SCLK偏差和通过配置为链模式的转换器的数据路径延迟会影响SCLK的最大频率。延迟也会受到电源电压和负载的影响。当设备配置为链模式时,可能需要降低SCLK的速度。

重置

该转换器有两种复位机制,一种是上电复位(por),另一种是使用cfr d0的软件复位。这两种机制在内部并不成立。当发出复位(软件或POR)时,所有寄存器数据被设置为默认值(所有1s),SDO输出(在复位后的周期内)被设置为所有1s。状态机被重置为通电状态。

图64。复位状态下的数字输出

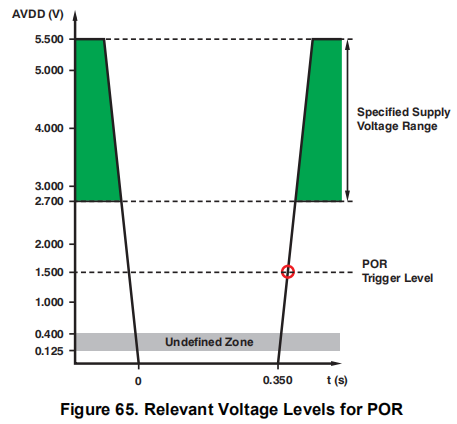

当设备通电时,当avdd达到1.5v时,por将设备设置为默认模式。当设备断电时,por电路要求avdd保持在125mv以下至少350ms,以确保内部电容器的正确放电,并在再次通电时纠正adc的行为。如果AVDD降至400毫伏以下,但仍高于125毫伏,则内部Por电容器不会完全放电,设备需要软件重置,以便在AVDD恢复后正确执行(这种情况如图65中未定义的区域所示)。

零件变更通知20071101001

ADS8329和ADS8330设备根据德州仪器零件变更通知(PCN)编号20071101001进行了硅变更。有关此部件更改的详细信息,可以从德州仪器的产品信息中心获得,也可以联系您当地的销售/分销办事处。本PCN涵盖日期代码为82xx及以上的设备。