4096点击型号即可查看芯片规格书

W25Q128FV(128M位)串行闪存为空间、管脚和电源有限的系统提供存储解决方案。25Q系列的灵活性和性能远远超过普通的串行闪存设备。它们非常适合对ram进行代码跟踪,直接从dual/quad spi(xip)执行代码,并存储语音、文本和数据。该设备在一个2.7V至3.6V的电源上工作,电流消耗低至4MA激活,1微A断电。所有设备都以节省空间的软件包提供。

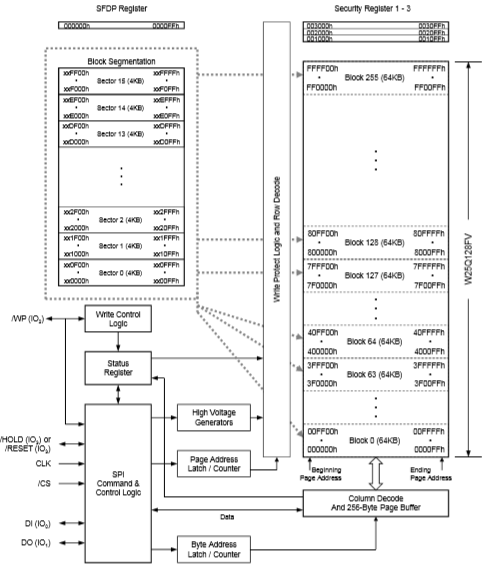

W25Q128FV阵列被组织成65536个可编程页面,每个页面256字节。一次可编程多达256字节。页面可以在16组(4KB扇区擦除)、128组(32 KB块擦除)、256组(64KB块擦除)或整个芯片(芯片擦除)中擦除。w25q128fv分别具有4096个可擦除扇区和256个可擦除块。小的4KB扇区允许在需要数据和参数存储的应用程序中具有更大的灵活性。

W25Q128FV支持标准串行外围接口(SPI)、双/四I/O SPI以及2块指令周期四外围接口(QPI):串行时钟、芯片选择、串行数据I/O0(DI)、I/O1(DO)、I/O2(/WP)和I/O3(/HOLD)。支持高达104MHz的SPI时钟频率,允许在使用快速读取的双/四I/O和QPI指令时,双I/O的等效时钟频率为208MHz(104MHz x 2),四I/O的等效时钟频率为416MHz(104MHz x 4)。这些传输速率可以优于标准异步8位和16位并行闪存。连续读取模式允许高效的内存访问,读取24位地址的指令开销只有8个时钟,允许真正的xip(就地执行)操作。

一个保持引脚,写保护引脚和可编程写保护,顶部或底部阵列控制,提供进一步的控制灵活性。此外,该设备支持jedec标准制造商、设备id和sfdp寄存器、64位唯一序列号和三个256字节安全寄存器。

特征

新的spiflash存储器系列

–W25Q128FV:128M位/16M字节

–标准spi:clk,/cs,di,do,/wp,/hold

–双SPI:CLK,/CS,IO0,IO1,/WP,/HOLD

–四SPI:CLK,/CS,IO0,IO1,IO2,IO3

–qpi:clk,/cs,io0,io1,io2,io3

–软件和硬件重置

最高性能串行闪存–104MHz单、双/四SPI时钟

–208/416MHz等效双/四SPI

–50MB/s连续数据传输速率

–超过100000次擦除/程序周期

–超过20年的数据保留

高效的“连续读取”和QPI模式–连续读取,8/16/32/64字节换行

–只需8个时钟即可寻址内存

–四外设接口(QPI)减少指令开销

–允许真正的xip(就地执行)操作

–优于x16并行闪存

低功率、宽温度范围

–单个2.7至3.6V电源

–4MA有功电流,<1微安断电(典型)

-40°C至+85°C工作范围

具有4KB扇区的灵活架构-统一扇区/块擦除(4K/32K/64K字节)-程序1至256字节/可编程页面

–擦除/程序挂起和恢复

高级安全功能–软件和硬件写保护

–电源锁定和OTP保护

–顶部/底部,补充阵列保护

–单个块/扇区阵列保护

–每个设备的64位唯一ID

–可发现参数(SFDP)寄存器

–带OTP锁的3x256字节安全寄存器

–易失性和非易失性状态寄存器位

空间有效包装-8引脚SOIC/VSOP 208密耳

-8引脚PDIP 300密耳

–8垫wson 6x5 mm/8x6 mm

- 16引脚SOIC 300密耳(附加/复位引脚)

–24球TFBGA 8x6毫米

–联系Winbond获取KGD和其他选项

封装类型和引脚配置

引脚配置SOIC/VSOP 208密耳

管脚说明

芯片选择(/cs)

spi chip select(/cs)管脚启用和禁用设备操作。当/cs为高时,设备被取消选择,串行数据输出(do或io0、io1、io2、io3)引脚处于高阻抗。当取消选择时,除非正在进行内部擦除、程序或写入状态寄存器循环,否则设备功耗将处于待机状态。当CS被引入到低电平时,设备将被选择,功耗将增加到有效电平,并且指令可以被写入和从设备读取数据。通电后,/cs必须从高转换到低,才能接受新指令。/cs输入必须跟踪通电和断电时的VCC电源电平(参见“写保护”和图58)。如果需要,可以使用/CS引脚上的上拉电阻来实现这一点。

串行数据输入、输出和IOS(DI、DO和IO0、IO1、IO2、IO3)

W25Q128FV支持标准SPI、双SPI和四SPI操作。标准SPI指令使用单向DI(输入)管脚将指令、地址或数据串行写入串行时钟(CLK)输入管脚上升沿上的设备。标准spi还使用单向do(输出)从clk下降沿上的设备读取数据或状态。

双SPI和四SPI指令使用双向IO管脚将指令、地址或数据串行写入CLK上升沿上的设备,并从CLK下降沿上的设备读取数据或状态。quad spi指令要求设置状态寄存器2中的非易失性quad enable位(qe)。当qe=1时,/wp pin变为io2,/hold pin变为io3。

写保护(/wp)

写保护(/WP)引脚可以用来防止状态寄存器被写入。与状态寄存器的块保护(CMP、SEC、TB、BP2、BP1和BP0)和状态寄存器保护(SRP)位一起使用,小到4KB扇区或整个存储器阵列的部分可以是硬件保护的。/WP引脚处于低激活状态。当状态寄存器-2的qe位被设置为四输入/输出时,/wp pin功能不可用,因为该pin用于i o 2。四路I/O操作的引脚配置见图1A-C。

保持(/保持)

/hold pin允许在设备处于活动状态时暂停设备。当/hold变低时,当/cs变低时,do管脚将处于高阻抗,di和clk管脚上的信号将被忽略(不要在意)。当保持高,设备操作可以恢复。当多个设备共享相同的SPI信号时,/HOLD函数可能是有用的。/HOLD引脚处于低激活状态。当状态寄存器-2的qe位设置为四输入/输出时,由于该引脚用于io3,因此/hold pin功能不可用。四路I/O操作的引脚配置见图1A-C。

串行时钟(CLK)

SPI串行时钟输入(CLK)引脚提供串行输入和输出操作的定时。(见SPI)

4.6复位(/复位)

/reset pin允许控制器重置设备。对于8引脚封装,当QE=0时,IO3引脚可以配置为A/STOP引脚或A/RESET引脚,取决于状态寄存器设置。当qe=1时,/hold或/reset功能不适用于8针配置。在16针SOIC封装上,提供了一个专用/复位管脚,它独立于QE位设置。

方块图

功能描述

W25Q128FV串行闪存操作图

标准SPI说明

W25Q128FV通过一个SPI兼容总线访问,该总线由四个信号组成:串行时钟(CLK)、芯片选择(/CS)、串行数据输入(DI)和串行数据输出(DO)。标准spi指令使用di输入pin将指令、地址或数据串行写入clk上升沿上的设备。do输出引脚用于从clk下降沿上的设备读取数据或状态。

支持SPI总线操作模式0(0,0)和3(1,1)。模式0和模式3之间的主要区别在于SPI总线主设备处于待机状态且数据未传输到串行闪存时CLK信号的正常状态。对于模式0,在/cs的下降和上升边缘,clk信号通常较低。对于模式3,CLK信号通常在/cs的下降和上升边缘高。

双SPI指令

W25Q128FV在使用“快速读取双输出(3BH)”和“快速读取双I/O(BBH)”等指令时支持双SPI操作。这些指令允许以普通串行闪存设备的2到3倍速率将数据传输到设备或从设备传输数据。双spi读取指令非常适合在通电时快速将代码下载到ram(代码阴影)或直接从spi总线(xip)执行非速度关键代码。使用双spi指令时,di和do管脚变为双向i/o管脚:io0和io1。

四SPI指令

W25Q128FV在使用诸如“快速读取四路输出(6BH)”、“快速读取四路I/O(EBH)”、“字读取四路I/O(E7H)”和“八进制字读取四路I/O(E3H)”等指令时支持四路SPI操作。这些指令允许数据以普通串行闪存4到6倍的速率传输到设备或从设备传输数据。四读指令在连续和随机访问传输速率方面提供了显著的改进,允许从spi总线(xip)直接对ram或执行进行快速代码跟踪。使用quad spi指令时,di和do管脚变为双向io0和io1,/wp和/hold管脚分别变为io2和io3。quad spi指令要求设置状态寄存器2中的非易失性quad enable位(qe)。

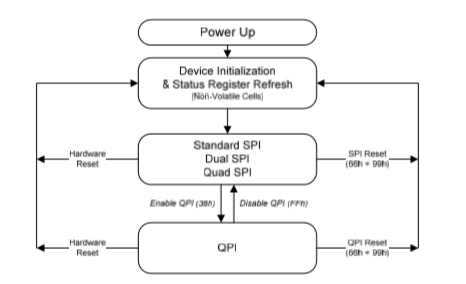

QPI说明

W25Q128FV仅在使用“enter qpi(38h)”指令将设备从标准/双/四SPI模式切换到QPI模式时支持四外围接口(QPI)操作。典型的spi协议要求在8个串行时钟中,字节长的指令码只能通过di-pin转移到设备中。qpi模式利用所有四个io管脚来输入指令码,因此只需要两个串行时钟。这可以显著减少SPI指令开销,并在XIP环境中提高系统性能。标准/双/四SPI模式和QPI模式是唯一的。在任何给定的时间只有一个模式可以是活动的。“enter qpi(38h)”和“exit qpi(ffh)”指令用于在这两种模式之间切换。通电后或使用“重置(99h)”指令进行软件重置后,设备的默认状态为标准/双/四SPI模式。要启用qpi模式,需要设置状态寄存器2中的非易失性四位启用位(qe)。使用qpi指令时,di和do管脚变为双向io0和io1,/wp和/hold管脚分别变为io2和io3。设备运行模式见图3。

保持功能

对于标准spi和双spi操作,/hold信号允许w25q128fv操作在被激活时暂停(当/cs为低时)。在spi数据和时钟信号与其他设备共享的情况下,/保持功能可能有用。例如,考虑当优先级中断需要使用SPI总线时,页缓冲区是否仅被部分写入。在这种情况下,/HOLD函数可以保存指令的状态和缓冲区中的数据,因此一旦总线再次可用,编程就可以恢复到它停止的地方。/HOLD功能仅适用于标准SPI和双SPI操作,而不适用于四SPI或QPI。状态寄存器2中的四位使能位qe用于确定管脚是否用作/保持管脚或数据输入/输出管脚。当qe=0(出厂默认值)时,管脚为/hold;当qe=1时,管脚变为I/O管脚,/hold功能不再可用。

要启动A/HOLD条件,必须选择/CS低的设备。如果CLK信号已经很低,A/HOLD状态将在/HOLD信号的下降沿激活。如果CLK还不低,则/保持条件将在CLK的下一个下降沿后激活。如果CLK信号已经很低,/HOLD条件将在/HOLD信号的上升沿终止。如果CLK不低,则/保持条件将在CLK的下一个下降沿之后终止。在A/HOLD状态下,串行数据输出(do)为高阻抗,忽略串行数据输入(di)和串行时钟(clk)。芯片选择(/cs)信号应在/hold操作的整个持续时间内保持激活(低),以避免重置设备的内部逻辑状态。

软件复位和硬件/复位引脚

W25Q128FV可以通过软件复位序列重置到初始通电状态,无论是SPI模式还是QPI模式。此序列必须包含两个连续的命令:启用重置(66h)和重置(99h)。如果命令序列被成功接受,设备将需要大约30us(trst)来重置。重置期间不接受任何命令。

对于WSON-8和TFBGA封装类型,W25Q128FV也可以被配置为利用硬件/复位引脚。状态寄存器3中的保持/rst位是/hold pin功能或复位pin功能的配置位。当HOLD/RST=0(出厂默认值)时,管脚充当上述的A/HOLD管脚;当HOLD/RST=1时,管脚充当A/RESET管脚。将/reset pin低开至少1us(treset*)将设备重置为初始开机状态。任何正在进行的程序/擦除操作都将中断,并且可能发生数据损坏。当/reset处于低位时,设备将不接受任何命令输入。

如果qe位设置为1,则/hold或/reset功能将被禁用,该引脚将成为四个数据I/O引脚之一。

对于SOIC-16封装,W25Q128FV除了图1b所示的/保持(IO3)引脚外,还提供一个专用/复位引脚。将/复位引脚低驱动至少1us(treset*)将设备复位至初始通电状态。状态寄存器中的HOLD/RST位或QE位不会影响此专用/复位引脚的功能。

硬件/复位引脚在所有输入信号中具有最高优先级。无论其他SPI信号(/cs、clk、ios、/wp和/或/hold)的状态如何,至少1us(treset*)的低驱动/复位将中断任何正在进行的外部/内部操作。

注:虽然更快/重置脉冲(短至几百纳秒)通常会重置设备,但建议至少1us以确保可靠运行。

写保护

使用非易失性存储器的应用程序必须考虑噪声和其他可能损害数据完整性的不利系统条件的可能性。为了解决这个问题,w25q128fv提供了几种保护数据不被意外写入的方法。

写保护特性

当VCC低于阈值时,设备复位

通电后时间延迟写入禁用

写入启用/禁用指令,擦除或编程后自动写入禁用

使用状态寄存器的软件和硬件(/wp pin)写保护

额外的单个块/扇区锁,用于阵列保护

使用断电指令写入保护

状态寄存器的锁定写保护,直到下一次通电

使用状态寄存器的阵列和安全寄存器的一次性程序(OTP)写保护*

*注:此功能在特殊订购时提供。详情请联系Winbond。

通电或断电时,当VCC低于VWI的阈值时,W25Q128FV将保持复位状态(见通电定时和电压水平和图43)。重置时,将禁用所有操作,并且不识别任何指令。在通电期间以及在vcc电压超过vwi之后,由于tpuw的时间延迟,所有与程序和擦除相关的指令进一步被禁用。这包括写入启用、页面程序、扇区擦除、块擦除、芯片擦除和写入状态寄存器指令。请注意,芯片选择引脚(/cs)必须在通电时跟踪VCC电源电平,直到达到VCC最小电平和TVSL延时,并且还必须在断电时跟踪VCC电源电平,以防止出现相反的命令序列。如果需要,可以使用一个上拉电阻/CS来实现这一点。

通电后,设备自动处于写禁用状态,状态寄存器写启用闩锁(WEL)设置为0。在接受页程序、扇区擦除、块擦除、芯片擦除或写入状态寄存器指令之前,必须发出允许写入指令。完成程序、擦除或写入指令后,写入启用闩锁(WEL)将自动清除为可写状态0。

使用写状态寄存器指令和设置状态寄存器保护(srp0,srp1)和块保护(cmp,sec,tb,bp[2:0])位有助于软件控制的写保护。这些设置允许将部分或整个内存阵列配置为只读。与写保护(/WP)引脚一起使用,可以在硬件控制下启用或禁用状态寄存器的更改。有关更多信息,请参阅状态寄存器部分。此外,掉电指令提供了额外的写保护级别,因为除了释放掉电指令之外,所有指令都被忽略。

w25q128fv还提供了另一种使用单独块锁的写保护方法。每个64kb块(除了顶部和底部块,总共510个块)和顶部/底部块内的每个4kb扇区(总共32个扇区)都配备有单独的块锁位。当锁位为0时,相应的扇区或块可以被擦除或编程;当锁位被设置为1时,将忽略对相应扇区或块发出的擦除或程序命令。当设备通电时,所有单独的块锁定位将为1,因此整个内存阵列受到保护,不受擦除/编程的影响。必须发出“单个块解锁(39h)”指令来解锁任何特定扇区或块。

状态寄存器3中的wps位用于决定应使用哪种写保护方案。当wps=0(出厂默认值)时,设备将仅使用cmp、sec、tb、bp[2:0]位来保护阵列的特定区域;当wps=1时,设备将使用各个块锁进行写保护。

状态和配置寄存器

W25Q128FV提供三个状态和配置寄存器。读取状态寄存器1/ 2/3指令可用于提供关于闪存阵列的可用性的状态、该设备是否已写入或禁用、写保护状态、Quad SPI设置、安全寄存器锁定状态、擦除/程序挂起状态、输出驱动器强度、上电和当前地址模式。写作

状态寄存器指令可用于配置设备写保护功能、Quad SPI设置、安全寄存器OTP锁、保持/复位功能、输出驱动器强度和上电地址模式。对状态寄存器的写访问由非易失性状态寄存器保护位(srp0,srp1)的状态、写启用指令和标准/双spi操作期间的/wp pin控制。

擦除/正在写入(忙)–仅状态忙是状态寄存器(s0)中的只读位,当设备执行页程序、四页程序、扇区擦除、块擦除、芯片擦除、写入状态寄存器或擦除/程序安全寄存器指令时,该位被设置为1状态。在此期间,设备将忽略除读取状态寄存器和擦除/程序挂起指令以外的其他指令(参见交流特性中的tw、tpp、tse、tbe和tce)。当程序、擦除或写入状态/安全寄存器指令完成时,忙碌位将被清除到0状态,表示设备已准备好接受进一步指令。写使能锁存(WEL)-仅状态写使能锁存(WEL)是状态寄存器(S1)中的只读位,在执行写使能指令后设置为1。当设备写禁用时,WEL状态位清除为0。在通电时或在以下任何指令之后出现写禁用状态:写禁用、页程序、四页程序、扇区擦除、块擦除、芯片擦除、写状态寄存器、擦除安全寄存器和程序安全寄存器。块保护位(bp2、bp1、bp0)-易失性/非易失性可写块保护位(bp2、bp1、bp0)是提供写保护控制和状态的状态寄存器(s4、s3和s2)中的非易失性读/写位。可以使用写状态寄存器指令来设置块保护位(参见AC特性中的TW)。所有,没有或部分存储器阵列可以被保护免于程序和擦除指令(见状态寄存器存储器保护表)。块保护位的出厂默认设置为0,没有受保护的数组。

上/下块保护(tb)易失性/非易失性可写非易失性上/下位(tb)控制块保护位(bp2、bp1、bp0)是从阵列的顶部(tb=0)还是底部(tb=1)进行保护,如状态寄存器内存保护表所示。出厂默认设置为tb=0。根据SRP0、SRP1和WEL位的状态,可以将TB位设置为写入状态寄存器指令。扇区/块保护位(秒)易失性/非易失性可写非易失性扇区/块保护位(秒)控制块保护位(bp2,bp1,bp0)保护数组顶部(tb=0)或底部(tb=1)的4kb扇区(sec=1)或64kb块(sec=0),如状态寄存器内存保护表所示。默认设置为sec=0。补码保护(CMP)是状态寄存器(S14)中的非易失性读/写位。它与sec、tb、bp2、bp1和bp0位结合使用,为阵列保护提供了更大的灵活性。一旦CMP设置为1,以前由SEC、TB、BP2、BP1和BP0设置的阵列保护将被反转。例如,当CMP=0时,顶部64KB块可以被保护,而阵列的其余部分不被保护;当CMP=1时,顶部64KB块将变得不受保护,而阵列的其余部分变成只读。有关详细信息,请参阅状态寄存器内存保护表。默认设置为cmp=0。7.1.7状态寄存器保护(SRP1,SRP0)是状态寄存器(S8和SRP0)中的非易失性读/写位。srp位控制写保护的方法:软件保护、硬件保护、电源锁定或一次性可编程(otp)保护。

擦除/程序挂起状态(SUS)–仅状态挂起状态位是状态寄存器(S15)中的只读位,在执行擦除/程序挂起(75h)指令后设置为1。SUS状态位通过擦除/程序恢复(7AH)指令以及断电、通电循环清除为0。

安全寄存器锁定位(LB3、LB2、LB1)-可写的易失性/非易失性OTP安全寄存器锁定位(LB3、LB2、LB1)是状态寄存器(S13、S12、S11)中的非易失性一次性程序(OTP)位,为安全寄存器提供写保护控制和状态。lb3-1的默认状态为0,安全寄存器未锁定。LB3-1可以使用写状态寄存器指令单独设置为1。LB3-1是一次性可编程(OTP),一旦设置为1,相应的256字节安全寄存器将永久变为只读。7.1.10 quad enable(qe)-易失性/非易失性可写quad enable(qe)位是状态寄存器(s9)中允许quad spi和qpi操作的非易失性读/写位。当qe位设置为0状态(出厂默认值)时,/wp pin和/hold被启用。当qe位设置为1时,四个io2和io3引脚被启用,并且/wp和/hold功能被禁用。

在发出“enter qpi(38h)”将设备从标准/dual/quad spi切换到qpi之前,qe位必须设置为1,否则该命令将被忽略。当设备处于qpi模式时,qe位将保持为1。QPI模式下的“写入状态寄存器”命令无法将QE位从“1”更改为“0”。

警告:如果/wp或/hold引脚在标准spi或双spi操作期间直接连接到电源或接地,则qe位不应设置为1。

写保护选择(WPS)-易失/非易失可写WPS位用于选择应使用哪种写保护方案。当wps=0时,设备将使用cmp、sec、tb、bp[2:0]位的组合来保护内存阵列的特定区域。当wps=1时,设备将使用单个块锁来保护任何单个扇区或块。所有单个块锁定位的默认值在设备通电或重置后为1。

输出驱动程序强度(DRv1,DRv0)-易失性/非易失性可写DRv1和DRv0位用于确定读取操作的输出驱动程序强度。

/保持或/复位引脚功能(保持/重新设置)–易失性/非易失性可写保持/重新设置位用于确定是否应在8针软件包的硬件引脚上实现/保持或/重新设置功能。当HOLD/RST=0(出厂默认值)时,管脚充当/HOLD;当HOLD/RST=1时,管脚充当/RESET。但是,/hold或/reset函数仅在qe=0时可用。如果qe设置为1,则/hold和/reset功能将被禁用,该管脚将充当专用数据I/O管脚。

保留位-非功能-有一些保留状态寄存器位可以读出为“0”或“1”。建议忽略这些位的值。在“写状态寄存器”指令中,保留位可以写成“0”,但不会有任何影响。

指令W25Q128FV的标准/双/四SPI指令集由45个基本指令组成,这些指令通过SPI总线完全控制(见指令集表1-2)。使用芯片选择的下降沿(/cs)启动指令。进入DI输入的数据的第一个字节提供指令代码。DI输入上的数据在时钟的上升沿上采样,最高有效位(msb)在前。

W25Q128FV的QPI指令集由32条基本指令组成,这些指令通过SPI总线完全控制,使用芯片选择的下降沿(/cs)启动指令。通过IO[3:0]管脚计时的数据的第一个字节提供指令代码。所有四个IO管脚上的数据都在时钟上升沿上采样,最有效位(msb)在前。所有qpi指令、地址、数据和伪字节都使用所有四个io管脚,以每两个串行时钟(clk)传输每个字节的数据。

指令的长度从一个字节到几个字节不等,后面可能是地址字节、数据字节、伪字节(不必在意),在某些情况下是一个组合。使用EDGE/CS的上升沿完成说明。图5到图57中包括了每条指令的时钟相关时序图。所有读指令可以在任何时钟位之后完成。但是,所有写入、编程或擦除的指令都必须在字节边界上完成(在一个完整的8位时钟后/cs驱动高),否则指令将被忽略。此功能进一步保护设备免受意外写入。此外,当存储器被编程或擦除时,或当状态寄存器被写入时,除读取状态寄存器外的所有指令都将被忽略,直到程序或擦除周期完成。