AD7520点击型号即可查看芯片规格书

AD7520和AD7521是单片的,高精度,低成本的10位和12位分辨率,乘法数模转换器(DAC)。Intersil在CMOS工艺上的薄膜在TTL/CMOS兼容操作下可提供高达10位的精度。数字输入通过二极管对地和正电源完全防止静电放电。

典型应用包括数字/模拟接口、乘法和除法、可编程电源、crt字符生成、数字控制增益电路、积分器和衰减器等。

绝对最大额定值

电源电压(V+至接地)………………+17V;电压…………………………………±25V

数字输入电压范围……………………V+到GND;对地输出电压符合性…………-100mV至V+

操作条件

温度范围

JN,LN版本……………………………0C至70Coo

热信息

热阻(典型,注1)θja(c/w)θjc(c/w)oo;16 LD PDIP包90不适用;18 LD PDIP包80不适用

最高连接温度(塑料包装)……….150℃;最大储存温度范围…………………-65C至150C;最高引线温度(焊接10s)…………300℃

注意:超过“绝对最大额定值”中列出的应力可能会对设备造成永久性损坏。这只是一个应力额定值,在这些或任何其他条件下,设备的操作高于本规范操作章节中所示的条件并不意味着。

数字控制输入受到齐纳保护,但是,在高能静电场下,未连接的单元可能会发生永久性损坏。在导电泡沫中始终保持未使用的单位。

不要施加高于V的电压DD或小于任何端子上的接地电位(V除外)。

1、θja是在自由空气中,用安装在低效热导率测试板上的元件测量的。

管脚说明

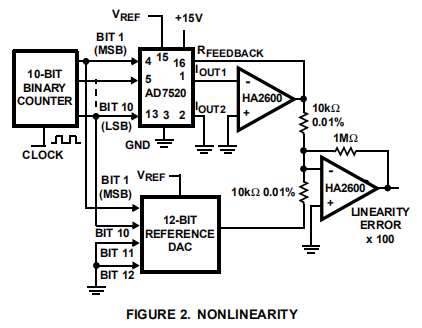

非线性:DAC传递函数偏离传递函数的实际绘图中的“最佳直线”所造成的误差。通常表示为满标度范围的百分比或1 lsb的(子)倍数。分辨率:它解决了D/A转换器能产生的最小的不同模拟输出变化。它通常表示为转换器位数。具有n位分辨率的转换器可以解决满标度范围的2的输出变化,例如,单极性转换的2 vref。分辨率绝不意味着线性。-N-N

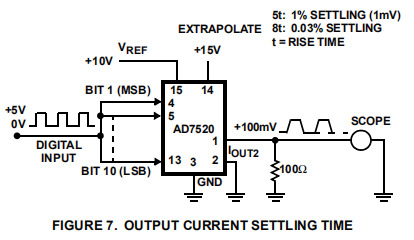

沉降时间:对于给定的数字输入变化,即所有数字输入从低到高和从高到低,dac的输出在其最终值(例如/2lsb)周围稳定到指定误差带所需的时间。

增益误差:满标度范围内的实际和理想模拟输出值之间的差异,即高状态下的所有数字输入。它表示为满标度范围的百分比或1 lsb的(子)倍数。

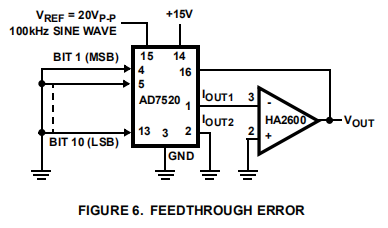

馈通错误:所有数字输入低时,VREF与IOUT1之间的电容耦合引起的误差。

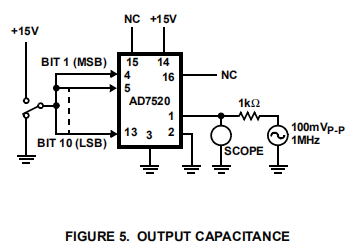

输出电容:IOUT1和IOUT2端子对地电容。

输出漏电流:当所有数字输入低时出现在IOUT1端子上的电流,或当所有数字输入高时出现在IOUT2端子上的电流。

详细说明

AD7520和AD7521是单片乘法D/A转换器。高稳定的薄膜r-2r电阻梯形网络和nmos-spdt开关构成了转换器电路的基础,cmos电平移相器允许低功耗ttl/cmos兼容工作。外部电压或电流基准和运算放大器是大多数电压输出应用所需的全部。

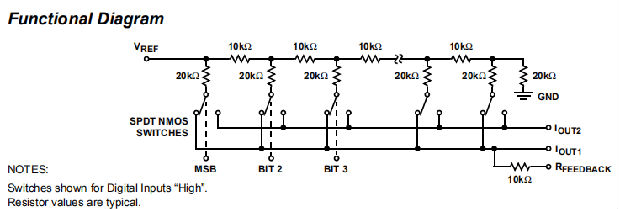

功能图中给出了dac的简化等效电路。nmos spdt开关控制iout1和iout2总线之间的梯段电流,该电流必须保持在地电位。此配置保持每个梯段中的恒定电流独立于输入代码。

通过在主要位和输出端之间使用单独的金属互连,转换器误差进一步减小。使用高阈值开关可将偏移(泄漏)误差降低到可忽略的水平。

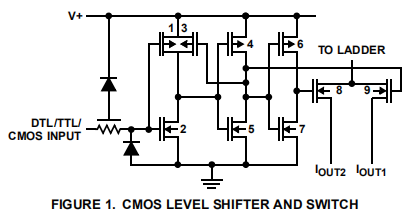

电平移位器电路由三个从第二个输出到第一个输出的正反馈逆变器组成,见图1。这种结构使得ttl/cmos兼容在整个军用温度范围内工作。在电平移位器驱动的梯形spdt开关中,每一个开关都按与各自梯形支路电流成比例的导通电阻进行二次加权。这确保了每个开关上的恒定电压降,为2R梯形电阻和高精度支路电流创建等电位终端。

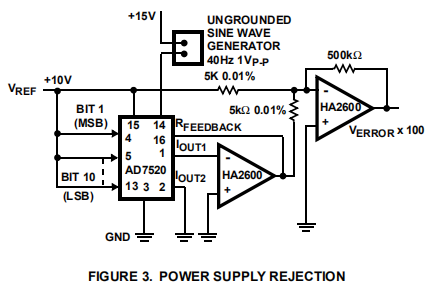

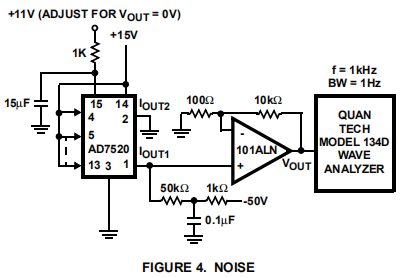

测试电路以下测试电路适用于AD7520。AD7521也采用了类似的电路。

测试电路以下测试电路适用于AD7520。AD7521也采用了类似的电路。

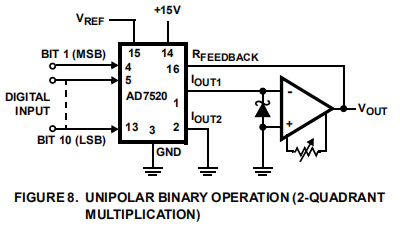

单极二进制运算应用

用于在单极模式下操作AD7520的电路配置如图8所示。类似的电路可用于AD7521。在正负VREF值的情况下,电路能够进行2象限乘法。

零偏移调整

1、将所有数字输入连接到GND。

2、将输出运算放大器的偏移零点调整微调器调整到0V。

增益调整

1、将所有数字输入连接到V+。

2、监控VOUT的A-VREF(1-2)读数。(AD7520的n=8,AD7521的n=10)。-N

3、要降低电压输出,请在参考电压和VREF端子之间连接一个串联电阻(0至250Ω)。

4、要增加输出电压,请在IOUT1放大器反馈回路中连接一个串联电阻(0至250Ω)。

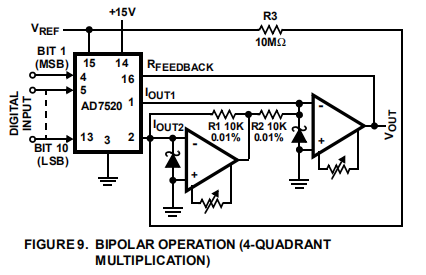

双极(偏置二进制)操作

图9给出了在双极模式下操作AD7520的电路配置。类似的电路可用于AD7521。利用偏置二进制数字输入码和正负参考电压值,可以实现四象限乘法。双极模式的“数字输入代码/模拟输出值”。

任何数字输入处的“逻辑1”输入迫使相应的梯形开关将位电流转向IOUT1总线。“逻辑0”输入将位电流强制到IOUT2总线。对于任何代码,iout1和iout2总线电流都是相互补充的。iout2处的电流放大器改变iout2电流的极性,iout1处的跨导放大器将两个电流相加。此配置使输出范围加倍。零偏移二进制代码(msb=“logic 1”,所有其他位均为“logic 0”)产生的差分电流通过使用外部电阻(10MW)从VREF到IOUT2进行校正。

增益调整

1、将所有数字输入连接到V+。

2、监控VOUT是否为-VREF(1-2伏读数。(AD7520的n=8,AD7521的n=10。)-(n-1)

3、要增加输出电压,在输出电压和反馈电压之间连接一个高达250欧的串联电阻。

4、要降低电压输出,请在参考电压和VREF端子之间连接一个高达250Ω的串联电阻。