AD7870点击型号即可查看芯片规格书

TMS32010点击型号即可查看芯片规格书

MC68008点击型号即可查看芯片规格书

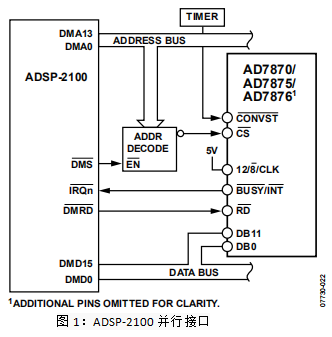

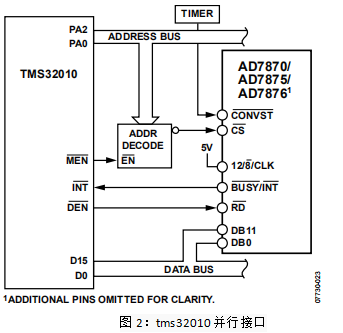

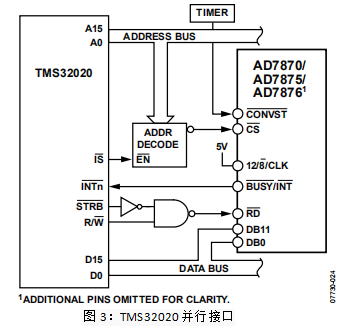

AD7870/AD7875/AD7876具有多种接口选项。它们提供两种操作模式和三种数据输出格式。快速的数据访问时间允许直接连接到包括DSP处理器在内的大多数微处理器。

并行读取接口

图1、图2和图3显示了ADSP-2100、TMS32010和TMS32020 DSP处理器的接口。ADC在模式1下运行,对所有三个接口进行并行读取。外部定时器控制与微处理器异步启动的转换。每次转换结束时adc busy/int中断微处理器。使用以下指令从adc读取转换结果:

ADSP-2100:MR0=dm(模数转换器)

tms32010:输入d,adc

tms32020:输入d,adc

MR0=ADSP-2100 MR0寄存器

D=数据存储器地址

ADC=AD7870/AD7875/AD7876地址

有些应用程序可能要求由微处理器而不是外部计时器启动转换。一种选择是对来自地址总线的convst信号进行解码,以便对adc的写入操作开始转换。如前所述,在转换结束时读取数据。注意:转换期间不得尝试读取操作。

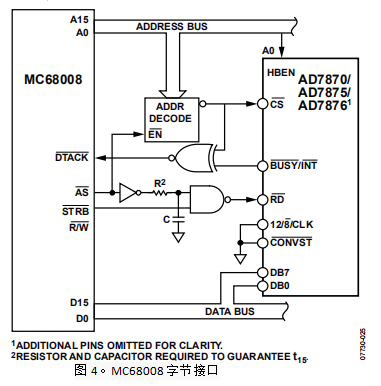

双字节读取接口

68008接口

图4显示了MC68008 Micro的8位总线接口-处理器。对于该接口,12/8/CLK输入连接到0 V,DB11/HBEN引脚由微处理器最低有效地址位驱动。转换启动控制由微处理器提供。在这个介面范例中,来自ADC位址的MOVE指令会启动转换并读取转换结果。

移动模数转换器

ADC=AD7870/AD7875/AD7876地址

d0=68008 d0寄存器

这是一个双字节的读取指令。在第一次读的时候。操作忙,结合CS,迫使微处理器等待ADC转换。转换结束时,将ADC低字节(DB7–DB0)加载到D0寄存器的D15–D8中,并将ADC高字节(DB15–DB7)加载到D0寄存器的D7–D0位中。以下到d0寄存器的旋转指令将高字节和低字节交换为正确的格式。R0L=8,D0。注意,在执行上述两字节读取指令时,等待状态只在第一次读取操作期间插入,而不是在第二次读取操作期间插入。

串行接口

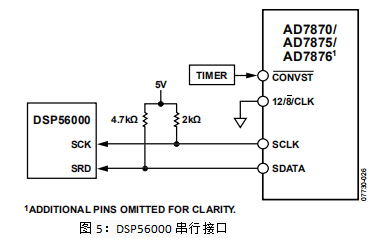

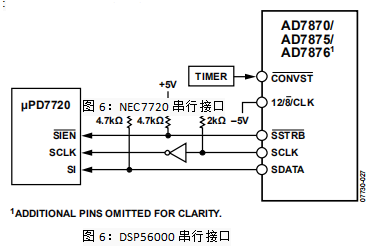

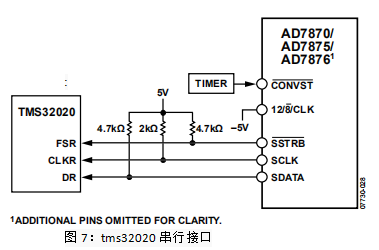

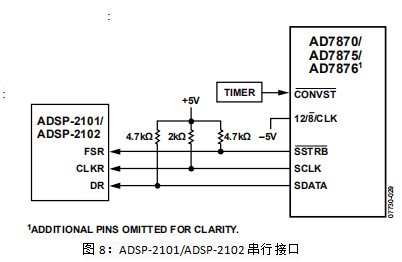

图5、图6、图7和图8显示了为串行接口配置的AD7870/AD7875/AD7876。在所有四个接口中,ADC配置为模式1操作。接口显示了一个驱动convst输入的计时器,但如果需要,可以从解码地址生成。这个SCLK、SDAT和SSTRB是开漏输出。如果需要这些来驱动超过35 pF的电容负载,建议进行缓冲。

DSP56000串行接口

图26显示了AD7870/AD7875/AD7876和DSP56000之间的串行接口。接口配置为二线制,ADC配置为非连续时钟操作(12/8/CLK=0V)。DSP56000配置为带选通时钟的正常模式异步操作。它还设置为16位字,SCK和SC1作为输入,FSL控制位设置为0。在此配置中,DSP56000假定SCK的第一个下降沿上有有效数据。由于adc在该第一边缘上提供有效的数据,因此不需要数据的选通或帧脉冲。当ADC不执行转换时,SCLK和SData被选通关闭。在转换过程中,数据在sdata上有效ADC的输出,并被记录到DSP56000的接收数据移位寄存器中。当这个寄存器接收到16位数据时,它在dsp56000上产生一个内部中断,从寄存器中读取数据。

DSP56000和AD7870/AD7875/AD7876也可以配置为连续时钟操作(12/8/CLK=-5 V)。在这种情况下,DSP56000需要一个选通脉冲来指示数据何时有效。ADC的SSTRB输出反向,并应用于DSP56000的SC1输入,以提供该选通脉冲。所有其他条件和连接与门控时钟操作相同。

NEC7720/77230串行接口

AD7870/AD7875/AD7876和NEC7720之间的串行接口如图27所示。在所示的接口中,adc被配置为连续时钟操作。这可以通过简单地将ADC的12/8/CLK输入连接到0V而将所有其他连接保持不变而改变为非连续时钟。NEC7720期望SCK输入上升沿上有有效数据,因此ADC的SCLK输出上需要一个逆变器。NEC7720配置为16位数据字。一旦nec7720的si寄存器接收到16位数据,就产生内部中断来读取si寄存器的内容。NEC77230接口与刚刚为NEC7720概述的接口类似。然而,nec77230的时钟输入是siclk。此外,在adc sclk输出和该siclk输入之间不需要反相器,因为nec77230假定siclk下降沿上的数据有效。

tms32020串行接口

图7显示了AD7870之间的串行接口/AD7875/AD7876和tms32020。AD7870/AD7875/AD7876配置为连续时钟操作。注意,如果ADC配置为非连续时钟,则ADC将无法正确地与tms32020接口。在转换过程中,数据被计时到tms32020的数据接收寄存器(drr)中。与前面的接口一样,当tms32020接收到16位字时,它会生成一个内部中断来从drr读取数据。

ADSP-2101/ADSP-2102串行接口

独立操作

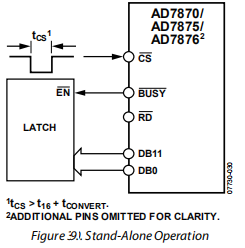

AD7870/AD7875/AD7876可在其模式2并行接口模式下用于独立操作。在这种情况下,转换是通过一个脉冲启动到ADC CS输入。此脉冲必须长于ADC的转换时间。这个忙输出用于驱动rd输入。数据从adc db0–db11输出锁存到busy上升沿的外部锁存。

独立操作

AD7870/AD7875/AD7876可用于其模式2,独立操作的并行接口模式。在这种情况下,转换是通过一个脉冲启动到ADC CS输入。这个脉冲必须长于ADC的转换时间。这个忙输出用于驱动rd输入。数据被锁定ADC DB0–DB11在上升时输出到外部锁存器忙碌的边缘。

应用程序信息

良好的印刷电路板(pcb)布局对于实现高速模拟数字性能与整个电路设计本身同等重要。设计者必须注意adc本身和前面模拟电路中的噪声。不建议使用开关模式电源,因为开关尖峰通过比较器引起噪声代码转换。其他引起关注的原因是接地回路和微处理器的数字反馈。这些都是影响任何adc的因素,适当的pcb布局将这些影响降到最低是获得最佳性能的关键。

布局提示

确保印刷电路板的布局尽可能将数字和模拟信号线分开。注意不要在模拟信号轨道旁边运行任何数字轨道。用agnd保护(屏幕)模拟输入。

建立一个单点模拟接地(星形接地),在AGND引脚处与逻辑系统接地分离,或尽可能靠近ADC。将所有其他接地和AD7870/AD7875/AD7876 DGND连接到此单一模拟接地点。不要将任何其他数字接地连接到此模拟接地点。

低阻抗模拟和数字电源公共回路对ADC的低噪声运行至关重要,因此应使这些磁道的箔宽度尽可能宽。接地平面的使用使阻抗路径最小化,同时也保护模拟电路不受数字噪声的影响。电路布局具有模拟和数字接地平面,它们保持分离,仅在AD7870/AD7875/AD7876 AGND引脚处连接在一起。

噪声

尽可能短地保持输入信号线到V和信号返回线从Agnd,以尽量减少输入噪声耦合。在不可能做到这一点的应用中,在源和adc之间使用屏蔽电缆。尽可能降低接地电路阻抗,因为信号源和ADC之间的接地电位差显示为与输入信号串联的错误电压。在外形尺寸

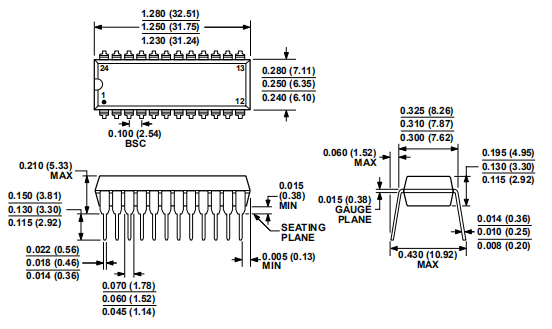

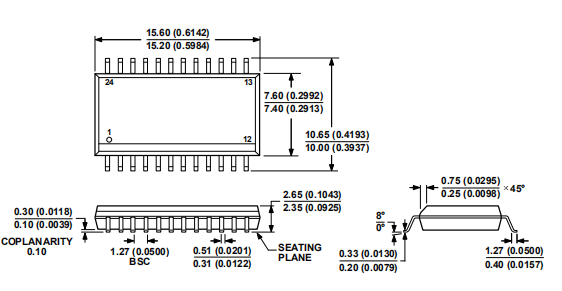

控制尺寸以英寸为单位;毫米尺寸(圆括号内)为四舍五入英寸当量,角引线可以配置为整体引线或半引线。;仅供参考,不适用于设计。

(在括号中)是四舍五入的英寸当量;仅供参考,不适用于设计。

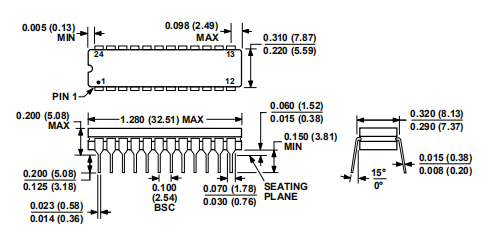

控制尺寸以英寸为单位;毫米尺寸;(在括号中)是四舍五入的英寸当量;仅供参考,不适用于设计。

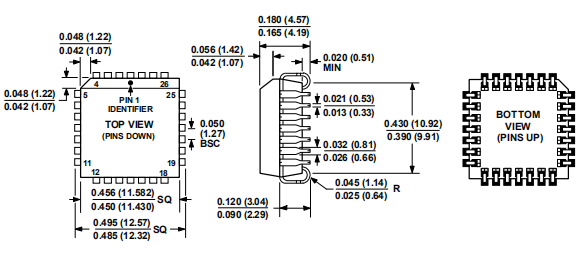

符合JEDEC标准MS-013-AD控制尺寸单位为毫米;英寸尺寸;(在括号中)是四舍五入的毫米当量;仅供参考,不适用于设计。