1149点击型号即可查看芯片规格书

8226点击型号即可查看芯片规格书

512点击型号即可查看芯片规格书

xC17v00点击型号即可查看芯片规格书

特征

系统内可编程3.3V proms

锡林克斯FPGA配置

20000个程序/擦除周期的耐久性整个工业电压和温度范围内的程序/擦除(–40°C至+85°C)

IEEE Std 1149.1边界扫描(JTAG)支持

JTAG命令启动标准FPGA配置

与FPGA的简单接口

可级联存储较长或多个位流

低功耗高级CMOS闪存处理8226;双配置模式

串行慢速/快速配置(最高33兆赫)

并行(33兆赫时高达264 MB/s)

5 V容限I/O引脚接受5 V、3.3 V和2.5 V信号

3.3V或2.5V输出能力

使用Xilinx ISE基础基金软件包进行设计支持

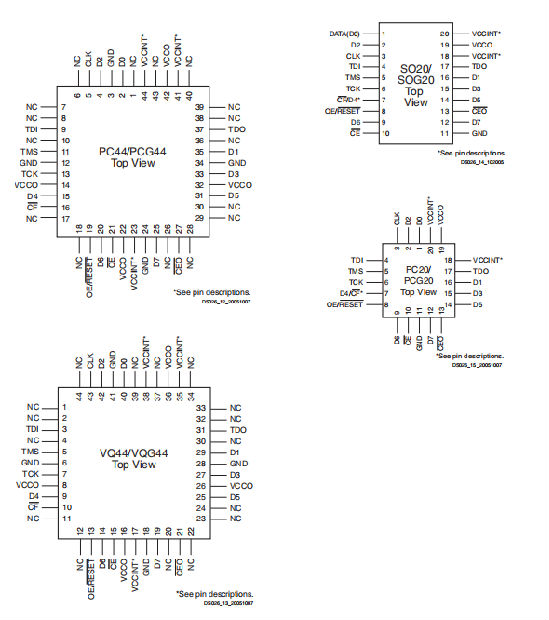

提供PC20、SO20、PC44和VQ44包

无铅(无铅)包装

描述

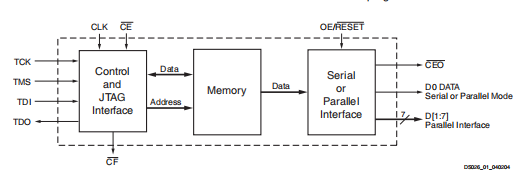

Xilinx介绍了XC18V00系列系统内可编程配置proms(图1)。这个3.3V系列的设备包括一个4兆位、一个2兆位、一个1兆位和一个512千位的可编程只读存储器-

用于重新编程和存储XilinxFPGA配置位流的低成本方法。

当FPGA处于主串行模式时,它产生一个驱动可编程只读存储器的配置时钟。很短的通道

CE和OE启用后的一段时间内,与FPGA DIN相连的可编程只读存储器数据(D0)插脚上的数据可用。

引脚。新数据在每次访问后很短的访问时间内可用

上升时钟边缘。FPGA生成适当数量的时钟脉冲来完成配置。当FPGA处于从串行模式时,可编程只读存储器和可编程门阵列由外部时钟进行时钟。

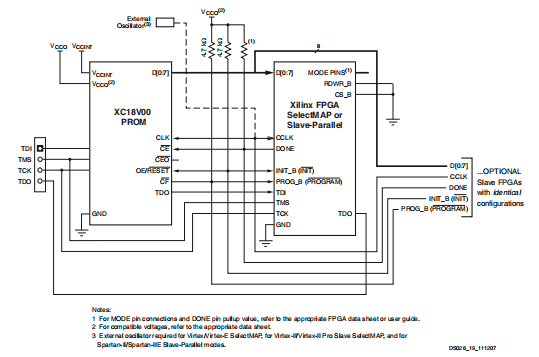

X-Ref目标

当FPGA处于主选择映射模式时,FPGA生成一个驱动可编程只读存储器的配置时钟。当FPGA处于从机并行或从机选择映射模式时,外部振荡器生成配置时钟

驱动PROM和FPGA。启用CE和OE后,可在PROM数据(D0-D7)引脚上获得数据。新数据在每个上升时钟边缘后的短访问时间内可用。数据在CCLK的后续上升沿上被时钟送入FPGA。自由运行振荡器可用于从机并联或从机SELECMAP模式。

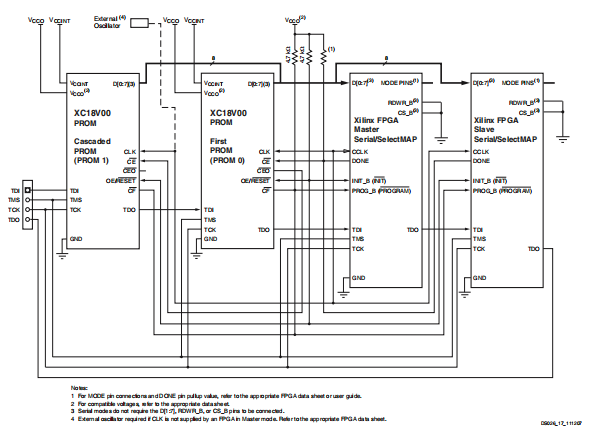

通过使用ceo输出可以级联多个设备

驱动以下设备的CE输入。该链中所有prom的时钟输入和数据输出是相互连接的。所有设备都是兼容的,可以与该系列的其他成员或

xC17v00一次性可编程串行可编程只读存储器系列。

引出线图

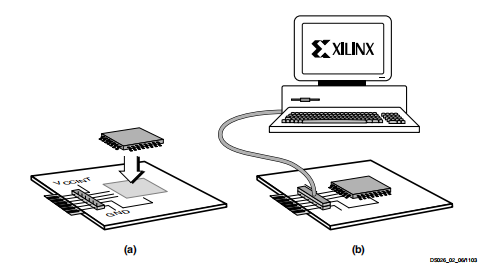

在系统编程中

系统内可编程的PROM可以单独编程,也可以通过标准的4针JTAG协议将两个或多个PROM链接在一起并在系统中编程,如图2所示。在系统编程中提供了快速和高效的设计迭代,并消除了不必要的包处理或设备套接。Xilinx开发系统使用Xilinx冲击软件和下载电缆、第三方JTAG开发系统、JTAG兼容板测试仪或模拟JTAG指令序列的简单微处理器接口提供编程数据序列。冲击软件还输出串行矢量格式(SVF)文件,用于接受SVF格式的任何工具和自动测试设备。

在系统编程期间,所有输出都保持在高Z状态或保持在钳位级别。

光电复位

ISP编程算法要求发出重置,使OE变低。

外部程序设计

Xilinx可重新编程的prom也可以由第三方设备程序员编程,提供了使用带有in的预编程设备的额外灵活性。-

X-Ref目标

系统可编程选项,用于将来的增强和设计更改。

可靠性和耐久性

Xilinx系统内可编程产品在系统程序/擦除周期内提供20000的保证耐久性水平,并至少保留20年的数据。每个设备都符合该耐久极限内的所有功能、性能和数据保留规范。有关设备质量、可靠性和过程节点信息,请参阅ug116,xilinx设备可靠性报告。

设计安全性

Xilinx系统内可编程可编程可编程可编程可编程可编程可编程只读存储器设备包含先进的数据安全功能,以完全保护编程数据,防止通过JTAG进行未经授权的读取。表3显示了可用的安全设置。

用户可以设置读取安全位,以防止内部编程模式通过JTAG被读取或复制。设置后,它允许设备擦除。擦除整个设备是重置读安全位的唯一方法。

IEEE 1149.1边界扫描(JTAG)

XC18V00系列完全符合IEEE标准1149.1边界扫描,也称为JTAG。提供测试访问端口(TAP)和寄存器,以支持所有要求的边界扫描指令,以及IEEE标准1149.1规定的许多可选指令。此外,JTAG接口用于在系统编程(ISP)中实现,以便于XC18V00设备上的配置、擦除和验证操作。

作为指令扫描序列的一部分加载到IR中的指令寄存器值

边界扫描寄存器

边界扫描寄存器用于在extest、sample/preload和clamp指令期间控制和观察设备管脚的状态。XC18V00上的每个输出管脚都有两个寄存器级,它们对边界扫描寄存器起作用,而每个输入管脚只有一个寄存器级。

对于每个输出管脚,距离TDI最近的寄存器级控制并观察输出状态,而距离TDO最近的第二级控制并观察管脚的高Z启用状态。

对于每个输入管脚,寄存器级控制并观察管脚的输入状态。

标识寄存器

IDcode是一个固定的、由供应商指定的值,用于以电子方式标识要处理的设备的制造商和类型。IDcode寄存器的宽度为32位。可以使用idcode指令将idcode寄存器移出进行检查。IDcode可通过JTAG提供给任何其他系统组件。

xc18v00 idcode值见表5。

IDcode寄存器具有以下二进制格式:vvvv:ffff:ffff:aaaa:aaaa:cccc:cccc:ccc1,其中

V=模具版本号F=系列代码(XC18V00系列为50H)A=ISP PROM产品ID(XC18V04为26H或36H)C=公司代码(Xilinx为49H)

注:根据IEEE标准1149.1的定义,IDcode寄存器的LSB始终被读取为逻辑“1”。

笔记:

1。idcode字段中的<v>表示设备的修订代码(十六进制),可能会有所不同。

用户代码指令允许访问一个32位用户可编程的草稿板,该草稿板通常用于提供有关设备编程内容的信息。通过使用用户代码指令,用户可编程识别码可以移出进行检查。在XC18V00设备的编程过程中,该代码被加载到用户代码寄存器中。如果设备为空或在编程期间未加载,则用户代码寄存器包含ffffffff h。

XC18V00抽头特性

XC18V00系列通过一个四线测试接入端口(TAP)执行系统编程和IEEE1149.1边界扫描(JTAG)测试。这简化了系统设计,并允许标准自动测试设备执行这两个功能。XC18V00抽头的交流特性描述如下

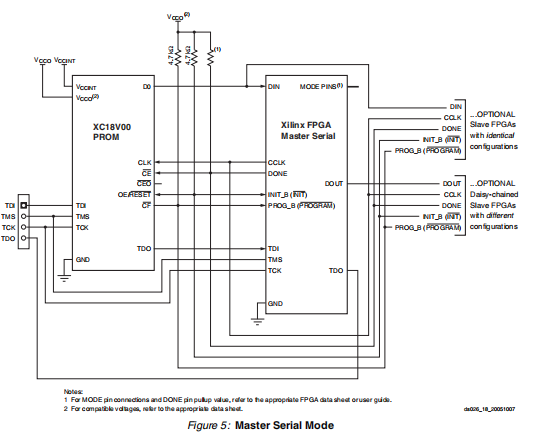

连接配置Proms

可编程只读存储器的数据输出驱动引线FPGA设备的DIN输入。

主FPGA CCLK输出驱动PROM的CLK输入(仅在主串行和主选择映射模式中)。

可编程只读存储器的CEO输出驱动菊花链(如果有)中下一个可编程只读存储器的CE输入。

所有PROM的OE/复位插脚都连接到所有FPGA设备的初始化插脚。此连接确保在任何(重新)配置开始之前重置PROM地址计数器,即使在V故障启动重新配置时也是如CCNT可从完成引脚驱动PROM CE输入。第一个(或唯一一个)可编程只读存储器的CE输入可由所有目标FPGA设备的完成输出驱动,

但前提是不永久接地。CE也可以永久性地低束缚,但这会使数据输出保持活动状态,并导致不必要的最大供电电流为10 mA。

从机并行/选择映射模式类似于从机串行模式。数据从可编程只读存储器中时钟输出,每个CCLK一个字节,而不是每个CCLK周期一个位。特殊配置要求见FPGA数据表。

启动FPGA配置

xc18v00设备包含一个名为cf的管脚,可通过jtag config指令进行控制。通过jtag执行config指令时

CF低300–500 ns,重置FPGA并启动配置。

要使用此功能,必须将CF引脚连接到FPGA上的程序引脚。

影响软件还可以通过“加载FPGA”设置发出jtag config命令来启动FPGA配置。

20针封装没有专用的CF针。对于20针封装,可以使用CF→D4设置进行布线。

只有在不使用并行输出模式的情况下,cf pin才对pin 7起作用。

选择配置模式

XC18V00支持串行和并行配置方法。配置模式可通过XC18V00设备中的用户控制寄存器进行选择。此控制寄存器可通过JTAG访问,并使用Xilinx Impact软件上的“并行模式”设置进行设置。串行输出是默认配置模式。

主串行模式摘要可配置逻辑块(CLB)的I/O和逻辑功能及其相关互连由配置程序建立。程序可以在通电时自动加载,也可以在命令下加载,具体取决于三个FPGA模式插脚的状态。在主串行模式下,FPGA自动从外部存储器加载配置程序。Xilinx Proms是为适应主串行模式而设计的。

通电或重新配置后,只要所有三个FPGA模式选择引脚都低(m0=0,m1=0,m2=0),则FPGA进入主串行模式。数据在一条数据线上按顺序从可编程只读存储器读取。同步由临时信号CCLK的上升沿提供,该上升沿由FPGA在配置期间生成。

主串行模式提供了一个简单的配置接口。配置FPGA只需要一条串行数据线、一条时钟线和两条控制线。从可编程只读存储器中的数据按顺序读取,通过内部地址和位计数器访问,这些计数器在CCLK的每个有效上升沿上递增。如果用户可编程,则FPGA上的双功能DIN管脚仅用于配置,则在正常操作期间,必须将其保持在规定的水平。XilinxFPGA家族使用片上拉阻器自动处理这一问题。

级联配置proms对于配置为串行菊花链的多个FPGA,或在串行或选择映射配置模式下需要较大配置内存的单个FPGA,级联PROM提供额外内存

xc18v00设备可以通过使用ceo进行级联

输出驱动下游设备的CE输入。链中所有XC18V00设备的时钟输入和数据输出是相互连接的。在读取第一个PROM的最后一个数据后,发送给PROM的下一个时钟信号断言其CEO输出低,并将其数据线驱动到高Z状态。第二个可编程只读存储器识别其CE输入端的低电平并启用其数据输出。

配置完成后,所有如果PROM OE/复位引脚,则级联PROM复位。

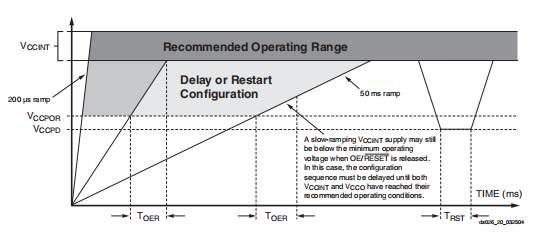

复位和通电复位激活

通电时,装置要求V电源在规定的V上升时间内单调上升至额定工作电压。如果电源不能满足此要求,则设备可能无法正确执行开机重置。在通电过程中,CCNTCCNT

oE/复位被PROM保持在低位。

一旦所需物资到达各自的位置

Por(上电复位)阈值,OE/复位释放延迟(t最小值),以便在启动配置前使电源稳定。OER

OE/复位引脚连接到外部上拉电阻,也连接到目标FPGA的初始B引脚。为了系统利用缓慢上升的电源,一个额外的电源监控电路可以用来延迟目标。

配置直到系统电源达到最小值保持OE/复位引脚低,从而产生工作电压。

当释放oe/reset时,fpga的init_b引脚被拉高,允许fpga的配置序列开始。如果电源降到断电阈值以下(v)PROM复位和OE/复位再次保持在低位,直到达到POR阈值后。CCPD

OE/复位极性不可编程。

对于全功率平台闪存可编程只读存储器,会发生重置。

每当OE/复位被断言(低)或CE被解除断言(高)。地址计数器被重置,CEO被驱动高,剩余的输出被置于高z状态。

待机模式每当CE被认定为高电平时,可编程只读存储器就进入低功耗待机模式。地址被重置。不管OE输入的状态如何,输出都保持在高z状态。JTAG引脚TMS、TDI和TDO可以处于高Z状态或高。

当使用fpga done信号驱动prom ce pin高以降低配置后的备用电源时,一个应使用外部上拉电阻器。通常使用330Ω上拉电阻,但请参考相应的FPGA数据表了解推荐的完成引脚上拉值。如果

完成电路连接到一个LED,以指示FPGA配置完成,并且还连接到可编程只读存储器。

CE引脚使能低功耗待机模式,则应使用外部缓冲器驱动LED电路,以确保有效Proms CE插针上的转换。如果是低功耗待机

可编程只读存储器不需要模式,则应将CE针脚接地。5V容限I/O每个可重新编程的可编程可编程只读存储器上的I/O即使通过3.3V的核心电源,也完全可以承受5伏的电压。这允许5伏的CMOS信号直接连接到可编程只读存储器的输入端,而不会造成损坏。此外,3.3V电源可在向I/O施加5V信号之前或之后施加。在混合的5V/3.3V/2.5V系统中,用户管脚、核心电源(V)和输出电源(V)可以按任意顺序供电。这使得PROM设备CCNTCCNTCCO

客户控制位xc18v00 proms具有客户可访问的各种控制位。这些可以在使用Xilinx Impact软件中的“跳过用户阵列”对阵列进行编程后进行设置。冲击软件可以设置这些位,以启用可选的JTAG读取安全、并行配置模式或CF→D4引脚功能。