EL4340和EL4342是固定的单位增益放大器多路复用器具有高转换率和优异的带宽视频切换。这些器件具有高阻抗输出国家(HIZ),使多台设备的输出是连接在一起。一个掉电模式(ENABLE)包括关闭非必要电路,功耗敏感应用程序。使能引脚,当拉高,设置EL4340和EL4342进入待机功耗模式-消费仅仅18mW功率。在EL4340一个附加特征是一个锁存使能函数(LE),它允许使用一个独立的逻辑控制常见的逻辑总线。

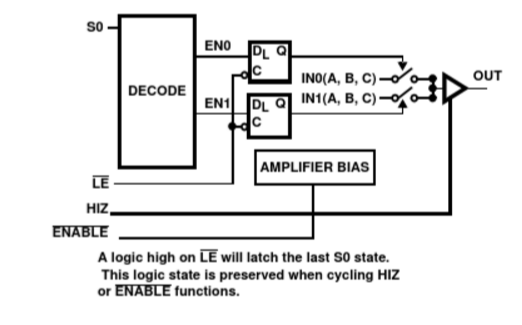

EL4340框图:

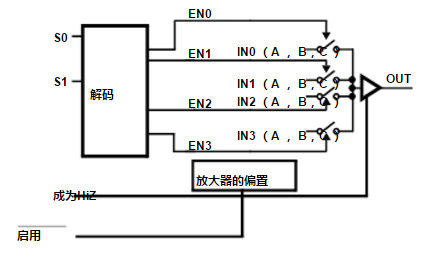

EL4343框图:

应用信息

一般的EL4340和EL4342三重2:1和4:1多路放大器是理想的高性能切换器矩阵元素和路由器。主要功能包括:缓冲高阻抗模拟输入和卓越的AC性能,在输出负载下降到150Ω的视频线驾驶。单位增益电流反馈输出放大器的稳定工作进容性负载和带宽优化的负载5pF的同一个500Ω平行。总输出电容即可PCB的电容和一个外部负载之间分割电容。

接地连接为了获得最佳的隔离和串扰抑制,所有GND引脚和NIC引脚必须连接到GND层。控制信号的S0、S1、启用、LE、HIZ-这些都是二进制编码,TTL/CMOS兼容的控制输入。在S0、S1引脚选择的输入。所有三个放大器同时切换从它们各自的输入端。启用, LE、HIZ引脚用于禁用部分以节省功率,锁存器中的最后一个逻辑州和三态输出放大器,分别。为控制信号上升和下降时间小于10ns的使用终端电阻接近部分将减少瞬变耦合到输出端。

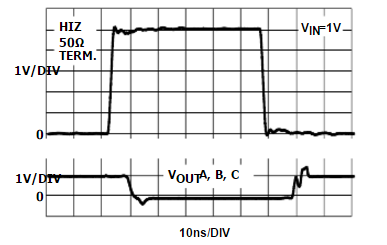

HIZ瞬态响应

电注意事项

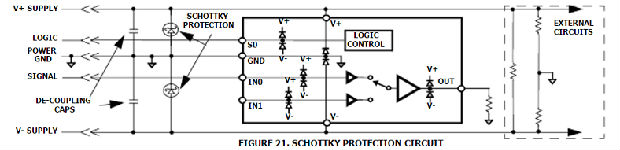

ESD保护电路使用内部二极管的所有引脚在V+和V-用品。此外,一个的dV/DT-触发钳连接在V +和V-端子之间,如图中等效电路1通过的引脚说明4节表。该dv / dt的触发钳施加最大供应接通1V/μs的压摆率。破坏性的电流可超过1V/μs的流动供电率-的高层,这样的因为在热插拔。在这些条件下,额外方法应采用保证率的上升是不超标。必须考虑到,在该系统的命令是施加于V+和V-的引脚,以及模拟和逻辑输入引脚。肖特基二极管(摩托罗拉MBR0550T或当量)从V+连接到地和V-与地(图肖特基保护电路)将分流破坏性电流远离内部的V +和V- ESD二极管事件的V +供应被施加到器件上的V型电源之前。若正电压被施加到所述逻辑或模拟视频输入引脚前V+的施加,电流将流过内部ESD二极管的V+引脚。大量存在去耦电容器和其它电路的负载效应连接到V+,可能会导致通过破坏性的电流ESD二极管等有源电路器件内。因此,适当的电流对数字限制和模拟输入是必要的,以防止在该时间损坏这些输入的电压比V+更积极HIZ状态内部下拉电阻保证了该设备将活跃??的HIZ管脚的连接。该HIZ状态在大约15ns的(图HIZ瞬态响应)通过将建立在HIZ引脚为逻辑高电平(>2V) 。如果选择了HIZ状态输出是与大约一高阻抗1.4MΩ取1.5pF在以10μA的偏置电流从输出并联连接。使用这种状态下,当一个以上多路复用器共享公共输出。在HIZ状态下的输出是三态,并保持其Z高,即使在??高转换率的存在。供应在此状态期间的电流是相同的活性状态。

肖特基保护电路

PC板布局

电路的AC性能在很大程度上取决于注意对设计的印刷电路板。以下是建议,以实现最佳的高频从你的PC板的性能。

使用低电感元件,如芯片电阻和贴片电容,强烈推荐。

最大限度地减少信号走线的长度。走线电感和电容可以很容易地限制了电路的性能。避免尖角,采用圆润的边角时可能。孔在信号线加电感在高频应尽量避免。 PCB走线大于1"开始带信号的上升/下降显示出传输线路特性为1ns或更少的时间。高频性能可降解为痕迹大于1英寸,除非带状线被使用。

匹配通道通道模拟量I/O走线长度及布局对称。这将最大限度地减少传输延迟不匹配。

最大限度地利用交流脱钩PCB层数。所有的信号I/O线应铺设在连续的地平面(即没有分割面或在这些线路板间隙) 。避免过孔在信号I/O线。

使用适当的价值和终端电阻位置。端接电阻应尽可能靠近器件作为可能。

当测试使用质量好的连接器和电缆,匹配的电缆类型,并保持电缆长度为最低限度。

2个电源去耦电容的最小推荐(1000pF的,0.01μF)尽量靠近器件尽可能-避免了帽和设备之间的通孔因为过孔添加不必要的电感。大帽可较远。当导通孔是必需的布局,它们应尽可能远离该装置尽可能进行路由。

网卡引脚被置于输入引脚的两侧。这些引脚内部没有连接到芯片。这是建议这些引脚连接到地,以尽量减少串扰。

QFN封装需要额外的PCB布局规则的散热焊盘

散热垫电连接到电源V-通过高电阻IC基板。它的主要功能是提供一种用于在IC散热。然而,由于该通过基板连接到V-供应,散热焊盘必须连接到V-电源,以防止多余的电流流向散热垫。办不此引脚到GND,因为这可能会导致大背偏置电流GND和V-之间流动。该EL4342采用包与D2=2.48毫米和E2=3.4毫米焊盘尺寸。如果散热垫是最大交流才能达到最佳性能连接到一个专用的去耦层中的多层PC板。的情况下的专用层是不可能的,AC性能可在上部的频率被降低。散热垫的要求与功率成正比耗散和环境温度。专用层省去了单独的导热衬垫面积。当一个专用层是不可能的1“× 1”的衬垫区域是足够对于正在消退0.5W的+50°C的环境中EL4342 。焊盘面积的要求应该由一个案例评估案件的依据。

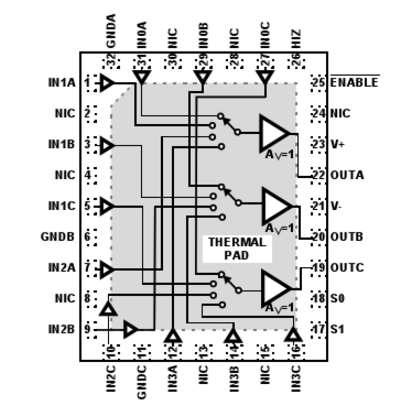

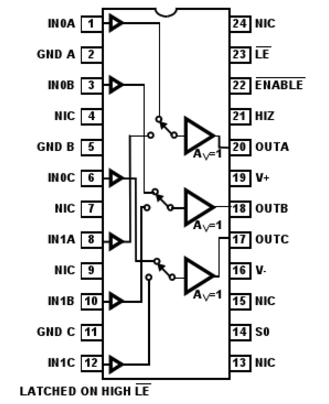

EL4340引脚图:

EL4343引脚图: