DIT4096点击型号即可查看芯片规格书

192点击型号即可查看芯片规格书

384点击型号即可查看芯片规格书

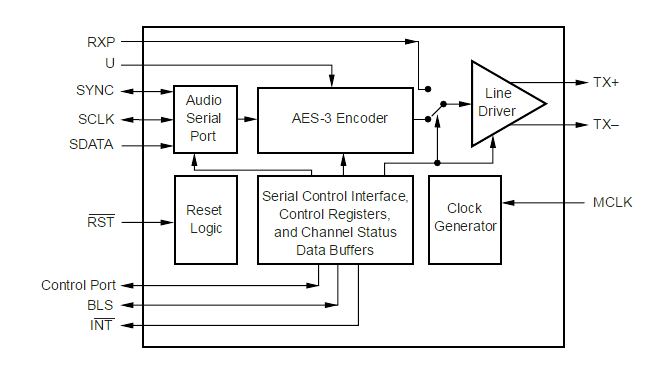

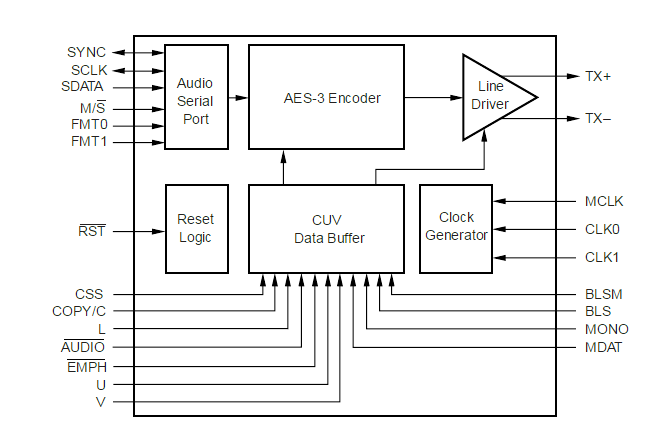

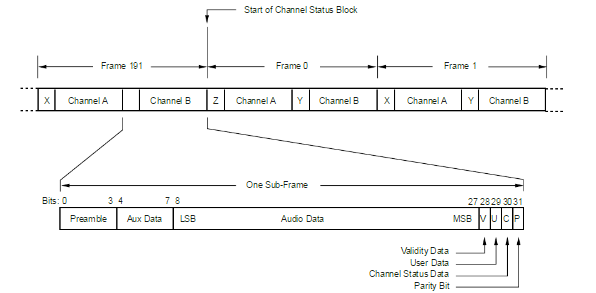

DIT4096是一个完整的数字音频发射器,适合专业和消费类音频应用。SAM-耦率高达96kHz的支持。该DIT4096的COM帘布层与用于AES-3,IEC-60958的要求,并EIAJCP1201接口标准。图1和图2示出了DIT4096框图在软件和硬件控制模式下使用时。该MODE输入(引脚28)确定用于控制模型配置DIT4096内部功能。在软件模式下,串行控制端口用于写入和读取片内控制寄存器和状态的缓冲区。在硬件模式下,专用提供了用于配置和状态控制输入引脚。该DIT4096包括音频串行端口,其用于接口标准的数字音频源,如模数(A/D)转换器,数字信号处理器器(DSP),和音频解码器。支持左对齐,右-有道理的,我2S个数据格式提供。在AES-3编码器产生的多路码流,连续的泰宁音频,状态和用户数据。参见图3为复用的数据格式。该数据然后双相标记编码,并输出到差分线路驱动器。线路驱动器输出被连接到传输介质,无论是电缆或光纤。在双绞线或同轴电缆的情况下电缆,变压器通常用于耦合驱动输出到传输线路。这同时提供了隔离和改进的共模抑制。光学transmis-锡永中,TX+(引脚18)的驱动器输出端被连接到光发射模块。

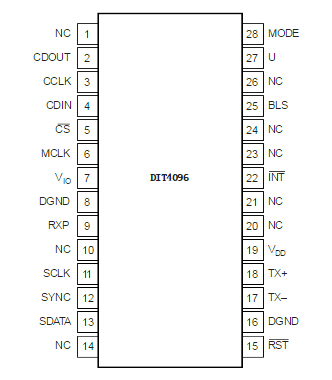

图1

复位和掉电手术

DIT4096包括复位输入,RST(引脚15),这是用于强制复位序列。当DIT4096是第一加电时,用户必须断言RST低,以便开始复位序列。该RST输入必须是低的迷你妈妈为500ns。该RST输入然后强制为高,使正常操作。对于软件模式下,复位序列将强制所有内部寄存器的默认设置。此外,复位序列将强制所有通道状态位为0软件模式。而RST输入为低时,发送器的输出,TX-(引脚17)和TX+(引脚18),被迫地。当设置RST高,TX-和TX+输出将保持低,直到同步时钟的上升沿被检测到时销12一旦发生这种情况,TX-和TX+输出将变得活跃,由AES-3的输出驱动编码器。在软件模式下,DIT4096还包括软件复位和关断位,位于控制寄存器02H。该软件复位位,RST,而软件关断位,PDN,均为高电平有效。

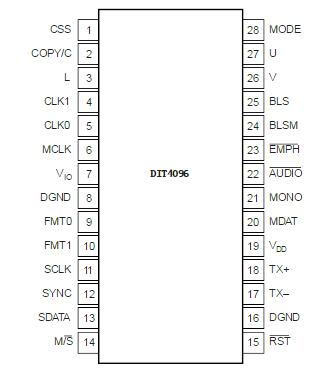

图2

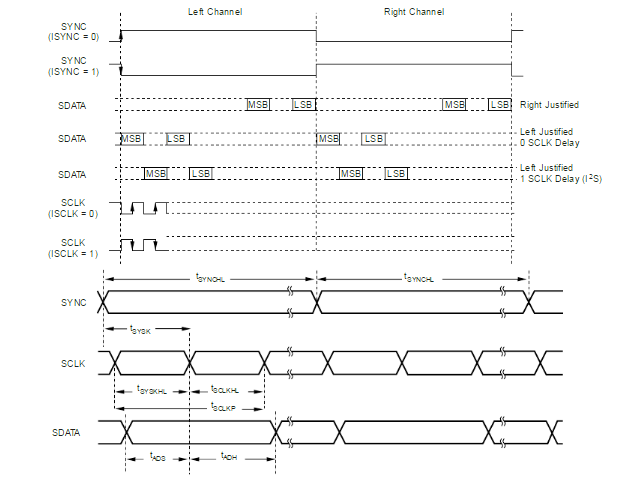

音频串行端口

音频串行端口用于连接一个3线接口DIT4096到音频源,如一个A/D转换器或DSP。该端口支持采样频率高达96kHz。该端口的信号包括SDATA(引脚13),同步(引脚12),和SCLK(引脚11)。的SDATA引脚为串行数据输入的端口。SCLK引脚可以是输入或输出,并且是用来同步串行数据端口。SYNC引脚可可以是输入或输出,并且提供所述框架synchroni-矩阵特殊积时钟端口。SYNC引脚也可以用作一个数据对于信道状态,用户和有效性的数据锁存时钟投入在硬件模式下,用户的数据输入软件模式。

图3

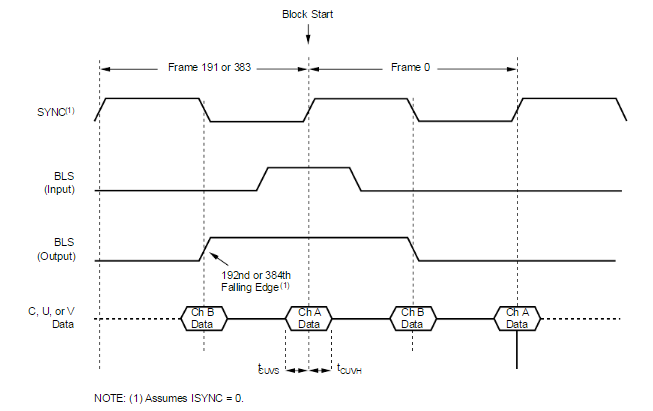

BLOCK启动输入/输出

开始被用来指示信道状态的开始数据块,其开头帧0用于AES-3数据流。对于DIT4096,块起始信号,BLS(引脚25),可以是输入或输出。在软件模式下,BLS的方向被使用在控制寄存器中的BLSM位置01H(默认为输入)。在硬件模式下,BLS的方向由BLSM输入(引脚24)来设置。如果BLSM=0,BLS的销是一个输入端。如果BLSM=1,BLS的引脚是输出。对于软件模式下操作时,该块起始信号是同步chronized到音频串行端口的帧同步时钟,SYNC(引脚12)。当BLS被配置为输入引脚,它是采样在SYNC的上升沿时在ISYNC位控制寄存器03H被设置为0,否则,它被采样的下降沿同步的边沿时iSync的位被设置为1,如果BLS高时进行采样,然后一个块起始条件表示。当BLS被配置为输出与所述ISYNC位被设置为0,BLS将为高,在每192落下SYNC的立体声模式,或者每384下降沿边缘的SYNC为单声道模式。BLS将会进入低就下面的下降沿。如果ISYNC位被设置为1,然后BLS转变在SYNC的上升沿。硬件模式下的操作类似软件模式操作化,所不同的是只有有限数量的可用于该音频的串行端口的数据格式。对于左和右对齐格式,BLS的行为,因为它会在与ISYNC=0。对于我的软件模式2S个数据格式,BLS的行为,因为它会与ISYNC=1的软件模式。

通道状态数据输入

通道状态的数据输入,由控制模式确定在使用中。在软件模式下,通道状态数据缓冲区通过串行控制端口访问。缓冲区操作在详细了解本数据手册的章节中介绍题为通道状态缓冲器运行(软件模式只)。在硬件模式下,通道状态数据输入由两个用户可选方法之一来完成。

CSS的输入

在硬件模式下,CSS输入状态(引脚1)决定的专用信道状态的输入的功能。当CSS=0时,复印(引脚2),L(引脚3),音频(引脚22),和EMPH(引脚23)输入用于设置关联的信道状态的数据位。COPY(复制)和L输入用于对于消费者操作设置复制保护,或说明该发射机工作在专业模式,而不复制保护。该音频输入被用来指示是否正被发送的数据是PCM音频数据,或非音频数据。该EMPH输入用于指示是否PCM音频数据已被使用的预加重的50/为15μs标准。当CSS=1时,信道状态数据被输入以串行时尚的C输入(引脚2)。数据在时钟的上升和下降沿SYNC输入的边缘(引脚12)。所有频道状态的数据位可以写入在该模式下,允许更大灵活性比以前的硬件模式与案例CSS=0。

图4

用户和有效性数据输入

在AES-3数据流中的用户数据比特允许一个方便的方式来传输用户定义或应用spe-cific数据包含一个AES-3接收机的另一装置。在U输入(引脚27)是用在软件和硬件模式输入以串行方式的用户数据。图5表示U输入时序图。有效性的数据,用于表明样品是无差错的音频数据,或该样品是有缺陷的,不适合供进一步处理。在软件模式下,VAL中位控制寄存器01H被用于写入的有效性的数据。在硬件模式下,V输入(引脚26)用于输入的在串行方式有效性的数据。请参考图5V输入时序硬件模式。当VAL或V=0时,这表示所述音频数据是否有效和适合于进一步的处理。当VAL或V=1,那么音频取样是有缺陷的,不应该被使用。

图5

线路驱动器输出

DIT4096包括一个平衡线路驱动器。线路驱动器输出TX-(引脚17)和TX+(引脚18)。在软件模式下,该线驱动器的输入是从导通的任一输出芯片的AES-3编码器,或从外部的AES-3编码在RXP源输入(引脚9)。输入源选择使用控制寄存器的01位BYPASSH(默认为片上的AES-3编码器)。在硬件模式下,线路驱动器源总是片上的AES-3编码器。线路驱动器的输出将遵循AES-3编码数据源中的正常操作。在一个硬件或软件复位,或当设备处于掉电模式,该线路驱动器的输出将被强制到地面。输出也可以强制地在软件模式中的任何时间通过设置TXOFF位为1,控制寄存器01。

引脚