CDCE906点击型号即可查看芯片规格书

511点击型号即可查看芯片规格书

4095点击型号即可查看芯片规格书

127点击型号即可查看芯片规格书

350点击型号即可查看芯片规格书

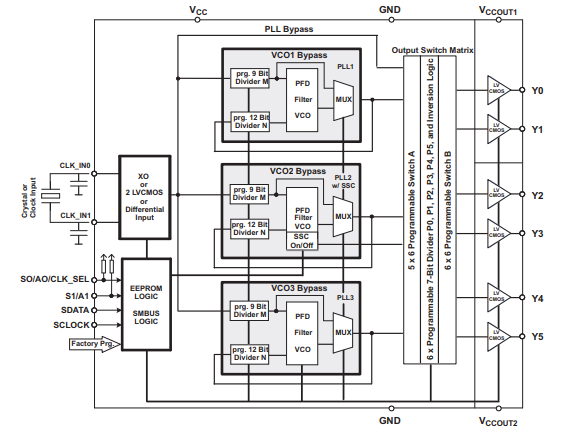

CDCE906是体积最小,功能最强大的时钟合成器/抖动清除器产品之一可编程输出开关矩阵[6x6]尽管物理外形很小,但CDCE906却是如此每个输出包括7位后分频器灵活。它有能力几乎产生差分输入时钟或单晶。该降低系统EMISMBus数据接口控制器。

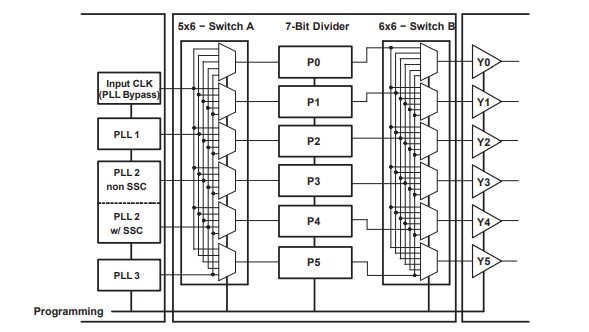

为了实现独立的输出频率,参考分频器M和每个PLL的反馈分频器N.对于M分频器,可以设置为1到511的值,对于N分频器,可以设置为1到4095。 PLL-VCO(压控振荡器)频率比被路由到自由可编程输出开关矩阵的任何一个六项产出。开关矩阵包括一个额外的7位后分频器(1到127)和一个反相逻辑每个输出。深M / N分频比允许从任何参考输入频率产生零ppm时钟(例如,a27 MHz)。

CDCE906包括三个支持SSC(扩频时钟)的PLL。PLL1,PLL2和PLL3设计用于高达167 MHz的频率,并针对具有宽分频器的零ppm应用进行了优化因素。

PLL2还支持中心扩频和下扩频时钟(SSC)。这是一种常见的技术减少电磁干扰。此外,摆率可控(SRC)输出边沿可最大限度地降低EMI噪声。根据PLL频率和分频器设置,内部环路滤波器组件将自动进行调整以实现PLL的高稳定性和优化的抖动传递特性。该器件支持非易失性EEPROM编程,易于定制应用。它是预编程的具有出厂默认配置(参见图13),可以重新编程为其他应用程序在进入PCB或通过系统内编程重新编程之前的配置。不同的设备设置通过串行SMBus接口编程。

两个可编程输入S0和S1可用于控制每个应用中最苛刻的逻辑控制设置(输出禁用为低,输出3态,断电,PLL旁路等)。

CDCE906有三个电源引脚,VCC,VCCOUT1和VCCOUT2。VCC是设备的电源。它采用3.3 V单电源供电。VCCOUT1和VCCOUT2是输出的电源引脚。

VCCOUT1为输出Y0和Y1供电,VCCOUT2为输出Y2,Y3,Y4和Y5供电。两个输出电源电压为2.3 V至3.6 V.输出电压低于3.3 V时,输出驱动电流受限。

CDCE906的工作温度范围为0°C至70°C。

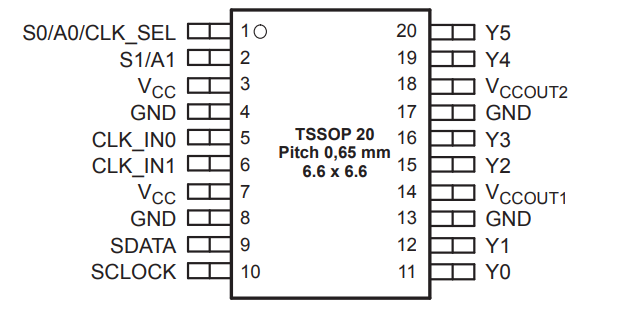

终端分配图

特征

高性能3:6基于PLL的时钟合成器/乘法器/分频器

用户可编程PLL频率

无需编程EEPROM编程

通过SMBus数据轻松实现在线编程

宽PLL分频比允许0 ppm输出时钟错误

生成精确视频(27 MHz或54 MHz)和多个音频系统时钟采样频率(fS = 16,22.05,24,32,44.1,48,96 kHz)

时钟输入接受水晶或单端LVCMOS或差分输入信号

接受从8 MHz到最高的水晶频率4 MHz

接受LVCMOS或差分输入频率高达167 MHz

两个可编程控制输入[S0 / S1,A0 / A1]用于用户定义的控制信号

具有输出频率的六个LVCMOS输出高达167 MHz

LVCMOS输出可以编程为互补信号

可选择的输出频率可编程输出开关矩阵[6x6]尽管物理外形很小

低周期抖动(典型值60 ps)

功能扩频时钟(SSC)

可编程中心扩展SSC调制

功能框图

输出开关矩阵图

应用信息

为了增强时钟合成器的灵活性和功能,提供了双信号串行接口。它跟随SMBus规范2.0版,它基于I的操作原理。

通过SMBus,各种器件功能(例如各个时钟输出缓冲器)可以单独使用启用或禁用。与SMBus数据接口关联的寄存器初始化为其默认设置上电,因此使用此接口是可选的。通常会进行时钟寄存器寄存器的更改在系统初始化时,如果需要的话。时钟驱动器串行协议接受字节写入,字节读取,块写入和块读取操作控制器。

对于块写/读操作,必须按从最低到最高字节的顺序访问字节(最重要的位优先)具有在传输完整字节后停止的能力。对于字节写和字节读操作,系统控制器可以访问单独寻址的字节。一旦发送了一个字节,它将被写入内部寄存器并立即生效。随着上升ACK位的边沿,这适用于每个传输的字节,无论是字节写还是块写序列。

如果启动EEPROM写周期,则内部SMBus寄存器的数据将写入EEPROM。在EEPROM写入期间,在编程之前,不允许数据通过SMBus发送到器件序列完成。但是,在编程序列(字节读取或块)期间可以读出数据读)。编程状态可由EEPIP监控,字节24位7。

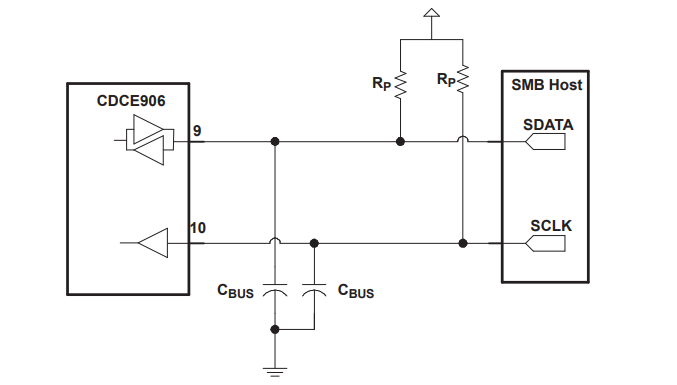

下图显示了CDCE906时钟合成器如何连接到SMBus。请注意通过上拉电阻(Rp)的电流必须符合SMBus规范(最小100μA,最大350μA)。如果CDCE906未连接到SMBus,则SDATA和SCLK输入必须连接10kΩ上拉电阻到VCC以避免浮动输入条件。

SMBus硬件接口

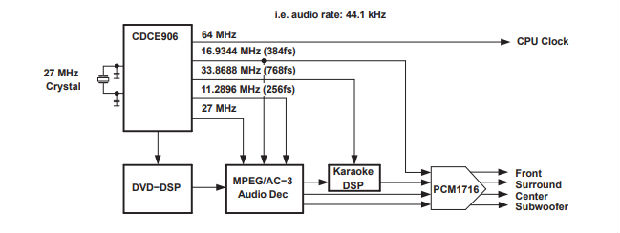

CDCE906的典型应用是数字高清电视系统,游戏机,DVD播放器,DVD插件用于多媒体PC和台式机的卡。

CDCE906系统应用程序框图

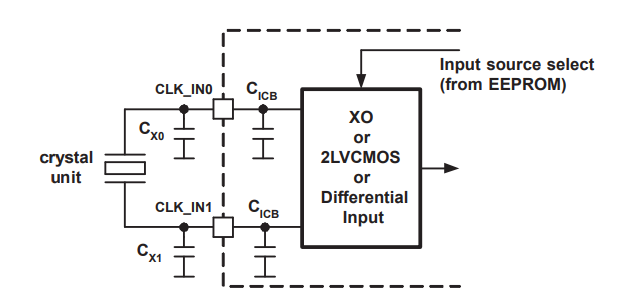

时钟输入(CLK_IN0和CLK_IN1)

CDCE906具有两个时钟输入,可用作:

晶体振荡器输入(默认设置)

两个独立的单端LVCMOS输入

差分信号输入

专用时钟输入可以通过字节11的输入信号源Bit [7:6]选择。

晶体振荡器输入

晶振模式下的输入频率范围为8 MHz至54 MHz。CDCE906使用皮尔斯型振荡器包含反相放大器反馈电阻的电路。但是,用户必须添加外部电容CX0,CX1)与晶体的输入负载电容相匹配(见下图)。所需的值可以计算:

CX0 = CX1 = 2×CL-CICB,

其中CL是晶体单元规定的晶体负载电容,CICB是晶体管的输入电容器件包括板电容(PCB的杂散电容)。

例如,对于CL为9 pF且CICB为4 pF的基本27 MHz晶振,

CX0 = CX1 =(2×9pF)-3pF = 15pF。

重要的是使用从器件到晶体单元的短PCB走线来保持晶体管的杂散电容振荡器环路降至最低。