HI5746点击型号即可查看芯片规格书

180点击型号即可查看芯片规格书

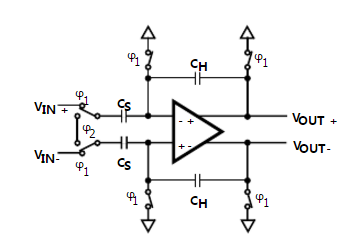

HI5746是一个10位全差分采样管道A/D转换器与数字误差校正逻辑。图模拟输入采样和保持中示出的电路,用于前端差动式差分出样品的分析和保持(S/H)。该开关是由一个内部控制采样时钟,该时钟是一个不重叠的两相的信号,φ1和φ2从主采样时钟。在采样相位,φ1中,输入信号被施加到采样电容,CS。同时在保持电容,CH,被排出到模拟地。在下降沿φ1该输入信号进行采样的采样的底板电容器。在下一时钟相位,φ2,的两个底板采样电容器连接在一起,所述保持电容器切换到运算放大器的输出节点。充电那么C之间重新分配S和CH完一个采样和保持周期。前端采样和保持输出是一个完全差分,采样数据的代表性模拟输入。该电路不仅执行采样和保持功能,而且也将转换为单端输入到fully-差分输出的转换器芯。在采样相,VIN销仅看到的导通电阻的开关和CS。这些组分的相对较小的值导致一个为250MHz的转换器的典型的全功率输入带宽。

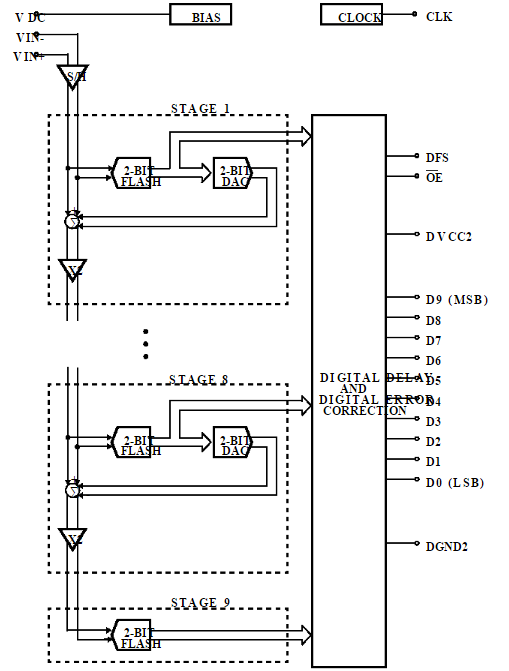

功能框图

模拟输入采样和保持

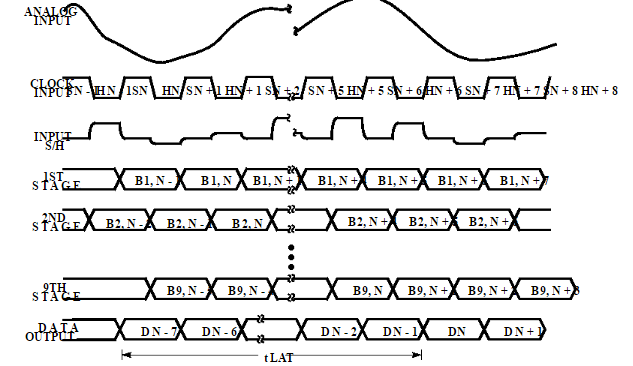

如附图中的功能框图和时序图图中,八个相同的管道subconverter阶段,每一个包含2位佛罗里达州灰烬转换器和一个2位乘法的数字 - 模拟转换器,按照S/H的电路与第九级是一个2位的佛罗里达州灰变换器。管道中的每个转换阶段将在一个被抽检相和放大中的其它时钟相位。每个人subconverter时钟信号偏置180度从所得的交替前级的时钟信号阶段在流水线执行相同的操作。每八个相同的2位subconverter的输出阶段是含有补充比特的两比特的数字字要使用所述数字误差校正逻辑。的输出每个subconverter阶段被输入到所述数字延迟线由内部采样时钟进行控制。的功能数字延时线是时间对准8的数字输出相同的2位subconverter阶段与相应的第九级闪蒸器的应用之前,输出18位结果的数字误差校正逻辑。该数字误差校正逻辑使用的补充位正确生成最终的前十名中可能存在的任何错误该转换器的位数字数据输出。由于此转换器的管道的性质,数字数据表示的模拟输入采样输出到在时钟的模拟后的第7个周期的数字数据总线的取样。这个延时特定网络连接编为数据潜伏期。后的数据的延迟时间,该数字数据代表每个成功的模拟样本输出在随后的时钟周期。数字输出数据是通过双同步到外部采样时钟缓冲锁存技术。数字误差的输出校正电路有两种补码或偏移根据不同的数据格式的状态的二进制格式选择(DFS)控制输入。

时序图

参考电压输入

VREF-和VREF+该HI5746的目的是接受两个外部基准电压源在VREF输入引脚。典型操作该转换器需要VREF+键被设置在+2.5V和VREF- 到被设置为2.0V。然而,应该指出的是,输入在V结构REF+和VREF- 输入引脚由一个电阻分压器的分压中的一个电阻器(标称500Ω)连接V之间REF+和VREF-和分频器(名义上2000Ω)所连接的其他电阻器V之间REF-和模拟地。这允许用户在供应只有+2.5V V选项REF+基准电压源与+2.0V VREF-由内部产生输入结构的分压作用。该HI5746与V测试REF-等于+2.0V和VREF+等于+2.5V产生一个全差分模拟输入电压范围±0.5V.VREF+和VREF-可以从上面的不同电压。为了最小化总的转换器的噪声,建议有足够的高频去耦时可提供两的参考电压输入引脚,VREF+和VREF-。

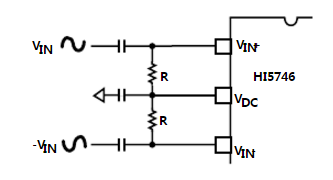

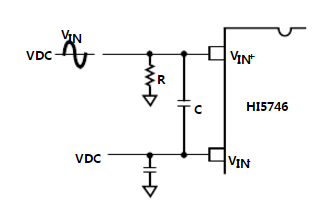

AC耦合差分输入

模拟输入

差分连接模拟输入到HI5746是一个差分输入端,能被CON组fi gured在这取决于信号的各种方式源和所需的性能水平。一个完全差分连接(图AC耦合差分输入和图直流耦合差分输入)将给用于转换器的最佳性能。由于HI5746是由一个单一的+ 5V模拟电源供电,模拟输入被限制为接地和+ 5V之间。对于差分输入连接这意味着该模拟输入共模电压范围从0.25V到4.75V。ADC的性能不发生变化显着与模拟输入共模电压的值。直流电压源,VDC,等于3.2V(典型值) ,由提供给用户,以帮助简化电路设计时使用交流耦合的差分输入。这种低输出阻抗电压源没有被设计成为一个参考,但使一个优良的直流偏压源,并保持良好的模拟中输入共模电压范围的温度。为交流耦合差分输入(图AC耦合差分输入)假定V之间的差REF+通常为2.5V ,而VREF-,典型的2.0V , 0.5V是。满量程实现了V时IN和-VIN输入信号是0.5VP-P与-VIN存在180度相结合VIN。该转换器将在正满量程时, VIN+输入为VDC+ 0.25V和VIN- 输入是在VDC- 0.25V (VIN+ -VIN- = +0.5V) 。相反,转换器将在负满量程时, VIN+输入等于VDC-0.25V和VIN-是在VDC+0.25V (VIN+ - VIN- = -0.5V).模拟输入可以被直流耦合(图直流耦合差分输入) ,只要输入是内模拟输入共模电压范围( 0.25V≤VDC≤4.75V)。电阻R,在图27中完全没有必要但可以用作负载设置电阻器。电容器,C,从V连接IN+到VIN- 有利于滤波器的任何高在输入频率的噪音,还提高了性能。各地20pF的值是苏夫连接古老而可以在交流中使用耦合输入,以及。但是,请注意,值电容C选择必须考虑到的最高模拟输入信号的频率分量。

直流耦合差分输入

模拟量输入

单端连接在图交流耦合单端输入中所示的CON组fi guration可与使用单端交流耦合输入。再次,假定V之间的差REF+,通常2.5V和VREF- 通常为2V ,为0.5V 。如果VIN是1VP-P正弦波,则VIN+是1VP-P在积极的正弦波骑电压等于直流电压。该转换器将在正满规模在VIN+是VDC+0.5V(VIN+ -VIN- = +0.5V)并且将在负满量程时, VIN+是等于VDC-0.5V(VIN+ - VIN- = -0.5V)。SUF网络cient一定的余量被提供,以使输入电压从不以上+ 5V或低于AGND 。在这种情况下,直流电压可介于0.5V和4.5V ,而不在ADC的一个显着的变化性能。以产生直流电压的最简单的方法是使用直流偏压源,VDC时, HI5746的输出。单端模拟输入可以被DC耦合(图直流耦合差分输入),只要输入是模拟输入内共模电压范围。电阻R,在图直流耦合单端输入中不是绝对必需的,但可被用作负载设置电阻。电容器,C,从V连接IN+到VIN- 有利于滤波器的任何高在输入频率的噪音,还提高了性能。各地20pF的值是苏夫连接古老而可以在交流中使用耦合输入,以及。但是,请注意,值电容C选择必须考虑到的最高模拟输入信号的频率分量。单端信号源可以提供更好的整体系统性能,如果是网络首先转换之前差驾驶HI5746 。

交流耦合单端输入

数字输出控制和时钟要求

HI5746提供了一个标准的高速接口外部TTL逻辑系列。为了确保HI5746 ,占空比的额定性能时钟的周期应在50%以内±5%.它也必须具有低抖动和标准TTL电平工作。HI5746的表现,只会在保证转化率大于1 MSPS 。这样可以确保适当的内部动态电路的性能。类似地,当功率是音响首先施加到转换器中,最多20的在一个采样速率高于1 MSPS的周期将必须是有效数据之前执行的是可用的。数据格式选择(DFS)引脚设置能确定的数字数据输出的格式。当在逻辑低电平时,数据将在偏移二进制格式的输出。在2级的时候,在逻辑高时,数据将被输出补码格式。