BAT754点击型号即可查看芯片规格书

MMBD7000点击型号即可查看芯片规格书

CDCM7005点击型号即可查看芯片规格书

功能描述

8通道电压控制放大器–LNA、VCAT、PGA、LPF和CW混频器VCA5807是一种集成电压控制放大器(VCA),专门为高性能、小尺寸的超声系统设计。

可编程低噪声放大器(LNA)

24/18/12 dB增益

-0.25/0.5/1 Vpp线性输入范围

-0.63/0.7/0.9 nv/rthz输入参考噪声

-可编程主动端接

40dB低噪声压控衰减器(VCAT)

24/30分贝可编程增益放大器(PGA)

三阶线性相位低通滤波器(LPF)

-10、15、20、30兆赫

-巴特沃斯特性

噪声/功率优化(全链)

-0.75 nv/rthz时为99 mw/ch

-1.1 nv/rthz时为56 mw/ch

-连续波模式下80 mW/ch

优秀的设备间增益匹配

-±0.5 dB(典型)和±1.05 dB(最大)

低谐波失真

快速一致的过载恢复

低频声纳信号处理

连续波多普勒无源混频器(CWD)

-低闭合相位噪声–1时为156 dBc/Hz

kHz关闭2.5兆赫载波

-相位分辨率1/16λ

-支持32x、16x、8x、4x和1x CW时钟

-3次和5次谐波的12dB抑制

-灵活的输入时钟

14毫米x 14毫米,100针TQFP

应用

医学超声成像

无损评价设备

声纳成像

是必需的。VCA5807集成了完整的时间增益控制(TGC)成像路径和连续波多普勒(CWD)路径。它还允许用户选择各种功率/噪声组合之一,以优化系统性能。因此,VCA5807不仅适用于高端系统,而且适用于便携式系统,是一种合适的超声模拟前端解决方案。

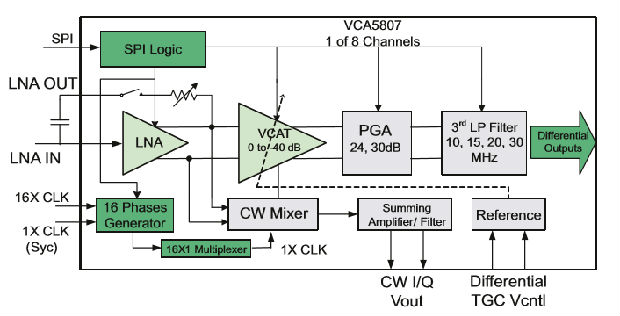

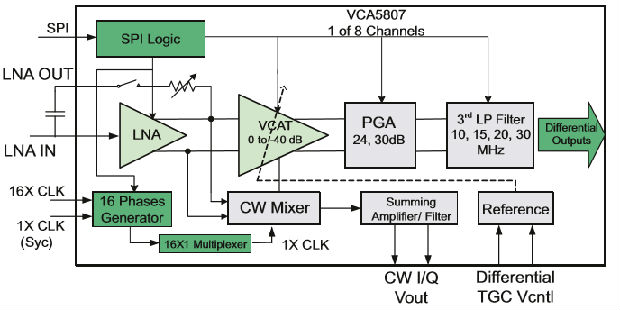

VCA5807包含八个通道的电压控制放大器(VCA)和连续波混频器。该VCA包括低噪声放大器(LNA)、电压控制衰减器(VCAT)、可编程增益放大器(PGA)和低通滤波器(LPF)。LNA增益可编程以支持250 mvpp到1 vpp输入信号。LNA也支持可编程主动终端。超低噪声VCAT提供40dB的衰减控制范围,提高了整体低增益信噪比,有利于谐波成像和近场成像。PGA提供24分贝和30分贝的增益选项。在ADC之前,可以将LPF配置为10兆赫、15兆赫、20兆赫或30兆赫,以支持不同频率的超声应用。此外,VCA5807的信号链可以处理低于100kHz的信号频率,这使得它不仅可以用于超声波应用,也可以用于声纳应用。

VCA5807集成了一个低功率无源混频器和一个低噪声和放大器,实现了一个单芯片CWD波束形成器。16个可选相位延迟可应用于每个模拟输入信号。同时采用独特的三阶和五阶谐波抑制滤波器,提高了连续波的灵敏度。

VCA5807有一个14mm x 14mm,100pin的TQFP封装,它被指定用于-40°C到85°C的操作。

静电放电损伤的范围从细微的性能退化到整个设备故障。精密集成电路可能更容易受到损坏,因为非常小的参数变化可能导致设备不符合其公布的规格。

寄存器写入描述

不同模式的编程可以通过pins sen(串行接口启用)、sclk(串行接口时钟)、sdata(串行接口数据)和reset组成的串行接口完成。所有这些引脚都有一个下拉电阻接地20kΩ。当SEN低时,位到设备的串行移位被启用。当SEN激活(低)时,串行数据SData被锁存在SCLK的每个上升沿。当SEN低时,串行数据在每24个SCLK上升沿加载到寄存器。如果字长度超过24位的倍数,则忽略多余的位。数据可以在单个有源SEN脉冲内以24位字的多个字加载(在SEN下降沿后,有一个内部计数器对24个时钟组进行计数)。该接口可以在20兆赫到低速(几赫兹)的SCLK频率下工作,甚至可以在非50%占空比SCLK下工作。数据分为两个主要部分:寄存器地址(8位)和数据本身(16位),加载到地址寄存器上。当用未使用的位写入寄存器时,这些位应设置为0。

寄存器读出说明

该设备包括一个选项,其中内部寄存器的内容可以被读出。这可能有助于诊断测试,以验证外部控制器和VCA之间的串行接口通信。首先,<register readout enable>位(reg0[1])需要设置为“1”。然后,用户应该启动一个串行接口循环,指定寄存器(A7-A0)的地址,该寄存器的内容必须被读取。数据位是“不关心”。设备将在sdout引脚上输出所选寄存器的内容(d15-d0)。从SCLK的下降沿开始,sdout的典型延迟t8为20 ns。对于低速SCLK,SDOUT可以锁定在SCLK的上升沿。对于高速SCLK,即SCLK周期小于60ns时,最好在SCLK的下一个下降沿锁定SDout。

VCA寄存器描述

LNA输入阻抗配置(主动端接可编程性)

可以通过寄存器52[4:0]配置不同的LNA输入阻抗。通过启用和禁用LNA输出和ACTX引脚之间的反馈电阻,可以相应地调整LNA输入阻抗。LNA增益和52[4:0]设置之间的关系。TGC和CW路径的输入阻抗设置相同。

VCA5807还具有4个预设的主动端接阻抗,如52[7:6]中所述。内部解码器用于根据不同的LNA增益选择适当的电阻。

VCA5807是一种集成电压控制放大器(VCA)解决方案,专门为需要高性能和小尺寸的超声系统设计。VCA5807集成了完整的时间增益控制(TGC)成像路径和连续波多普勒(CWD)路径。它还允许用户选择各种功率/噪声组合之一,以优化系统性能。VCA5807包含八个通道;每个通道包括低噪声放大器(LNA)、电压控制衰减器(VCAT)、可编程增益放大器(PGA)、低通滤波器(LPF)和连续波混频器。

此外,VCA5807中的多个功能适用于超声波应用,例如主动端接、单通道控制、快速上/下电响应、可编程钳位电压控制、快速一致的过载恢复和打开。因此,VCA5807为超便携手持系统带来了优质的图像质量,一直到高端超声系统。此外,VCA5807可以支持声纳应用,考虑到其出色的低频(<100 kHz)响应。

低噪声放大器(LNA)

在许多高增益系统中,低噪声放大器是实现整体性能的关键。使用新的专有架构,VCA5807中的LNA提供了卓越的低噪声性能,同时与具有类似噪声性能的基于CMOS的架构相比,在非常低的静态电流下工作。LNA执行单端输入到差分输出电压转换。它可配置为24/18/12db的可编程增益,其输入参考噪声分别为0.63/0.70/0.9nv/√hz。可编程增益设置使线性输入范围达到1vpp,实现了新传感器技术所需的高信号处理能力。较大的输入信号可以被低噪声放大器接受;但是,由于信号超过低噪声放大器的线性工作区域,信号可能会失真。结合低噪声和高输入范围,实现了宽输入动态范围,满足了各种超声成像模式的高要求。

低噪声放大器(LNA)

在许多高增益系统中,低噪声放大器是实现整体性能的关键。使用新的专有架构,VCA5807中的LNA提供了卓越的低噪声性能,同时与具有类似噪声性能的基于CMOS的架构相比,在非常低的静态电流下工作。LNA执行单端输入到差分输出电压转换。它可配置为24/18/12db的可编程增益,其输入参考噪声分别为0.63/0.70/0.9nv/√hz。可编程增益设置使线性输入范围达到1vpp,实现了新传感器技术所需的高信号处理能力。较大的输入信号可以被低噪声放大器接受;但是,由于信号超过低噪声放大器的线性工作区域,信号可能会失真。结合低噪声和高输入范围,实现了宽输入动态范围,满足了各种超声成像模式的高要求。

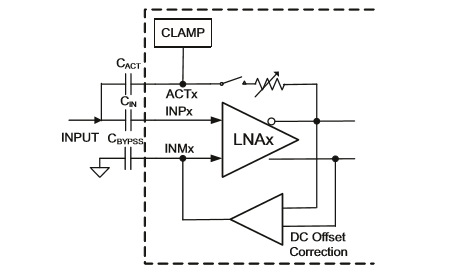

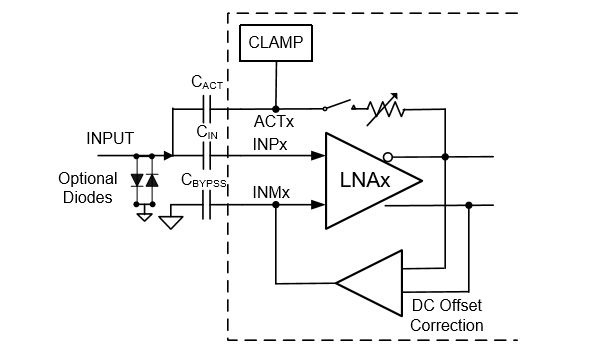

LNA输入的内部偏压约为+2.4V;信号源应通过适当尺寸的电容器(即,≥0.1微F)与LNA输入进行交流耦合。为实现低直流偏移漂移,VCA5807为每个放大器级集成了一个直流偏移校正电路。为了提高过载恢复率,采用积分器电路提取低噪声放大器输出的直流分量,然后反馈到低噪声放大器的互补输入进行直流偏移校正。该直流偏移校正电路具有高通响应,可以作为高通滤波器处理。有效角频率由连接在inm的电容器cBypass确定。电容器越大,角频率越低。为了在最高高压滤波器截止频率下稳定运行,可选择一个≥15nF的电容器。这个角频率几乎与cBypass的值成线性比例。例如,15nf给出了大约100kHz的角频率,而47nf给出了33kHz的有效角频率。如果需要低频操作,也可以通过寄存器52[12]禁用/启用直流偏移校正电路。大电容器(如1微F)可用于设置LNA直流偏移校正电路的低角频率(<2 kHz)。

VCA5807可以被动或主动终止。主动端接在超声应用中是首选的,以减少不匹配的反射,并在不过度降低噪声系数的情况下获得更好的轴向分辨率。主动端接值可预设为50、100、200、400Ω;其他值也可由用户通过寄存器52[4:0]进行编程。在actx和信号源之间需要一个反馈电容器,在有源端接路径上,当VCA5807看到过载信号时,还使用钳位电路来创建低阻抗路径。钳位电路限制了低噪声放大器输入端的大输入信号,提高了VCA5807的过载恢复性能。当寄存器52[10:9]=0时,根据LNA增益设置,钳位电平可自动设置为350mvpp、600mvpp、1.15vpp。其他钳形电压,如1.15Vpp、0.6Vpp和1.5Vpp,也可以通过设置寄存器52[10:9]来实现。这种钳位电路的设计还可以获得良好的脉冲反转性能,并减少非对称输入的影响。请注意,在LNA增益切换过程中,钳位设置可能会发生变化。因此,在调整LNA增益时,尤其是当过载信号超过夹紧电压时,必须考虑钳位的固定时间。

电压控制衰减器

电压控制衰减器设计成具有线性In-dB衰减特性;即,对于控制电压(VCNTL)的每一个相等增量,以dB为单位的平均增益损失(见图2)是恒定的

衰减器本质上是一个可变分压器,它由串联输入电阻(RS)和七个并联FET组成,FET并联并由顺序激活的限幅放大器(A1到A7)控制。vcntl是vcntlp和vcntlm之间的有效区别。每个削波放大器可以理解为一个专门的电压比较器具有软传输特性和良好的控制输出极限电压。参考电压v1至v7在0V至1.5V控制电压范围内等距分布。当控制电压通过每个剪切放大器的输入范围增加时,放大器输出从FET几乎关闭的电压上升到FET完全打开的高电压。当每个场效应管接近其开启状态且控制电压持续升高时,下一个剪切放大器/场效应管组合将接管分段线性衰减特性的下一部分。因此,低控制电压使大部分场效应管关闭,产生最小的信号衰减。同样,高控制电压会打开场效应管,导致最大的信号衰减。因此,每个场效应管的作用是降低由RS和并联场效应管网络形成的分压器的分流电阻。

此外,为了在VCA5807中获得更好的相位噪声性能,还实现了数字控制TGC模式。衰减器可以由数字控制而不是模拟控制电压VCNTL。该模式可由寄存器位59[7]设置。变压分压器采用固定串联电阻,场效应管采用并联电阻。通过连接开关SW1-7,可以打开每个FET。打开每个开关可以产生大约6分贝的衰减。这可以由寄存器位59[6:4]控制。这种数字控制特性可以消除VCNTL电路中的噪声,确保TGC路径具有更好的信噪比和相位噪声。

电压控制衰减器的噪声与衰减系数呈单调关系。在较高的衰减下,输入参考噪声较高,反之亦然。然后,衰减器的噪声被PGA放大,成为ADC输入端的噪声地板。在衰减器的高衰减工作范围内,即VCNTL高,衰减器的输入噪声可能超过LNA的输出噪声;然后衰减器成为下一个PGA级和ADC的主要噪声源。因此,与LNA输出噪声相比,衰减器的噪声应最小化。VCA5807的衰减器设计用于在高衰减(低通道增益)下实现非常低的噪声,并在近场中实现更好的信噪比。

低输入噪声是PGA中的首选,其噪声贡献不应在衰减器后过多地降低ADC的信噪比。在最小衰减(用于小输入信号)时,LNA噪声占主导地位;在最大衰减(大输入信号)时,PGA和ADC噪声占主导地位。因此,只要放大后的信号能超过ADC的噪声下限,PGA的24dB增益就能获得更好的信噪比。

可启用PGA电流箝位电路(寄存器51),以提高VCA的过载恢复性能。如果我们在过载后测量输出的标准偏差,对于0.5伏VCNTL,正常情况下约为3.2 LSB,即过载后约1个时钟周期内输出稳定。在禁用电流钳位电路的情况下,该值接近4 LSB,这意味着输出稳定之前的时间更长;但是,在启用电流钳位电路的情况下,对于pga输出水平>2dbfs,hd3将降级。例如,对于–2dbfs输出电平,hd3下降约3db。为了使输出动态范围最大化,采用钳位电路,最大PGA输出电平可以超过2VPP(0 dbfs线性输出范围)。因此,应选择具有良好过载恢复性能的ADC。

VCA5807集成了一个反混叠滤波器,其形式为可编程低通滤波器(LPF)在跨阻放大器中。低通滤波器是一种差分、有源、三阶滤波器,具有巴特沃思特性,每八度滚降一个典型的18dB。通过串行接口可编程,-1db频率角可以设置为10MHz、15MHz、20MHz和30MHz中的一个。同时为所有通道设置滤波器带宽。

此外,还实现了一种可选的直流偏移校正电路。此校正电路与LNA中使用的电路相似。它提取PGA输出的直流分量,并反馈给PGA的互补输入进行直流偏移校正。该直流偏移校正电路还具有高通响应,截止频率为80kHz。如果需要<80kHz的操作,可通过寄存器0x33[4]禁用直流偏移校正电路。

连续波波束形成器

连续波多普勒是中高端超声系统的关键功能。与TGC模式相比,连续波路径需要处理高动态范围和严格的相位噪声性能。由于上述的严格要求,连续波波束形成通常在模拟域中实现。在超声系统中,包括无源延迟线、有源混频器和无源混频器等,正在实现多种波束形成方法。其中,被动混频器实现了功率和噪声的优化。它满足了连续波处理的动态范围宽、相位噪声低、增益准确、相位匹配等要求。

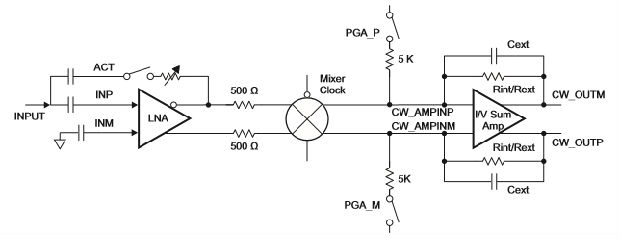

下面分别给出了简化的连续波路径方块图和同相或正交(I/Q)通道方块图。每个连续波通道包括一个低噪声放大器、一个电压-电流转换器、一个基于开关的混频器、一个带低通滤波器的共享求和放大器以及时钟电路。所有的分块都包括匹配良好的同相和正交信道,以实现良好的图像频率抑制和波束形成精度。结果表明,I/Q通道的图像抑制率优于超声系统所需的-46dbc。

LNA配置

LNA输入耦合和去耦

LNA闭环结构在内部进行补偿,以获得最大的稳定性,而无需外部补偿元件。LNA输入偏压为2.4V,需要交流耦合。典型的输入配置如图84所示。CIN是输入交流耦合电容器。CACT是主动端接反馈路径的一部分。即使未使用主动端接,也需要CACT来实现夹钳功能。CACT≥1微F和CIN的推荐值≥0.1微F。T/R开关和LNA输入之间通常放置一对钳位二极管。根据传感器回波幅度的不同,可以考虑使用具有适当正向电压降(即BAT754/54系列、BAS40系列、MMBD7000系列或类似系列)的肖特基二极管。

LNA输入配置

这种结构最大限度地减少了信号源的任何负载,否则可能导致一个频率相关的分压器。闭环设计产生非常低的偏移和偏移漂移。cBypass(≥0.015微F)用于设置高通滤波器截止频率,并将互补输入解耦。它的截止频率与cBypass值成反比。如表8所示,可通过寄存器59[3:2]调整高功率因数截止频率。T/R开关输出的低频信号,如振铃缓慢的信号,可以过滤掉。此外,高功率因数可以最大限度地降低来自DC-DC转换器、脉冲重复频率(PRF)触发器和帧时钟的系统噪声。大多数超声系统的信号处理单元包括数字高通滤波器或FPGA或ASIC中的带通滤波器(BPF)。在这些模块中可以实现进一步的噪声抑制。如果在某些应用中需要低频信号检测,可以禁用

电压控制衰减器

VCA5807中的衰减器由一对差分控制输入(VCNTLM/P引脚)控制。差分控制电压在0伏到1.5伏之间。此控制电压根据衰减器的线性(单位:dB)特性改变衰减器的衰减。其最大衰减(最小信道增益)出现在VCNTLP VCNTLM=1.5 V处,最小衰减(最大信道增益)出现在VCNTLP-VCNTLM=0处。典型的增益范围是40dB,并且保持不变,与PGA设置无关。

当只有单端VCNTL信号可用时,可以使用

VCNTLM针脚接地。如下图所示,TGC增益曲线与VCNTLP-VCNTLM成反比。

低频支持

VCA5807的信号链可以处理低于100kHz的信号频率,使VCA5807不仅可以用于医学超声应用,还可以用于声纳应用。必须关闭PGA积分器才能启用低频支持。同时,如图65所示,可以使用1微F这样的大电容器来设置低角频率的LNA直流偏移校正电路

CW配置

连续波求和放大器为了简化连续波系统的设计,在VCA5807中实现了一个求和放大器,将8通道混频器的电流输出求和转换为差分电压输出。在保持连续波工作所需的全动态范围的同时,求和放大器具有低噪声和低功耗的特点。

该求和放大器有5个内部增益调整电阻,可提供32种不同的增益设置系统设计人员可以根据信号强度和传感器灵敏度轻松调整连续波路径增益。对于任何其他增益值,支持外部电阻选项。总和放大器的增益由LNA后500Ω电阻与内部或外部电阻网络REXT/INT的比值决定,因此这些电阻之间的匹配比绝对电阻值起着更重要的作用。在芯片上实现了1%以上的匹配。由于工艺的变化,电阻的绝对公差可能更高。如果使用外部电阻,I/Q通道之间或多个VCA之间的增益误差可能会增加。建议使用内部电阻设置增益,以实现更好的增益匹配(跨通道和多个VCA)。对于外部电容器CEXT,该求和放大器具有一阶LPF响应,以去除混频器中的高频分量,例如2F0±FD。

多个VCA5807通常用于并行扩展连续波束形成器的信道数。这些VCA5807S的连续波输出可以在外部进行求和和和过滤,以获得所需的增益和滤波器响应。需要交流耦合电容器CAC来阻断连续波载波信号的直流分量。CAC可以在1uF到10sμF之间变化,这取决于慢血流所需的低频多普勒信号。在16/18位差分音频ADC之前,多个VCA5807S的I/Q输出可与低噪声外部差分放大器相加。可以考虑采用超低噪声差分精密放大器opa1632和ths4130。

时钟噪声和连续波路径噪声的结合会降低连续波的性能。内部时钟电路的设计是为了实现良好的相位噪声要求的连续波操作。VCA5807连续波路径在1KHz偏移下的相位噪声优于155dBc/Hz。因此,混频器时钟输入的相位噪声需要优于155dbc/hz。

在16、8、4×_CW工作模式下,16、8、4×_CW时钟需要低相位噪声时钟(即,

CLKP U 16X/CLKM U 16X引脚),以保持良好的连续波相位噪声性能。1×_CW时钟(即CLKP U1X/CLKM U1X引脚)仅用于同步多个VCA5807芯片,不用于解调。因此,1_cw时钟的相位噪声不是一个问题。可使用频率为_cw的连续时钟或宽度大于1/(n_cw)的单脉冲。

另一方面,在1×_CW工作模式下,由于两个CLKP U16X/CLKM U16X和CLKP U1X/CLKM U1X管脚都用于混频器解调,因此需要低相位噪声时钟。一般来说,高转速率时钟具有较低的相位噪声,因此在连续波工作中,高振幅和快速转速率时钟是首选。在CMOS时钟模式下,5V的CMOS时钟可以达到最高的转换速率。

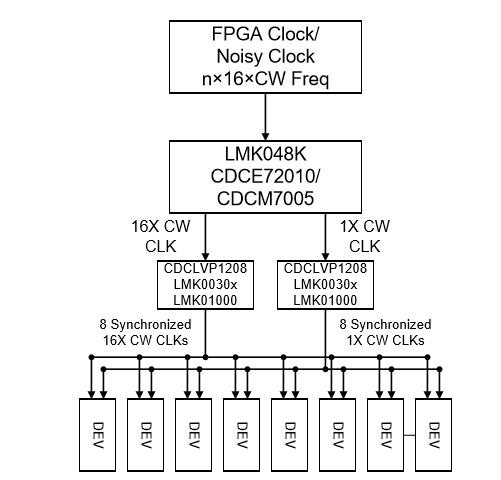

只要分频器的相位噪声低于目标相位噪声,分频器就可以改善时钟相位噪声。分频时钟的相位噪声可以提高约20log10n db,其中n是16、8或4的分频因子。如果混频器低时钟1×_cw的目标相位噪声在1KHz非载波时为160dbc/hz,则16×_cw的时钟相位噪声应优于160-20log1016=136dbc/hz。TI的抖动清洗器LMK048X/CDCM7005/CDCE72010超过此要求,可用于VCA5807。在4x/1x模式中,由于n较小,高质量的输入时钟有望达到相同的性能。因此,16X模式是首选模式,因为它降低了系统时钟设计的相位噪声要求。此外,相位延迟精度由内部时钟分频器和分配电路来规定。在16x操作模式下,由于16x CLK,连续波操作范围限制为8兆赫。16x时钟的最大时钟频率为128兆赫。在8x、4x和1x模式中,可以支持高达15MHz的高CW信号频率,但性能降低较小,例如,相噪声在15MHz时比在2MHz时降低9dB

随着系统信道数的增加,时钟分布变得更加复杂。由于时钟缓冲器的负载电容增加了一个因数n,因此不建议使用一个时钟驱动器输出来驱动多个VCA。因此,时钟信号的下降和上升时间会降低。多个VCA5807的典型时钟安排如图95所示。每个时钟缓冲输出驱动一个VCA5807,以实现最佳的信号完整性和最快的转换速率,即更好的相位噪声性能。当时钟相位噪声不是问题时,泰语是。1×_CW时钟在32、16、8、4×_CW工作模式下,一个时钟驱动器输出可能会激励一个以上的VCA5807S,但在这种时钟分配网络的设计中应特别考虑。在典型的超声系统中,所有时钟最好是由同一个时钟源产生的,例如16×_cw、1×_cw时钟、音频ADC时钟、射频ADC时钟、脉冲重复频率信号、帧时钟等。通过这样做,可以最大限度地减少由时钟异步引起的干扰。

连续波支持电路

作为连续波电路设计的一般实践,同相和正交通道应严格对称,采用匹配良好的布局和高精度的元件。

在系统中,通常需要额外的带多极的高通墙壁滤波器(20Hz至500Hz)和低通音频滤波器(10kHz至100kHz)。由于连续波多普勒信号的范围从20Hz到20kHz,因此在这个范围内的噪声是至关重要的。因此,低噪声音频运算放大器适用于构建用于连续波后处理的有源滤波器,即opa1632、opa2211、lme49990、lmh6629或ths4130。更多的过滤器设计技术可以在上找到。TI的主动过滤器设计工具/docs/toolsw/folders/print/filterdesigner.html

滤波后的音频连续波I/Q信号由音频ADC采样,并由DSP或PC进行处理。尽管连续波信号的频率在20赫兹到20千赫之间,但更高的采样率ADC仍然是进一步提取和信噪比增强的首选。由于连续波信号的动态范围较大,需要高分辨率的ADC(≥16位),如ADS8413(2MSPS/16it/92DBFS SNR)和ADS8472(1MSPS/16bit/95DBFS SNR)。为了实现最佳的I/Q匹配,必须严格匹配同相和四次相位通道的ADC,不仅要进行幅度匹配,还要进行相位匹配。此外,同相和正交ADC通道必须同时采样。

电源管理

功率/性能优化

电源管理优先级

电源管理对于延长电池寿命和确保长时间运行起着至关重要的作用。VCA5807具有快速灵活的断电/上电控制功能,可最大限度延长电池寿命。VCA5807可通过外部插脚或内部寄存器断电/加电。下表显示了在调用电源管理时受影响的电路块和优先级。在该设备中,所有的断电控制逻辑上被“或”运算,以产生不同模块的最终断电。因此,高优先级控制可以覆盖低优先级控制。当VCA5807处于部分断电模式或完全断电模式时,VCA5807寄存器设置保持不变。

部分加电/断电模式也称为快速加电/断电模式。在这种模式下,信号通路中的大多数放大器断电,而内部参考电路保持激活状态。

部分断电功能允许VCA5807快速从低功耗状态唤醒。这种配置确保外部电容器放电缓慢,因此只要恢复这些电容器上的电荷,就需要最短的唤醒时间。VCA唤醒响应通常约为2μs或断电持续时间的1%,以较大者为准。最长的唤醒时间取决于连接在INP和INM的电容器,因为唤醒时间是将电容器充电到所需工作电压所需的时间。对于0.1μF的inp和15nf的inm,唤醒时间为2.5ms。对于较大的电容器,这一时间将更长。因此,VCA5807唤醒时间更依赖于VCA唤醒时间。断电时间是瞬时的,小于1微秒。

这种快速唤醒响应是便携式超声波应用的理想选择,在这种应用中,节能至关重要。

超声系统的脉冲重复频率可以从50kHz到500Hz不等,而成像深度(即接收路径的激活周期)则从10μs到数百us不等。当系统的PRF较低时,节电效果显著。在某些情况下,只有VCA断电,而ADC保持正常运行,以确保对FPGA的影响最小。

在部分断电模式下,VCA5807通常仅耗散12.5 mW/ch,与正常工作模式相比,功率降低了80%。此模式可以使用pin pdn_fast或寄存器位vca_partial_pdn设置。

完全断电模式

为了实现0.7mw/ch的最低功耗,VCA5807可置于完全断电模式。此模式通过寄存器VCA_complete_PDN或PDN_global pin控制。在完全断电模式下,包括VCA5807内的参考电路在内的所有电路都断电;连接到VCA5807的电容器放电。唤醒时间取决于为这些电容器充电所需的时间。唤醒时间取决于VCA5807在关机模式下的时间。

INP为0.1μF,INM为15nF,唤醒时间接近2.5ms。

连续波模式节能

通常,在连续波模式下,系统中只有一半的信道处于活动状态。因此,通过VCA_pdn_ch<7:0>进行单独的通道控制,可以关闭未使用的通道,大大节省功耗。在CW模式下的默认寄存器设置下,电压控制衰减器PGA仍处于激活状态。在调试阶段,PW和CW路径都可以同时运行。在实际操作中,这些模块需要手动断电。

测试模式

当直接探测VCA输出不可行时,VCA5807有一个测试模式,在该模式下,CH7和CH8 PGA输出可被带到CW管脚。通过监测这些连续波管脚,可以验证VCA操作的功能。PGA输出通过5KΩ电阻器连接到求和放大器的虚拟接地端(CW_IP_Ampinm/p、CW_QP_Ampinm/p)。当移除LPF电容器CEXT时,可在求和放大器输出端监测PGA输出。注意,总和放大器输出端的信号由于5KΩ电阻器而衰减。衰减系数为rint/ext/5KΩ。

如果用户想在不移除CExt的情况下检查PGA输出,另一种方法是在CW求和放大器断电时,直接测量CW_IP_Ampinm/p和CW_QP_Ampinm/p处的PGA输出。

一些寄存器与此测试模式相关。PGA测试模式启用:REG59[9];缓冲放大器断电REG59[8];缓冲放大器增益控制REG54[4:0]。根据缓冲放大器的配置,寄存器可以用不同的方式设置:

配置1:

在此配置中,测试输出可以在cw_ampinp/m下进行监控。

REG59[9]=1;测试模式已启用

REG59[8]=0;缓冲放大器断电

配置2:

在这种配置中,测试输出可以在cw_outp/m处进行监控。

REG59[9]=1;测试模式已启用

REG59[8]=1;缓冲放大器通电

REG54[4:0]=10h;内部反馈2K电阻已启用。也可以使用不同的值

电源、接地和旁路

在混合信号系统设计中,电源和接地设计起着重要的作用。在大多数情况下,印刷电路板(PCB)的布局应足以使用VCA5807的单一接地平面。应注意,该接地平面应在系统内的不同部分之间正确划分,以尽量减少模拟电路和数字电路之间的相互作用。此外,光隔离器或数字隔离器(如ISO7240)可将模拟部分与数字部分完全分离。因此,它们可以防止数字噪声污染模拟部分。

VCA5807的所有旁路和电源应参考其相应的接地平面。应使用0.1μF陶瓷片电容器(尺寸0603或更小)绕过所有电源插脚。为了使引线和迹线电感最小化,电容器应尽可能靠近电源插脚。如果允许安装双面组件,最好将这些电容器直接放置在组件下方。此外,更大的双极去耦电容器2.2微F至10微F,在较低频率下有效)也可用于主电源引脚。这些元件可以放置在离VCA5807本身很近的印刷电路板上(<0.5英寸或12.7毫米)。

VCA5807有许多需要绕过的参考电源,如CM-BYP、VHIGH和VREF-IN。这些引脚应至少绕过1微F;可以使用高值电容器来更好地抑制低频噪声。为获得最佳效果,请选择低电感陶瓷片电容器(尺寸0402,>1微F),并将其放置在尽可能靠近设备插脚的位置。

高速混合信号装置对各种噪声耦合敏感。噪声的一个主要来源是来自序列化程序和输出缓冲区/驱动程序的切换噪声。对于VCA5807,已注意确保设备内模拟和数字电源之间的交互保持在最小值。数字和模拟部分耦合和传输的噪声程度取决于每个电源和接地连接的有效电感。电源和接地引脚的有效电感越小,噪声抑制效果越好。因此,使用多个插脚连接每个电源和接地装置。通过使用适当的平面和层厚,在整个印刷电路板布局设计过程中保持低电感特性是很重要的。

版面布置

正确的接地和旁路、短引线长度以及使用接地和电源平面对高频设计尤为重要。使用VCA5807等高性能设备实现最佳性能需要仔细注意PCB布局,以最小化板寄生的影响并优化组件放置。多层印刷电路板通常确保最佳效果,并允许方便的元件放置。

此外,对于连续波时钟路径,尤其是在信道数较多的系统中,应考虑适当的延迟匹配。例如,如果时钟延迟是16倍时钟周期的一半,则可能存在22.5°C的相位误差。因此,信道间的定时延迟差异有助于波束形成器的精度。

为了避免通过电源引脚的噪声耦合,建议保持敏感的输入引脚,如INM、INP、ACT引脚始终来自AVDD 3.3 V和AVDD 5V平面。例如,连接到这些管脚的记录道或通孔不应穿过AVDD 3.3 V和AVDD 5V平面。