802点击型号即可查看芯片规格书

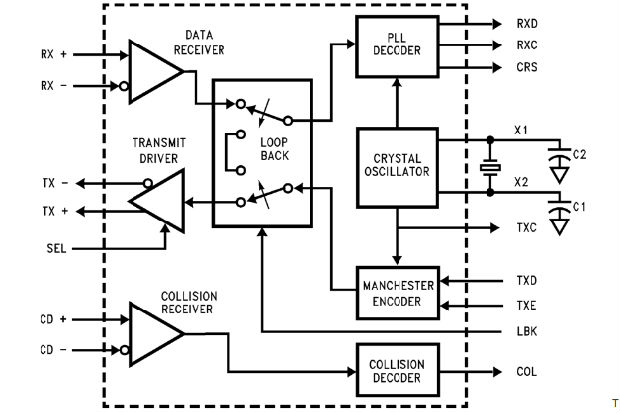

DP83910A由五个主要的逻辑块

一、振荡器产生的10MHz的发送时钟信号为系统时序

二、曼彻斯特编码器接受来自NRZ数据控制器编码数据,曼彻斯特和反MITS其差异,以通过存在差的收发信机无穷区间发送驱动器

三、曼彻斯特解码器接收来自曼彻斯特的数据收发器将其转换为NRZ数据和时钟脉冲并将其发送到控制器

四、该碰撞转换指示控制器的一个有效的10MHz的碰撞信号到PLL的存在

五、被断言路由数据的环回电路从曼彻斯特编码器回PLL解码器

振荡器

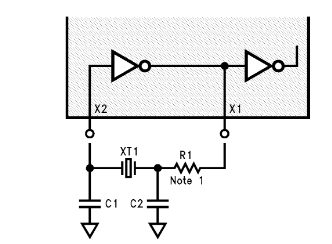

振荡器由一个20MHz的并联谐振控制晶体连接X1和X2之间或由一个外部关于X1时钟振荡器的20MHz的输出被分割由2产生用于控制 - 10MHz的发送时钟不可测量振荡器还提供了内部时钟信号提供给编码和解码电路如果晶体被连接到DP83910A它是推荐使用编所示,在电路图1可使用与该使用的组件满足以下水晶XT1 AT切割并联谐振晶体串联电阻s10X指定负载电容13pF的5精度0.005%(50ppm)C1 C2负载电容27 pF的在电阻器R1图1可能需要以频率漂移最小化由于改变在VCC供应电压如果R1需要它的价值一定要仔细选择-ED R1减小环路增益因此,如果R1是由太大的环路增益将大大降低,结晶不会振荡。如果R 1是由过小的正常变化在VCC可能导致振荡频率漂移出规格根据经验R1的值的第一条规则应等于该动态电阻5倍晶体20MHz的晶体的动态电阻,通常是在的10倍到30倍这个范围意味着一个合理的值对于R 1应在50X的范围-150X与否的决定,包括R1应基于晶振频率的测量偏差各电路参数是不同的根据IEEE 802标准的3整个振荡器电路(crytsal和放大器)必须精确到0.01 %当使用水晶X1引脚不能保证亲韦迪一个TTL兼容的逻辑输出和不应该使用驱动外部标准的逻辑。

振荡器模块操作

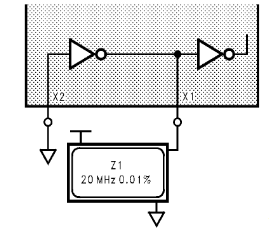

如果设计者希望使用一个晶体时钟振荡器1这提供了以下应采用

1、 TTL或CMOS输出一个0.01%频率公差

2、40%-60%的占空比

3、t2 TTL负载输出驱动器

功能说明

电路示于图2(附加输出可以驱动是必要的,如果振荡器也必须带动其他康波堂费)使用时钟振荡器仍建议设计者连接振荡器输出到X1引脚领带X2引脚到地3 3 Manchester编码和差分驱动器该编码器开始工作时,发送使能输入(TXE)变为高电平,并将其转换时钟和NRZ数据,以曼彻斯特数据的收发有关的持续时间TXE居高不下发送数据(TXD)的编码用于发射驱动器对(TXg) TXD必须在有效发送时钟(TXC)的上升沿发送结束当TXE变低,最后过渡始终是积极的它出现在比特单元的中心,如果最后一个比特是1还是在位单元的结束时,如果最后位是零差动发送对从所述次级的异的LATION变压器驱动器长达50米的双绞线??AUI电缆这些输出需要两个源极跟随器270X下拉电阻到地该DP83910A允许两个半工序和全步骤是以太网I和IEEE 802 3在SEL引脚兼容低(对于以太网I)发射a是相对于正发送b闲着SEL高时(对于IEEE 802 3)发送a和发送b是相等的,在空闲状态这提供零差分电压与变压操作呃耦合负载

曼彻斯特解码器

解码器包括一个差动接收器和一个PLL来的独立的曼彻斯特编码的数据流进入时钟显的NAL和NRZ数据的差分输入必须外部端的两个39X电阻串联连接,如果标准78X收发器引入光缆采用的是薄以太网网应用中,这些电阻器是可选的预防从错误触发,解码器静噪电路的噪音输入拒绝与小于电平的信号b175毫伏一旦输入超出了静噪要求载波感(CRS)有效接收数据(RXD)和接收时钟(RXC)生效通常在6位倍DP83910A可以容忍有点抖动高达18纳秒的接收数据解码器检测到一个帧结束时没有更多midbit转换被检测在一个半位倍的最后一位载波感测之后解除断言接收时钟保持活跃的五个位的时间后, CRS变低以保证接收到的DP8390网卡的定时

译者碰撞

当以太网收发器(DP8392 CTI)的检测colli-锡安它会产生一个10 MHz信号到差分碰撞输入(CDg)的DP83910A的。当这些投入是否变形tected活跃DP83910A转换的10 MHz信号到一个有效高电平为控制器的控制器使用这个信号打退堂鼓了其目前的传输和resched-ULE另一个碰撞差分输入端的相同的方式作为差分接收输入的静噪电路是也同样拒绝脉冲小于水平b175毫伏

环回功能

当环回输入(LBK)被置高DP83910A重定向其传送的数据返回到其重新人为对象的路径,此功能提供了一种方便的方法同时测试芯片和系统级诚信发射驱动器和接收输入电路是禁用环回模式

框图: