DF1706点击型号即可查看芯片规格书

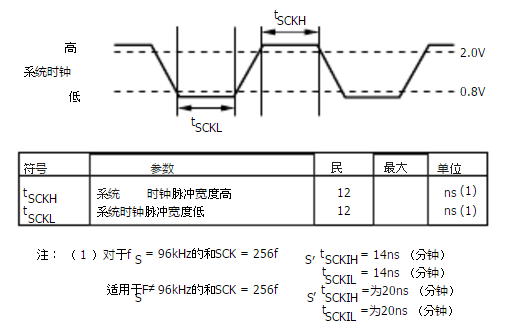

DF1706的系统时钟可以通过一个提供外部时钟信号在XTI (引脚6 ),或通过片上晶体振荡器。系统时钟速率必须运行在128FS, 192fS,256fS, 384fS, 512fS或768fS,其中fS是音频采样率。当128FS或192fS系统时钟被施加到DF1706 ,的DF1706的所述过采样率( OSR)数字滤波器应该是4倍,而不是8倍。该OSR可以通过x4的引脚(引脚21 )的硬件模式被选择在软件模式MODE 2寄存器或x4位。但是应当注意的是, 768fS系统时钟不能使用当fS比48kHz的大。无论128FS和192fS系统时钟可用于当fS比96kHz的大。此外,片上晶体振荡器被限制到最大频昆西24.0MHz的。表I示出了典型的系统时钟频率选择的采样率。该DF1706包括系统时钟检测电路,其确定系统时钟速率在使用中。该电路比较频率与LRCIN输入的系统时钟输入( XTI )率来确定系统时钟的倍频。理想情况下, LRCIN和BCKIN应该从系统时钟导出确保正确的同步。如果相位差BE-补间的系统时钟和LRCIN大于±4位时钟( BCKIN )期间,该系统的同步和LRCIN时钟将自动被DF1706进行。为系统时钟输入时序要求见图1。

图1

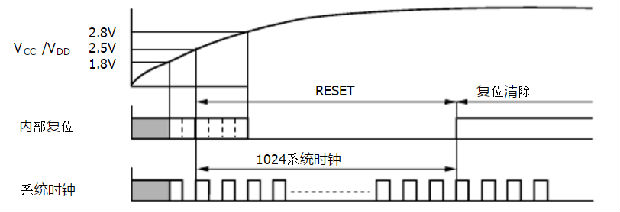

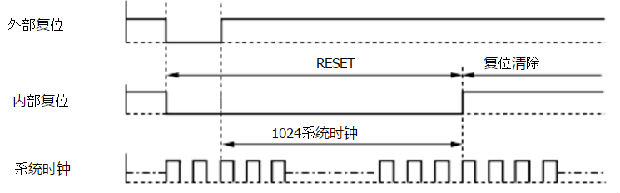

DF1706同时具有内部上电复位电路和复位引脚RST ( 14脚) ,用于提供一个外部复位信号。内部上电复位进行automati-当功率被施加到DF1706 ,如图2. RST引脚可以用于同步DF1706用一个系统复位信号,如图3 。在上电复位期间(1024个系统时钟),则BCKO , DOL和DOR的输出被强制拉低,WCKO的输出被强制为高。对于外部强制复位,BCKO , DOL和DOR的输出被强制为低和WCKO输出的初始化过程中强制为高周期(1024个系统时钟),则低到之后发生RST引脚的高电平跳变(见图3) 。

图2

图3

PCB布局指南

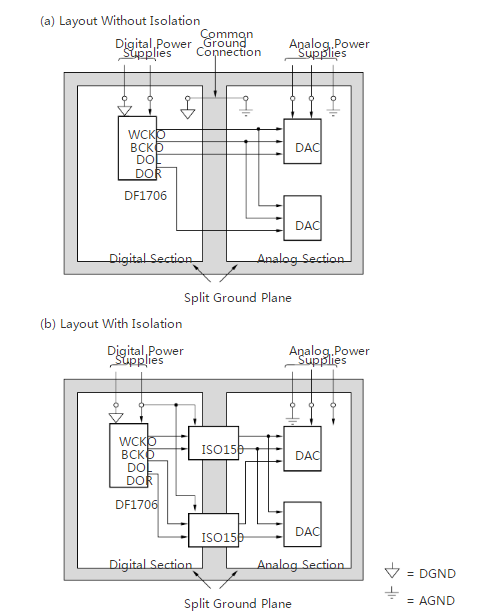

为了获得从DF1706指定性能和其相关联的D / A变换器,适当的印刷电路电路板布局是至关重要的。图4示出两种方法为获得最佳的音频性能。图4(a )示出了一个标准的,混合信号布局方案。该板被分成数字和模拟部分,每与自己的地面。地皮应放在一个分割平面,分离了路由和电源层。4DF1706和所有的数字电路应该被放置在数字部分,而音频D / A转换器(S)和模拟电路应位于过的模拟部分板。数字和模拟之间的常见的连接理由是必需的,是做在单个点处,如图所示。

对于图4 ( a)中,数字信号应该从路由DF1706到音频D / A采用短直接转换器( S)连接,以减少辐射高频量昆西能量。如果需要的话,串联电阻器可被放置在时钟和数据信号通路,以减少或消除任何过冲或下冲存在于这些信号。的值50Ω到100Ω ,建议作为起点,但设计师应该尝试以电阻值以获得最好的结果。图4( b)示出一种改进的方法,高性曼斯,混合信号电路板布局。此方法将数字该DF1706和音频D之隔离/ A转换器(多个) ,并提供了数字和之间的完全隔离电路板的模拟部分。在ISO150双数字耦合器提供出色的隔离和运行速度高达80Mbps的。

图4

电源和旁路

DF1706需要的操作+ 5V单电源供电化。该电源应该由一个10μF被绕过,0.1μF电容并联组合。该电容应被放置在尽可能靠近到VDD(引脚22)。铝电解或钽电容器可用于10μF值,而可以用于0.1μF的值陶瓷。

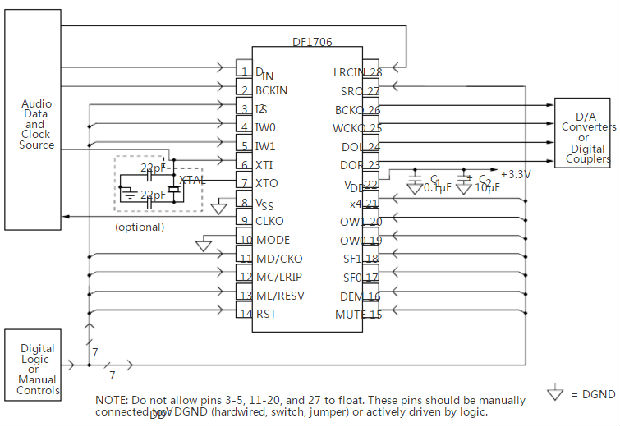

基本的电路连接

图5和6为基本电路的连接DF1706 。图5示出了用于设备模式连接控制,而软件如图6所示的连接模式控制。请注意,配售的C1和C2在这两个图中,因为它们在物理上是接近的DF1706 。

图5

图6