Z80180点击型号即可查看芯片规格书

特征

Z80180 微处理器单元(MPU)的主要功能包括:

•代码与Zilog Z80 CPU兼容®

•扩展指令

•两个DMA通道

•低功耗模式

•片内中断控制器

•三个片上等待状态发生器

•片内振荡器/发电机

•扩展的MMU寻址(高达1 MB)

•时钟串行I/O端口

•两个16位计数器/计时器

•两个UART

•时钟速度:6兆赫、8兆赫和10兆赫

•6兆赫版本支持6.144兆赫CPU时钟操作

•工作范围:5 V

•工作温度范围:0℃至+70℃。

•三种包装类型68针PLCC-

-64针DIP 80针QFP

一般说明

Z801808482;是一个8位MPU,它提供了降低系统成本的好处,还提供了与现有Zilog Z80设备的完全向后兼容性。

通过将多个关键系统功能与CPU结合,降低了系统成本。这些关键功能包括I/O设备,如DMA、UART和定时器通道。芯片上还包括等待状态发生器、时钟振荡器和中断控制器。

Z80180™封装在80针QFP、68针PLCC和64针DIP封装中。

注:所有具有上横线的信号都是低激活信号。例如,b/w,其中word为active low);b/w,其中byte为active low。

Pin描述

A0—A19。地址总线(输出,高有效,3状态)A–形成一个20位地址总线。地址总线为内存数据总线交换提供地址,高达1 MB,I/O数据总线交换提供地址,高达64 KB。地址总线在复位和外部总线确认循环期间进入高阻抗状态。地址行A18与可编程重新加载计时器(PRT)通道1(T,重置时选择作为地址输出)的输出多路复用,地址行A19在Z80180的DIP版本中不可用。019出

BasACK总线确认(输出,低激活)。Busack表示请求设备、MPU地址和数据总线,以及一些进入高阻抗状态的控制信号。

布雷克总线请求(输入,低激活)。外部设备(如DMA控制器)使用此输入请求访问

系统总线。此请求要求比NMI更高的优先级,并且总是在当前机器周期结束时被识别。此信号阻止CPU执行进一步的指令,并将地址和数据总线以及其他控制信号置于高阻抗状态。

CKA0,CKA1-异步时钟0和1(双向,高激活)。当处于输出模式时,这些引脚是发送和接收时钟。

来自ASCI波特率发生器的输出。在输入模式下,这些管脚用作ASCI波特率发生器的外部时钟输入。CKA0与DREQ0多路复用,

CKA1与TEND0多路复用。

CKS -串行时钟(双向,高激活)。这条线是CSIO通道的时钟。

时钟-系统时钟(输出,高激活)。输出用作MPU和外部系统的参考时钟。该输出的频率等于晶体或输入时钟频率的一半。

CTS0- CTS1-清除以发送0和1(输入,低激活)。这些线路是ASCI信道的调制解调器控制信号。CTS1与RXS多路复用。

D0- D7-数据总线(双向,高电平,3态)。D0–D7构成8位双向数据总线,用于传输

输入/输出和存储设备之间的信息。在复位和外部总线确认循环期间,数据总线进入高阻抗状态。

DCD0-数据载体检测0(输入,低激活)。ASCI信道0的可编程调制解调器控制信号。

DRYQ0,DRYQ1。DMA请求0和1(输入,低电平有效)。DREQ用于请求从芯片上的DMA信道之一进行DMA传输。DMA通道监视这些输入,以确定外部设备何时准备好进行读或写操作。这些输入可编程为水平或边缘感应。DREQ0与CKA0多路复用。

E-启用时钟(输出,高激活)。总线事务期间的同步机器周期时钟输出。

外-外部时钟晶体(输入,高激活)。晶体振荡器连接。当不使用晶体时,外部时钟可以输入到该管脚上的Z80180。此输入由施密特触发。

停止-停止/休眠(输出,低激活)。此输出在CPU执行halt或sleep指令后断言,并等待不可屏蔽或可屏蔽

操作恢复前中断。它还与M1和ST信号一起用于解码CPU机器周期的状态。

英特0-可屏蔽中断请求0(输入,低激活)。此信号由外部I/O设备生成。CPU在当前指令周期结束时将这些请求作为

只要NMI和BUSREQ信号处于非激活状态。CPU通过中断确认此中断请求

确认周期。在此循环中,M1和IORQ信号都变为激活状态。

It1,Int-可屏蔽中断请求1和2(输入,低电平有效)。此信号由外部I/O设备生成。CPU在当前指令周期结束时满足这些请求,只要NMI, 布雷克和英特0信号无效。CPU通过中断确认周期来确认这些请求。不同于英特0在这个循环中M1或IORQ信号激活。

IORQI/O请求(输出,低激活,3态)。IORQ表示地址总线连接-

为I/O读写操作提供有效的I/O地址。也会生成IORQ,

与M1一起,在确认INT0输入信号期间,指示-

中断响应向量可以放置在数据总线上。该信号类似于Z64180的IOE信号。

M1-机器循环1(输出,低激活)。一起MReq, M1指示当前循环是操作码获取循环和指令执行。一起IORQ, M1指示当前循环用于中断确认。它也用于停顿和装货单解码CPU机器周期状态的信号。此信号类似于激光雷达Z64180的信号。

MREQ-内存请求(输出,低激活,3态)。MREQ表示地址总线为内存读写操作保留有效地址。这个信号是

类似于Z64180的ME信号。

NMI-不可屏蔽中断(输入,触发负边缘)。NMI要求比国际的并且总是在指令结束时被识别,不管中断启用触发器的状态如何。此信号强制CPU在位置继续执行0.66 h.

RD-操作码重新初始化(输出,低激活,3态)。rd表示CPU想要从内存或I/O设备读取数据。寻址I/O或内存设备必须使用此信号将数据选通到CPU数据总线上。

RSF-刷新(输出,低激活)。与mreq一起,rfsh表示当前的CPU机器周期和地址总线的内容必须用于动态存储器的刷新。地址总线(A7–A10)的低阶8位包含刷新地址。

该信号类似于Z64180的参考信号。

RTS0-请求发送0(输出,低激活)。ASCI信道0的可编程调制解调器控制信号。

RXA0,RXA1-接收数据0和1(输入,高激活)。这些信号是到ASCI信道的接收数据。

RXS-时钟串行接收数据(输入,高激活)。这条线是CSIO通道的接收器数据。RXS与ASCI信道1的CTS1信号多路复用。

圣-状态(输出,高激活)。该信号与M1和HALT输出一起使用,以解码CPU机器周期的状态。

笔记:

X =保留。

mc=机器循环。

腱1传输端0和1(输出,低激活)。在DMA的最新写入周期内,此输出被断言为活动输出。

操作。它用于指示块传输的结束。tend0与

CKA1

试验-测试(输出,不是DIP版本)。此销用于测试,必须保持打开。

吹嘘-超时(输出,高激活)。T是来自PRT通道1的脉冲输出。这条线路与地址总线的A18多路复用。出

TXA0,TXA1-传输数据0和1(输出,高激活)。这些信号是来自ASCI信道的传输数据。传输数据的变化与传输时钟的下降沿有关。

TX--时钟串行传输数据(输出,高激活)。这条线路是从CSIO通道传输的数据。

等待-等待(输入,低激活)。等待向MPU指示地址存储器或

I/O设备没有准备好进行数据传输。该输入在t2的下降沿上采样(以及随后的等待状态)。如果输入采样率较低,则附加的等待状态为

插入,直到对等待输入进行高采样,此时继续执行。

WR-写入(输出,低激活,3态)。wr表示CPU数据总线将有效数据存储在地址I/O或内存位置。

XTAL晶体(输入,高激活)。晶体振荡器连接。如果使用外部时钟而不是晶体,则必须保持此针打开。振荡器输入不是TTL电平(见第21页的直流特性)。根据不同的情况,有几种销用于不同的情况。

多路管脚描述

多路管脚描述

销

描述

A18/T出

在复位过程中,此针脚初始化为A18针脚。如果定时器控制寄存器(TCR)的TOC1或TOC0位设置为1,则选择T功能。如果TOC1和TOC0清除为0,则选择A18功能。出

CKA0/DRYQ0

在复位过程中,该管脚初始化为CKA0管脚。如果dma模式寄存器(dmode)中的dm1或sm1设置为1,则始终选择dreq0函数。

CKA1/RAND0

在复位过程中,此插脚初始化为CKA1插脚。如果asci控制寄存器ch1(cntla1)中的cka1d位设置为1,则选择tend0功能。如果CKA1D位设置为0,则选择CKA1功能。

RXS/CTS1

在复位过程中,该管脚初始化为RXS管脚。如果asci状态寄存器ch1(stat1)中的cts1e位设置为1,则选择cts1功能。如果CTS1E位设置为0,则选择RXS函数。

建筑

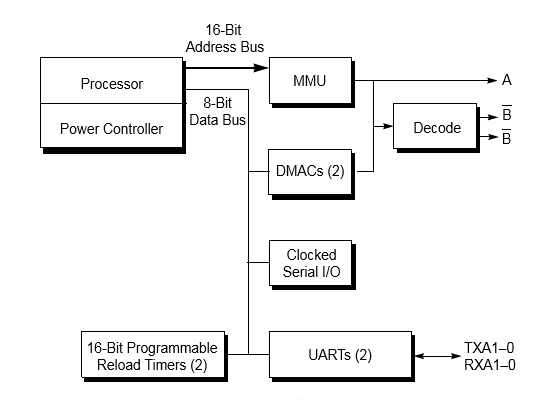

Z180结合了高性能CPU核心和多种®

系统和I/O资源在广泛的应用中很有用。CPU核心由五个功能块组成:时钟发生器、总线状态控制器、中断控制器、内存管理单元(MMU)和中央处理器(CPU)。集成的I/O资源构成了剩余的四个功能块:直接内存访问(DMA)控制(2个通道)、异步串行通信接口(ASCI)2个通道、可编程重新加载计时器(PRT)2个通道和时钟串行I/O(CSIO)通道。

时钟发生器-从外部晶体或时钟输入生成系统时钟。外部时钟分为两个或一个,并提供给内部和外部设备。

总线状态控制器-该逻辑执行与CPU和一些片上外围设备相关的所有状态和总线控制活动。包括等待状态定时、重置周期、DRAM刷新和DMA总线交换。

中断控制器-该逻辑监控和优先处理各种内部和外部中断和陷阱,以提供来自CPU的正确响应。为了保持与Z80 CPU的兼容性,支持三种不同的中断模式。®

内存管理单元-MMU允许您将CPU使用的内存(逻辑上只有64 KB)映射到z80180支持的1-MB寻址范围。MMU对象代码的组织允许维护与Z80 CPU的兼容性,同时提供对扩展内存空间的访问。该组织是通过使用有效的公共区域银行区域方案来实现的。

中央处理单元-CPU是微编码的,以提供与Z80 CPU兼容的对象代码核心。它还提供Z80指令集的超集,包括8位乘法。核心被修改为允许许多指令以更少的时钟周期执行。

DMA控制器-DMA控制器在内存和I/O设备之间提供高速传输。支持的传输操作有内存到内存、内存到/从I/O和I/O到I/O。支持的传输模式有请求、突发和周期窃取。DMA传输可以访问完整的1 MB地址范围,块长度可达64 KB,并且可以跨越64K的边界。

异步串行通信接口ASCI逻辑提供两个单独的全双工UART。每个通道包括可编程波特率发生器和调制解调器控制信号。ASCI通道还支持多处理器通信格式以及中断检测和生成。

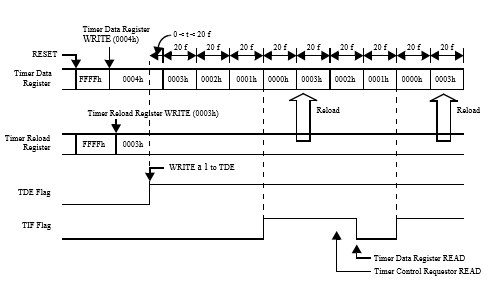

可编程重新加载计时器(PRT)该逻辑由两个独立的通道组成,每个通道包含一个16位计数器(计时器)和计数重新加载寄存器。计数器的时基是从到达计数器之前的系统时钟(除以20)得出的。PRT通道1提供可选输出,以允许波形生成。

定时器数据寄存器

定时器数据寄存器

时钟串行I/O(CSIO)。CSIO通道提供半双工串行发送器和接收器。该通道可用于与其他微处理器或微型计算机的简单高速数据连接。TRDR用于CSIO传输和接收。系统设计必须保证满足半双工操作的约束条件。发送和接收操作不能同时发生。例如,如果在CSIO接收数据时尝试CSIO传输,则CSIO不工作。

注:中继转发没有缓冲。正在尝试执行首席信息官在先前的传输数据仍被移出时传输,使移位数据立即

更新,破坏正在进行的传输操作。必须避免在传输或接收过程中读取trdr。

CSIO框图

运行模式

Z80与64180兼容®

Z80180是两个不同的祖先处理器的后代,Zilog的原始Z80和Hitachi 64180。操作模式

控制寄存器(OMCR),可编程为在某些Z80和64180差异之间进行选择。

-操作控制寄存器(OMCR:I/O地址=3eh)

M1E(M1启用)-该位控制M1输出,并在复位期间设置为1。

当m1e=1时,m1输出在操作码获取循环、int0确认循环和NMI确认的第一个机器循环期间被断言为低。

在Z80180上,这种选择使得处理器只获取一次RETI指令,当从零等待状态存储器获取RETI时,使用三个时钟机器周期,这不是完全Z80定时兼容,但与片上CTC兼容。

当m1e=0时,处理器在指令获取周期内不驱动m1低。在正常定时情况下,只获取一次RETI指令后,处理器返回并

使用包括驱动M1低的完全Z80兼容循环重新蚀刻指令。一些外部Z80外围设备可能需要正确解码的RETI指令。图9说明了当m1e=0时的reti序列。

MIE=0的RETI指令序列

M1TE(M1临时启用)-此位控制临时

M1信号的断言。它始终作为1读取,并在重置期间设置为1。

当m1e设置为0以适应某些外部z80外围设备时,这些相同的设备可能需要在对其某些寄存器编程后在m1上进行脉冲,以完成正在编程的功能。

例如,当控制字写入Z80 PIO以启用中断时,不启用

实际上发生在PIO识别出激活的M1信号之前。当m1te=1时,没有

M1信号的操作发生变化,M1E控制其功能。当m1te=0时,m1输出在下一个操作码获取周期内断言,而不管状态如何

编程到M1E位。这个实例只是暂时的(仅一次),不需要预先编程1来禁用该函数(参见图10)。

M1临时启用时间

国际奥委会该位控制IORQ和RD信号的定时。通过重置将其设置为1。什么时候?

IOC=1的I/O读写周期

当IOC=0时,IORQ和RD信号的时间与Z80的时间匹配。由于t2的上升沿,IORQ和RD信号变为激活状态(见图12)。

IOC=0的I/O读写周期

停机和低功率运行模式-Z80180可以在五种模式下运行,包括活动和功耗:

•正常运行

•停止模式

•iostop模式

•睡眠模式

•系统停止模式

正常运行-Z80180处理器正在获取并运行一个程序。全部启用

设备的功能和部分处于活动状态,停止销处于高位。

停机模式此模式由HALT指令进入。此后,Z80180处理器继续获取以下操作码,但不执行它,并驱动

停止,ST和M1销都低。振荡器和功率因数管脚保持激活状态,中断和总线授予外部主设备,DRAM刷新可能发生,所有片上I/O设备继续运行,包括DMA通道。

Z80180在响应低开启复位时离开停止模式,在来自

已启用片上源、NMI上的外部请求或INT0上的已启用外部请求,

It1或It2。在中断的情况下,返回地址是HALT指令之后的指令;此时,程序可以分支回HALT指令以等待另一个中断,或者可以检查系统/应用程序的新状态并做出适当的响应。

暂停计时

睡眠模式通过将CPU控制寄存器(CCR3、CCR6)的iostop位(ICR5)第3位和第6位全部置零并执行休眠指令,进入休眠模式。振荡器和功率因数输出继续工作,但被阻塞从CPU核心和DMA通道,以降低功耗。DRAM刷新停止,但可能发生中断并授予外部主机。除非总线被授予外部主机,

A19–0和除停机以外的所有控制信号均保持高位。停下是Low。除DMA通道外,I/O操作与休眠指令之前一样继续。

Z80180响应低启动重置而离开睡眠模式,并且

来自片上源的中断请求、NMI的外部请求或外部请求

在int0、int1或int2上。

如果一个中断源被单独禁用,它就不能使Z80180退出休眠模式。如果一个中断源是单独启用的,并且ief位是1,因此中断是全局启用的(由ei指令),则会发生最高优先级的活动中断,返回地址是sleep指令之后的指令。如果单独启用了中断源,但ief位为0,因此中断被全局禁用(通过DI指令),则z80180只需执行以下指令即可退出休眠模式。

这提供了一种与高速外部事件同步的技术,而不会引起中断响应序列所施加的延迟。由于中断请求而退出睡眠模式的时间。

注:Z80180需要大约1.5个时钟才能重新启动。

睡眠时间

停止模式通过将I/O控制寄存器(ICR)的iostop位设置为1进入iostop模式。在这种情况下,片上I/O(asci、csio、prt)停止工作。然而,CPU继续工作。从iostop模式恢复是通过将icr中的iostop位重置为0

系统停止模式-系统停止模式是睡眠和iostop模式的组合。通过将ICR中的iostop位设置为1,然后执行sleep指令,进入系统停止模式。在此模式下,片上I/O和CPU停止工作,降低功耗,但功率因数输出继续工作。从系统停止模式恢复与从睡眠模式恢复相同,只是内部I/O源(被i o stop禁用)无法生成恢复中断。

标准试验条件

直流特性部分适用于以下标准试验条件,除非另有说明。所有电压均参考GND(0 V)。正电流流入参考管脚。

所有交流参数假设负载电容为100 pF。每增加50 pf负载,增加10 ns延迟,数据总线最大为200 pf,地址和控制线最大为100 pf。交流定时测量参考1.5伏(时钟除外,时钟参考10%和90%点)。