AD9200点击型号即可查看芯片规格书

AD9200是单芯片,单电源,10位,20 MSPS具有片上采样保持功能的模数转换器放大器和电压参考。AD9200使用多级差分流水线架构,20 MSPS数据速率和保证在整个工作温度下没有丢失代码范围。

AD9200的输入设计用于简化成像和通信系统的开发。用户可以选择各种输入范围和偏移,并可以驱动输入是单端还是差分输入。采样保持(SHA)放大器同样适用于两者多路复用系统,可切换连续通道中的满量程电压电平,并以高达奈奎斯特速率和超过奈奎斯特速率的频率对单通道输入进行采样。交流耦合输入信号可以通过板载转换到预定的水平钳位电路(AD9200ARS,AD9200KST)。动态性能非常出色。

AD9200具有板载可编程基准电压源。一个也可以选择外部参考以适应直流精度和温度漂移要求的应用。单个时钟输入用于控制所有内部转换周期。数字输出数据以直接二进制形式呈现输出格式。超出范围信号(OTR)表示可以与最高有效位一起使用的溢出条件确定低或高溢出。

应用

AD9200的工作电压范围为2.7 V至5.5 V,非常适合高速低功率运行便携式应用。

AD9200工业规范(-40°C至+ 85°C)和商用(0°C至+ 70°C)温度范围。

产品亮点

低电量

AD9200采用3 V电源时功耗为80 mW(不包括参考力量)。在睡眠模式下,功率降低到以下

5 mW。非常小的包装

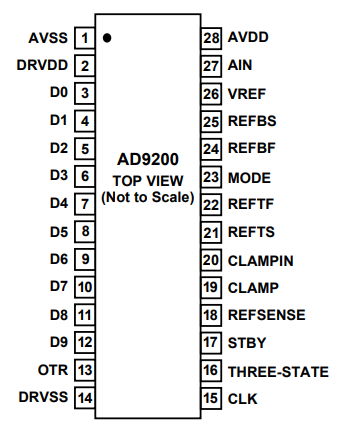

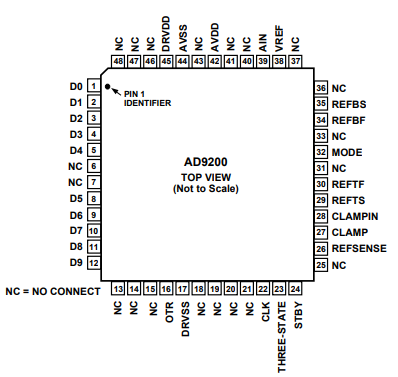

AD9200采用28引脚SSOP和48引脚LQFP包。引脚与AD876兼容

AD9200与AD876引脚兼容,允许使用较旧版本设计转移到更低的电源电压。300 MHz板载采样保持多功能SHA输入可配置为单端或差分输入。

超出范围的指标OTR输出位指示输入信号何时超出AD9200的输入范围。

内置钳位功能允许使用AD9200ARS和DC92直接恢复视频信号AD9200KST

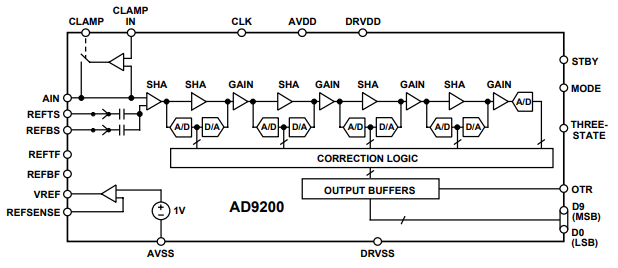

功能框图

AD9200规格(AVDD = + 3 V,DRVDD = +3 V,FS = 20 MHz(占空比50%),MODE = AVDD,2 V输入除非另有说明,否则范围为0.5 V至2.5 V,外部参考电压,TMIN至TMAX。

参数符号最小值典型最大单位条件

第10号决议

转换率FS 20 MHz

直流精度

差分非线性DNL±0.5±1 LSB REFTS = 2.5 V,REFBS = 0.5 V.

积分非线性INL±0.75±2 LSB

偏移误差EZS 0.4 1.2%FSR

增益误差EFS 1.4 3.5%FSR

参考电压

最高参考电压REFTS 1 AVDD V.

底部参考电压REFBS GND AVDD - 1 V.

差分参考电压2 V p-p

参考输入电阻110kΩREFTS,REFBS:MODE = AVDD

在REFTF和REFBF之间4.2kΩ:MODE = AVSS

模拟输入

输入电压范围AIN REFBS REFTS V REFBS Min = GND:REFTS Max = AVDD

输入电容CIN 1 pF切换

光圈延迟tAP 4 ns

孔径不确定性(抖动)tAJ 2 ps

输入带宽(-3 dB)BW

全功率(0 dB)300 MHz

直流泄漏电流23μA输入=±FS

内部参考

输出电压(1 V模式)VREF 1 V REFSENSE = VREF

输出电压容差(1 V模式)±10±25 mV

输出电压(2 V模式)VREF 2 V REFSENSE = GND

负载调节(1 V模式)0.5 2 mV 1 mA负载电流

电源

工作电压AVDD 2.7 3 5.5 V.

DRVDD 2.7 3 5.5 V

电源电流IAVDD 26.6 33.3 mA AVDD = 3 V,MODE = AVSS

功耗PD 80 100 mW AVDD = DRVDD = 3 V,MODE = AVSS

掉电4 mW STBY = AVDD,MODE和CLOCK =

AVSS

增益误差电源抑制PSRR 1%FS

动态性能(AIN = 0.5 dBFS)

信噪比和失真SINAD

f = 3.58 MHz 54.5 57 dB

f = 10 MHz 54 dB

有效的比特

f = 3.58 MHz 9.1位

f = 10 MHz 8.6位

信噪比SNR

f = 3.58 MHz 55 57 dB

f = 10 MHz 56 dB

总谐波失真THD

f = 3.58 MHz -59 -66 dB

f = 10 MHz -58 dB

无杂散动态范围SFDR

f = 3.58 MHz -61 -69 dB

f = 10 MHz -61 dB

双音互调

失真IMD 68 dB f = 44.49 MHz和45.52 MHz

差分相位DP 0.1度NTSC 40 IRE Mod斜坡

差分增益DG 0.05%

PIN配置

28引脚收缩小外形(SSOP)图

48引脚塑料薄型四方扁平封装(LQFP)图

规格的定义

积分非线性(INL)

积分非线性是指每个人的偏差从“零”到“满量程”的线条代码。该用作“零”的点在第一次代码转换之前发生1/2 LSB。 “满量程”定义为超过最后一级的1 1/2 LSB代码转换。偏差是从中心测量的每个特定代码到真正的直线。

微分非线性(DNL,无缺失代码)理想的ADC具有恰好1 LSB的代码转换分开。DNL是与该理想值的偏差。经常这样根据没有遗漏码的决议规定(NMC)有保证。

偏移误差

第一次转换应发生在高于“零”的1 LSB级别。

偏移量定义为实际第一个代码转换与该点的偏差。增益错误对于模拟值1 LSB,应进行第一次代码转换高于标称负满量程。最后的过渡应该发生模拟值低于标称正满1 LSB规模。增益误差是第一次和最后一次代码转换之间的实际差异与理想差异的偏差在第一个和最后一个代码转换之间。管道延迟(延迟)转换启动和转换之间的时钟周期数

相关的输出数据可用。新产出每个上升沿提供数据。

运作理论

AD9200采用流水线式多级架构以低功率实现高采样率。AD9200将转换分配到几个较小的A / D子块上进行精炼转换时,精度逐渐提高从阶段到阶段的结果。作为分布式转换的结果,AD9200只需要一小部分1023比较器用于传统闪光型A / D.一个每个阶段内的采样保持功能允许第一阶段操作新的输入样本,而第二阶段,第三和第四阶段对前三个样本进行操作。

运作模式

AD9200旨在实现最佳性能各种各样的成像,通信和仪器仪表应用,包括引脚与AD876 A / D的兼容性。为了实现这种灵活性,AD9200的内部开关是用于将电路重新配置为不同的模式。这些模式通过适当的针扎带选择。有三个部分受此模态影响的电路:电压参考,电压参考缓冲区和模拟输入。应用程序的性质将决定哪种模式是合适的:以下各节中的描述以及表I应该如此协助选择所需的模式。